ВМЯп

-

FPGAВМЯпгЕШћжївЊдвђМАНтОіЗНЗЈ

дкFPGAПЊЗЂЩшМЦжаЃЌЮвУЧПЩФмЛсОРњгЩгкзЪдДеМгУЙ§ИпЕФЧщПіЃЌР§ШчBRAMЁЂLUTКЭURAMЕШЙиМќзЪдДРћгУТЪДяЕНЛђГЌЙ§80ЃЅЃЌДЫЪБГіЯжЪБађЮЅР§ЪЧГЃгаЕФЪТЃЌЩѕжСгЩгкгЕШћЕМжТВМЯпЪЇАмЃЌећИіFPGAЙЄГЬУцСйЮоЗЈЩњГЩbitЮФМўЕФЮЃЯе

-

вЛЮФЯъНтПЊЙиЕчдДВМЯпзЂвтЪТЯю

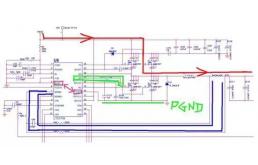

ЮФ | аЄгТГЌ вЛВЉПЦММИпЫйЯШЩњЭХЖгЖгдБЩЯЦкЮвУЧЬИЕНСЫВМОжЗНУцЕФзЂвтЪТЯю,Ждгкlayout ЙЄГЬЪІРДЫЕЕчдДФЃПщВМОжЭъГЩЪБ,ВМЯпвВОЭЛљБОвбОЙцЛЎКУ,ВМОжзіКУ,ВМЯпздШЛЫЎЕНЧўГЩЁЃШчЯТЭМ1ЫљЪОд

-

FLY-BYЁЊДјФуСЫНтСНДѓВМЯпЯИНк

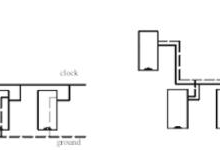

ЮФ | дЌВЈ зїепЬ§Й§етбљвЛжжЫЕЗЈ,DDRЕФРњЪЗ,ОЭЪЧвЛИіSIММЪѕБфИяЕФЙ§ГЬ,ЫЕАзСЫОЭЪЧЭиЦЫгыЖЫНгжЎељЁЃDDR2ЪЙгУЕФЪЧTЭиЦЫ,ЗЂеЙЕНDDR3,в§ШыСЫШЋаТЕФОеЛЈСДЁЊfly-byНсЙЙ

-

?AD PCB2АхЦРЩѓЃКВМОжЮЪЬтМАВМЯпЮЪЬт

вЛЃЎВМОжЮЪЬтЃК1ЃЎЁОЮЪЬтЗжЮіЁПЃКLEDЕЦУЛгаЖдЦыЁЃ ЁОЮЪЬтИФЩЦНЈвщЁПЃКНЈвщЪЧНЋдЊЦїМўНјааЖЅЕзЖдЦыЛђепжааФЖдЦыЃЌдіЧПвЛЖЈЕФЩшМЦаЇЙћЁЃЖўЃЎВМЯпЮЪЬтЃК1ЃЎЁОЮЪЬтЗжЮіЁПЃКаХКХЯпДђПзЮЛжУОрРыЖдгІЙмНХНЯдЖ

-

ЁОPCBММЧЩЁПЯрЭЌФЃПщВМОжВМЯпЕФЗНЗЈ

КмЖрPCBЩшМЦАхПЈжаДцдкЯрЭЌФЃПщЃЌИјШЫећЦыЁЂУРЙлЕФИаОѕЁЃДгЩшМЦЕФНЧЖШРДНВЃЌећЦыЛЎвЛЃЌВЛЕЋПЩвдМѕЩйЩшМЦЕФЙЄзїСПЃЌЛЙБЃжЄСЫЯЕЭГадФмЕФвЛжТадЃЌЗНБуМьВщгыЮЌЛЄЁЃЯрЭЌФЃПщЕФВМОжВМЯпДцдкЦфКЯРэадКЭБивЊадЁЃ

-

EMCРэТлЩЯЕФВюФЃЕчСїгыЙВФЃЕчСї&PCBВМОжВМЯпЫМТЗЃЁ

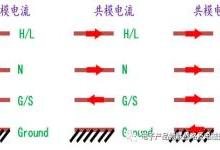

гЩгкМЏГЩЕчТЗММЪѕЕФЗЩЫйЗЂеЙЃЌЦфЫйЖШЃЌЙцФЃКЭЙІФмВЛЖЯРЉДѓЃЎЫцзХжїЦЕЕФЬсИпЃЌВМЯпУмЖШЕФдіМгвдМАДѓСПЪ§ФЃЛьКЯЕчТЗЕФгІгУЃЌЖдвдЪБжгЮЊДњБэЕФИпЫйЕчТЗЩшМЦЕФвЊЧѓдНРДдНИпЁЃ

-

ММЪѕЗжЯэЃКЪЎеаИуЖЈФеШЫЕФИпЦЕЕчТЗВМЯп

ШчЙћЪ§зжТпМЕчТЗЕФЦЕТЪДяЕНЛђепГЌЙ§45MHZЁЋ50MHZЃЌЖјЧвЙЄзїдкетИіЦЕТЪжЎЩЯЕФЕчТЗвбОеМЕНСЫећИіЕчзгЯЕЭГвЛЖЈЕФЗнСПЃЈБШШчЫЕ1ЃЏ3ЃЉЃЌЭЈГЃОЭГЦЮЊИпЦЕЕчТЗЁЃИпЦЕЕчТЗЩшМЦЪЧвЛИіЗЧГЃИДдгЕФЩшМЦЙ§ГЬЃЌЦфВМЯпЖдећИіЩшМЦжСЙиживЊЃЁ

ИпЦЕЕчТЗВМЯп 2018-12-25 -

еЧзЫЪЦЃЁЪЕР§ЯъНтМгЫйКЭИФНјPCBВМЯпЕФЗНЗЈ

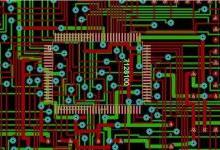

PCBВМЯпЗНЗЈдкВЛЖЯНјВНЃЌСщЛюЕФВМЯпММЪѕПЩвдЫѕЖЬЕМЯпГЄЖШЃЌЪЭЗХИќЖрЕФPCBПеМфЁЃДЋЭГPCBВМЯпЪмЕНЕМЯпзјБъЙЬЖЈКЭШБЩйШЮвтНЧЖШЕМЯпЕФЯожЦЁЃШЅГ§етаЉЯожЦПЩвдЯджјИФЩЦВМЯпЕФжЪСПЁЃ

-

PCBВМОжВМЯпЙцдђ

PCBВМОжгІОЁСПТњзувдЯТвЊЧѓЃКзмЕФСЌЯпОЁПЩФмЖЬЃЌЙиМќаХКХЯпзюЖЬЃЛИпЕчбЙЁЂДѓЕчСїаХКХгыаЁЕчСїЃЌЕЭЕчбЙЕФШѕаХКХЭъШЋЗжПЊЃЛФЃФтаХКХгыЪ§зжаХКХЗжПЊЃЛИпЦЕаХКХгыЕЭЦЕаХКХЗжПЊЃЛИпЦЕдЊЦїМўЕФМфИєвЊГфЗжЁЃ

-

ЕчзгВњЦЗЃКPCBВМОжВМЯпЕФёюКЯEMIТЗОЖЗжЮі

ЮвУЧдкНјааЕчзгВњЦЗЛђЩшБИНјааEMIЗжЮіЪБЯШвЊЗжЮіЯЕЭГЕФИЩШХЕФДЋВЅТЗОЖЃЛШчЙћдкЮвУЧВњЦЗЩшМЦВтЪдЪБГіЯжГЌБъЕФЧщПіЃЌШчЙћЮвУЧФмЭЈЙ§ЗжЮіТЗОЖЛђепжЊЕРИЩШХдДЕФТЗОЖЖдНтОіЮЪЬтОЭБфЕУЧсЫЩЃЁ

зюаТЛюЖЏИќЖр >

-

11дТЦ№СЂМДБЈУћ>> ЙтЕчРрзЈвЕ2025ФъЧяМОПежаЫЋбЁЛс

-

11дТ28ШеСЂМДБЈУћ>>> 2024ЙЄГЬЪІЯЕСаЁЊЙЄвЕЕчзгММЪѕдкЯпЛсвщ

-

11дТ29ШеСЂМДдЄдМ>> ЁОЩЯКЃЯпЯТЁПЩшМЦЃЌвзШчЗДеЦЁЊCreo 11ЗЂВМбВеЙ

-

МДШе-11.30УтЗбдЄдМЩъЧы>>> ьнЪЏММЪѕ-КьЭтШШГЩЯёЯЕСаВњЦЗЪдгУЛюЖЏ

-

11дТ30ШеСЂМДЪдгУ>> ЁОгаНБЪдгУЁПАЎЕТПЫIDEC-ОХДѓЭѕХЦАВШЋВњЦЗ

-

МДШе-12.5СЂМДЙлПД>> ЫЩЯТаТФмдДжаЙњВМОжЃКяЎвЛДЮЕчГиаТЦЗНщЩм

- ГЬађЙЄГЬЪІ ЙуЖЋРћдЊКржЧФмзАБИЙЩЗнгаЯоЙЋЫО

- ЧЖШыЪНгВМўЙЄГЬЪІ ЩюлкЛЊЩљвНСЦММЪѕЙЩЗнгаЯоЙЋЫО

- ЪлКѓЗўЮёдБ ГЩЖМЪагЅХЕЪЕвЕгаЯоЙЋЫО

- ЯњЪлЙЄГЬЪІ еуНШШДЬМЄЙтММЪѕгаЯоЙЋЫО

- ББЧјЯњЪлЙЄГЬЪІ ЫежнБДСжМЄЙтгаЯоЙЋЫО

- ЯЕЭГЙЄГЬЪІЃЈ2025НьЃЉ ЩюлкЪадННЎПЦММЙЩЗнгаЯоЙЋЫО

- КЃЭтЯњЪл ЙуЖЋМЮЬкЛњЦїШЫздЖЏЛЏгаЯоЙЋЫО

- mesЙЄГЬЪІ АЌЕТПЫЫЙЕчзгЃЈФЯОЉЃЉгаЯоЙЋЫО