硬见小百科:单片机中断系统

单片机中断系统的概念

什么是中断,我们从一个生活中的例程引入。

你正在家中看书,突然电话铃响了,你放下书本,去接电话,和来电话的人交谈,然后放下电话,回来继续看你的书。这就是生活中的“中断”的现象,就是正常的工作过程被外部的事件打断了。仔细研究一下生活中的中断,对于我们学习单片机的中断也很有好处。

第一、什么可经引起中断。生活中很多事件能引起中断:有人按了门铃了,电话铃响了,你的闹钟闹响了,你烧的水开了…等等诸如此类的事件,我们把能引起中断的称之为中断源。单片机中也有一些能引起中断的事件,8031中一共有5个:两个外部中断,两个计数/定时器中断,一个串行口中断。

第二、中断的嵌套与优先级处理。设想一下,我们正在看书,电话铃响了,同时又有人按了门铃,你该先做那样呢?如果你正是在等一个很重要的电话,你一般不会去理会门铃的,而反之,你正在等一个重要的客人,则可能就不会去理会电话了。如果不是这两者(即不等电话,也不是等人上门),你可能会按你常常的习惯去处理。总之这里存在一个优先级的问题,单片机中也是如此,也有优先级的问题。优先级的问题不仅仅发生在两个中断同时产生的情况,也发生在一个中断已产生,又有一个中断产生的情况,比如你正接电话,有人按门铃的情况,或你正开门与人交谈,又有电话响了情况。考虑一下我们会怎么办吧。

第三、中断的响应过程。当有事件产生,进入中断之前我们必须先记住现在看书的第几页了,或拿一个书签放在当前页的位置,然后去处理不一样的事情(因为处理完了,我们还要回来继续看书):电话铃响我们要到放电话的地方去,门铃响我们要到门那边去,也说是不一样的中断,我们要在不一样的地点处理,而这个地点常常还是固定的。计算机中也是采用的这种办法,五个中断源,每个中断产生后都到一个固定的地方去找处理这个中断的程序,当然在去之前首先要保存下面将执行的指令的地址,以便处理完中断后回到原来的地方继续往下执行程序。具体地说,中断响应能分为以下几个步骤:1、保护断点,即保存下一将要执行的指令的地址,就是把这个地址送入堆栈。2、寻找中断入口,根据5个不一样的中断源所产生的中断,查找5个不一样的入口地址。以上工作是由计算机自动完成的,与编程者无关。在这5个入口地址处存放有中断处理程序(这是程序编写时放在那儿的,如果没把中断程序放在那儿,就错了,中断程序就不能被执行到)。3、执行中断处理程序。4、中断返回:执行完中断指令后,就从中断处返回到主程序,继续执行。

MCS-51单片机中断系统的结构

5个中断源的符号、名称及产生的条件如下。

INT0:外部中断0,由P3.2端口线引入,低电平或下跳沿引起。

INT1:外部中断1,由P3.3端口线引入,低电平或下跳沿引起。

T0:定时器/计数器0中断,由T0计满回零引起。

T1:定时器/计数器l中断,由T1计满回零引起。

TI/RI:串行I/O中断,串行端口完成一帧字符发送/接收后引起。

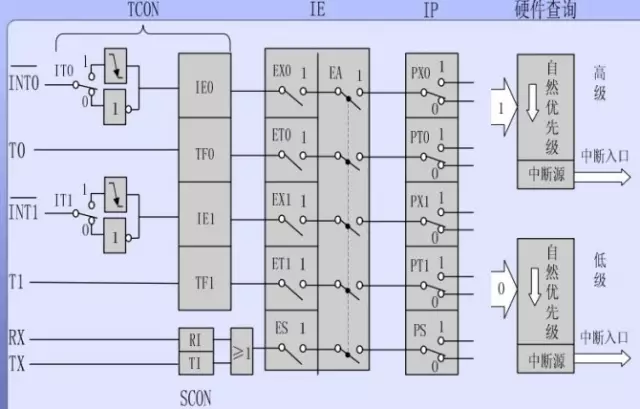

整个中断系统的结构框图见下图所示。

如图所示,由与中断有关的特殊功能寄存器、中断入口、次序查询逻辑电路等组成,包括5个中断请求源,4个用于中断控制的寄存器IE、IP、ECON和SCON来控制中断类弄、中断的开、关和各种中断源的优先级确定。

中断请求源

(1)外部中断请求源:

即外中断0和1,经由外部管脚引入的,在单片机上有两个管脚,名称为INT0、INT1,也就是P3.2、P3.3这两个管脚。在内部的TCON中有四位是与外中断有关的。

IT0:INT0触发方式控制位,可由软件进和置位和复位,IT0=0,INT0为低电平触发方式,IT0=1,INT0为负跳变触发方式。这两种方式的差异将在以后再谈。

IE0:INT0中断请求标志位。当有外部的中断请求时,这位就会置1(这由硬件来完成),在CPU响应中断后,由硬件将IE0清0。

IT1、IE1的用途和IT0、IE0相同。

(2)内部中断请求源TF0:

定时器T0的溢出中断标记,当T0计数产生溢出时,由硬件置位TF0。当CPU响应中断后,再由硬件将TF0清0。

TF1:与TF0类似。

TI、RI:串行口发送、接收中断,在串行口中再讲解。

中断允许寄存器IE在MCS-51中断系统中,中断的允许或禁止是由片内可进行位寻址的8位中断允许寄存器IE来控制的。

中断系统的控制寄存器

中断系统有两个控制寄存器IE和IP,它们分别用来设定各个中断源的打开/关闭和中断优先级。此外,在TCON中另有4位用于选择引起外部中断的条件并作为标志位。

1.中断允许寄存器--IE

IE在特殊功能寄存器中,字节地址为A8H,位地址(由低位到高位)分别是A8H-AFH。

IE用来打开或关断各中断源的中断请求,基本格式如下图1所示:

图1

EA:全局中断允许位。EA=0,关闭全部中断;EA=1,打开全局中断控制,在此条件下,由各个中断控制位确定相应中断的打开或关闭。

×:无效位。

ES:串行I/O中断允许位。ES=1,打开串行I/O中断;ES=0,关闭串行I/O中断。

ETl:定时器/计数器1中断允许位。ETl=1,打开T1中断;ETl=O,关闭T1中断。

EXl:外部中断l中断允许位。EXl=1,打开INT1;EXl=0,关闭INT1。

ET0:定时器/计数器0中断允许位。ET0=1,打开T0中断;ET0=0,关闭TO中断。

EXO:外部中断0中断允许位。Ex0=1,打开INT0;EX0=0,关闭INT0.

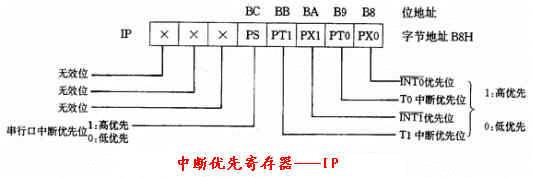

2、中断优先寄存器--IP

IP在特殊功能寄存器中,字节地址为B8H,位地址(由低位到高位)分别是B8H一BFH,IP用来设定各个中断源属于两级中断中的哪一级,IP的基本格式如下图2所示:

图2

×:无效位。

PS:串行I/O中断优先级控制位。PS=1,高优先级;PS=0,低优先级。

PTl:定时器/计数器1中断优先级控制位。PTl=1,高优先级;PTl=0,低优先级。

Pxl:外部中断1中断优先级控制位。Pxl=1,高优先级;PXl=O,低优先级。

PT0:定时器/计数器o中断优先级控制位。PT0=1,高优先级;PTO=0,低优先级。

Px0:外部中断0中断优先级控制位。Px0=1,高优先级;Px0=0,伤优先级。

在MCS-51单片机系列中,高级中断能够打断低级中断以形成中断嵌套;同级中断之间,或低级对高级中断则不能形成中断嵌套。若几个同级中断同时向CPU请求中断响应,则CPU按如下顺序确定响应的先后顺序:

INT0一T0---INT1一T1一RI/T1.

以上所有信息仅作为学习交流使用,不作为任何学习和商业标准。若您对文中任何信息有异议,欢迎随时提出,谢谢!

关于云创硬见

云创硬见是国内最具特色的电子工程师社区,融合了行业资讯、社群互动、培训学习、活动交流、设计与制造分包等服务,以开放式硬件创新技术交流和培训服务为核心,连接了超过30万工程师和产业链上下游企业,聚焦电子行业的科技创新,聚合最值得关注的产业链资源, 致力于为百万工程师和创新创业型企业打造一站式公共设计与制造服务平台。

图片新闻

技术文库

最新活动更多

-

即日-12.26立即报名>>> 【在线会议】村田用于AR/VR设计开发解决方案

-

1月8日火热报名中>> Allegro助力汽车电气化和底盘解决方案优化在线研讨会

-

1月9日立即预约>>> 【直播】ADI电能计量方案:新一代直流表、EV充电器和S级电能表

-

即日-1.14火热报名中>> OFweek2025中国智造CIO在线峰会

-

即日-1.20限时下载>>> 爱德克(IDEC)设备及工业现场安全解决方案

-

即日-1.24立即参与>>> 【限时免费】安森美:Treo 平台带来出色的精密模拟

推荐专题

分享

分享

发表评论

请输入评论内容...

请输入评论/评论长度6~500个字

暂无评论

暂无评论