无法启动!这个原理图出错的水平怎么样?

作者:黄刚

众所周知,原理图是整个设计流程的前端,关系到后面的PCB设计、加工、焊接、整板功能的调试是否成功。如果原理图出错导致调试失败的水平也分段位的话,大家说说看本文的这个案例的出错水平属于哪个段位呢?

这又是一个关于DDR系统的故事。高速先生这几年深耕在DDR仿真设计这个领域中,基本上经过我们仿真设计的各种DDR系统都很少出现功能的问题了。但是与此同时,DDR设计的难度的确是逐年增加的,单通道容量越来越大,密度越来越高,层数越来越少,速率越来越高,因此高速先生能看到我们有些客户们的DDR设计稍显吃力,然后出现问题的几率也慢慢增加。我们在最近的文章中也给大家分享了一些fail的例子,那么今天再给大家分享一个由于原理图问题导致的fail案例哈。

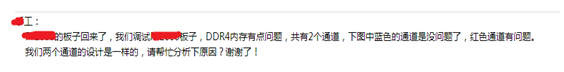

这又是另外一个略带点困意的午后,高速先生刚投入到下午的工作,突然就收到了一封醒神的邮件:

高速先生看到这封简单而有力的邮件,的确shock到了我们,两组基本一样的设计居然一组能成功运行到额定的速率,另外一组居然连启动都启动不了!!!差别之大,可能是高速先生前所未见的。一般来说,同一个板的几个DDR通道,最多会出现降频能运行的差别,像这样的差别真的只能用以下的词语来形容了。

但是震惊归震惊,分析还是要去分析的,PCB是我司进行设计和加工的,但是并没有进行仿真,因此板子的设计到加工整个流程都并没有经过高速先生的检阅。因此高速先生看到板子的时候,基本上就和你们看到板子是同一个时候了。我们看看其中一路DDR的拓扑,发现还是一个比较有难度的设计,一个通道10个颗粒,1拖10的拓扑,采用正反贴的结构进行布局。

从布局到布线来看,我们设计工程师的水平还是可以信赖的,高速先生会经常在内部去一起讨论DDR设计的细节方法,因此高速先生是相信我们设计团队能力的,从本案例也可以看到,这个1拖10难度的DDR系统至少有一个通道是成功跑到了额定速率。

高速先生隐隐的感觉到这么大的调试差别,在PCB设计上应该在某些地方有明显的区别,可能是乍眼一看没发现吧,因此高速先生一边在仔细检阅PCB设计文件,一边还是去指导客户去做一些debug的调试,例如让客户换一下驱动和ODT的配置,改变一下Vref电压幅度,甚至让客户只焊正面,去掉背面5个颗粒这种操作,但是很遗憾的事,客户尝试之后并没有任何的改善和变化。

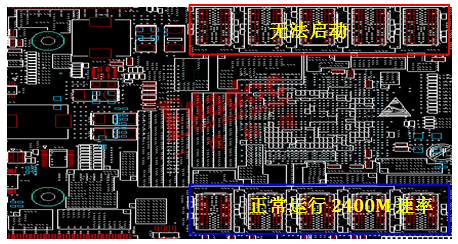

正当debug调试陷入僵局的时候,也不知道是不是看PCB文件看到眼花了,隐约发现两个通道在端接VTT电阻的数量上好像不太一样??!!!

赶紧猛的揉揉眼睛并而喝口水稳定下情绪,然后再认真的看一次!!!

这下看清楚了,还真是数量不一样的,上面有问题的通道明显少了一列VTT电阻,我们赶紧仔细检查每一根地址控制信号,看看是不是他们在VTT电阻上有差别。

不检查还好,一检查不得了!居然有问题的通道有三根信号就没连接到VTT电阻,也就是说,这三根信号压根就没有端接!

分析到这里,高速先生大概知道问题出在哪里了,在进行仿真来对比有VTT电阻端接和没有端接的波形之前,我们还想搞清楚到底为什么PCB设计上会漏掉这几根信号的端接。因此和我们PCB设计工程师确认后,我们要到了客户的设计原理图,找到相应的位置,果然有了惊人的发现。

我们找到了部分网表的对比,惊人的发现有问题的通道从客户的原理图上就已经漏了这几根信号的端接,然后我们这边工程师按照原理图完成了设计,加工和焊接,板子出来的结果就是这样了。

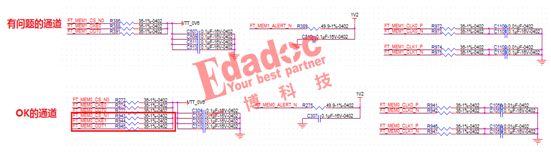

好吧,其实问题已经弄清楚了,最后我们再通过仿真来证明下有接端接和没接端接情况下,信号质量到底能有多大的差异。

经过仿真后,波形结果的确也能很好的和测试情况相对应。

这种没端接的情况,不要说2400M速率跑不上去,哪怕是降一半频率,1200M也是妥妥的…有问题!

最后我们的PCB工程师也找到了这个原理图的问题,并而把高速先生的结论告诉了客户。

最后高速先生以一句很无奈的话结束了这个项目的debug。

这个时候,希望高速先生快速定位到问题会给客户带来一丝丝安慰和后续能快速的进行改板,这个原理图出错导致加工出来的DDR系统完全不能启动的案例,希望能给大家在方案设计上有所思考哈。

图片新闻

技术文库

最新活动更多

-

1月8日火热报名中>> Allegro助力汽车电气化和底盘解决方案优化在线研讨会

-

1月9日立即预约>>> 【直播】ADI电能计量方案:新一代直流表、EV充电器和S级电能表

-

即日-1.16立即报名>>> 【在线会议】ImSym 开启全流程成像仿真时代

-

即日-1.20限时下载>>> 爱德克(IDEC)设备及工业现场安全解决方案

-

即日-1.24立即参与>>> 【限时免费】安森美:Treo 平台带来出色的精密模拟

-

即日-1.31立即参与>>> 【限时免费下载】村田白皮书

推荐专题

分享

分享

发表评论

请输入评论内容...

请输入评论/评论长度6~500个字

暂无评论

暂无评论