SAR ADC的隔离

作者:Wilfried Platzer,ADI公司应用工程师

问题:

如何为ADC增加隔离而不损害其性能?

(企业供图,下同)

答案:

对于隔离式高性能ADC,一方面要注意隔离时钟,另一方面要注意隔离电源。

SAR ADC传统上被用于较低采样速率和较低分辨率的应用。如今已有1 MSPS采样速率的快速、高精度、20位SAR ADC,例如LTC2378-20 ,以及具有32位分辨率的过采样SAR ADC,例如LTC2500-32。将ADC用于高性能设计时,整个信号链都需要非常低的噪声。当信号链需要额外的隔离时,性能会受到影响。

关于隔离,有三方面需要考虑:

? 确保热端有电的隔离电源

? 确保数据路径得到隔离的隔离数据

? ADC(采样时钟或转换信号)的时钟隔离,以防热端不产生时钟

隔离电源(反激拓扑与推挽拓扑的比较)

对于传感器应用,隔离电源通常在10 W以下范围内。

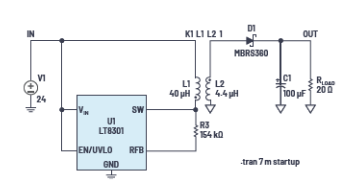

反激式转换器被广泛用于隔离电源。图1显示了反激式转换器简单可行的特点。该拓扑的优势是只需要很少的外部元件。反激式转换器只有一个集成开关。该开关可能是影响信号链性能的主噪声源。对于高性能模拟设计,反激式转换器会带来很多断点,引起电磁辐射(称为EMI),这可能会限制电路的性能。

图1.典型的反激式转换器拓扑

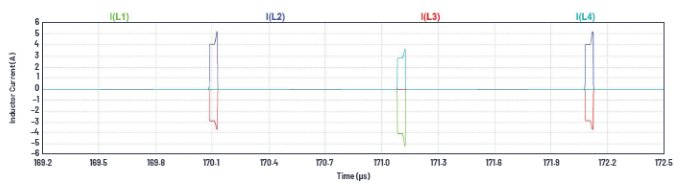

图2显示了变压器L1和L2中的电流。在初级(L1)和次级(L2)绕组中,电流在短时间内从高值跳变为零。电流尖峰可以在图3的I(L1)/I(L2)迹线中看到。电流和能量在初级电感中累积,当开关断开时,它们被传输到次级电感,产生瞬变。需要降低开关噪声效应导致的瞬变,因此,设计中必须插入缓冲器和滤波器。除了额外的滤波器之外,反激拓扑的另一个缺点是磁性材料的利用率低,而所需的电感较高,因此变压器较大。此外,反激式转换器的热环路也很大,不易管理。有关热环路的背景信息,请参阅应用笔记AN139。

反激式转换器的另一个挑战涉及开关频率变化。图3显示了负载变化引起的频率变化。如图3a所示,t1 < t2。这意味着fSWITCH随着负载电流从较高负载电流I1减小到较低负载电流I2而变化。频率的变化会在不可预测的时间产生内部噪声。此外,频率也会因器件不同而异,这使得更难以对其进行滤波,因为每个PCB都需要调整滤波。对于一款5 V输入范围的20位SAR ADC,1 LSB相当于大约5μV。EMI噪声引入的误差应低于5μV,这意味着为精密系统隔离电源时,不应选择反激拓扑。

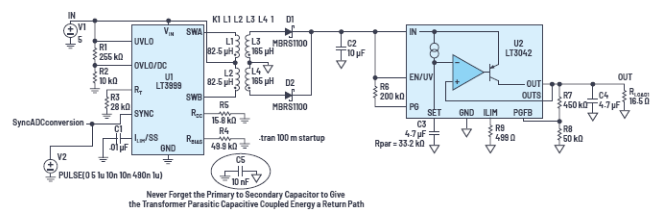

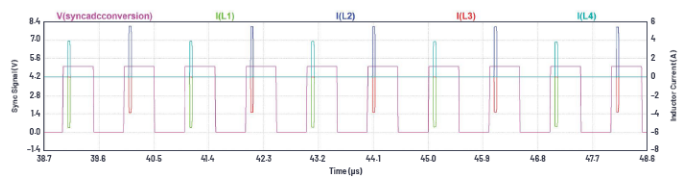

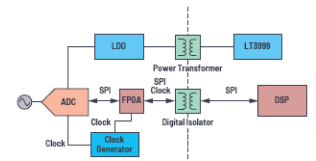

还有其他电磁辐射骚扰较低的隔离电源架构。就辐射而言,推挽式转换器比反激式转换器更合适。像LT3999这样的推挽式稳压器提供了与ADC时钟同步的可能性,有助于实现高性能。图4显示了隔离电源电路中的LT3999与ADC采样时钟同步的情况。请记住,初级到次级电容为开关噪声提供了一个避免共模噪声效应的返回路径。该电容可以在PCB设计中利用重叠的顶层平面和第二层平面实现,以及/或者利用实际电容实现。

图2.LT8301在变压器绕组中切换电流

图3.(a) LT8301频率变化,(b)从2.13 ms到2.23 ms的频率变化的特写

图4.具有超低噪声后置稳压器的LT3999

图5.LT3999电流波形

图6.LT3999及其与同步引脚的切换关系

图5显示了变压器处的电流波形(初级侧和次级侧电流),它更好地利用了变压器,提供更好的EMI行为。

图6显示了与外部时钟信号的同步。采集阶段的末端与同步引脚的正边沿对齐。因此,将有一个大约4μs的较长安静时间。这使得转换器可以在该时间范围内对输入信号进行采样,并将隔离电源的瞬变效应降至最小。LTC2378-20的采集时间为312 ns,非常适合<1μs的安静窗口。

数据隔离

数据隔离可以使用数字隔离器实现,例如ADuMx系列数字隔离器。这些数字隔离器可用于SPI、I2C、CAN等许多标准接口,例如ADuM140 可用于SPI隔离。 为了实现数据隔离,只需将SPI信号SPI时钟、SDO、SCK和Busy连接到数据隔离器。在数据隔离中,电能通过感性隔离栅从初级侧传输到次级侧。需要添加电流返回路径,这由电容来完成。该电容可以在PCB中利用重叠平面实现。

时钟隔离

时钟隔离是另一项重要任务。如果使用1 MHz采样速率的20位高性能ADC,例如LTC2378-20,可以实现104 dB的信噪比(SNR)。为了实现高性能,需要无抖动时钟。为什么不应使用像ADuM14x系列这样的标准隔离器?标准隔离器会增加时钟抖动,从而限制ADC的性能。更多详细信息请参见设计笔记DN1013。

图7显示了不同频率、不同类型时钟抖动下SNR的理论极限。像LTC2378这样的高性能ADC的孔径时钟抖动为4 ps,在200 kHz输入下理论限值为106 dB。

图7.时钟抖动与ADC性能的关系

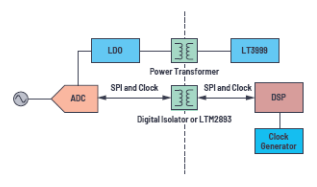

图8.使用标准隔离器实现时钟隔离

图8显示的标准时钟隔离器概念包括:

? 像ADuM250N这样良好的标准数字隔离器的抖动为70 ps rms。对于100 dB SNR目标,由于时钟抖动,信号采样速率限制为20 kHz。

? 像LTM2893这样优化的时钟隔离器提供30 ps rms的低抖动。对于100 dB SNR目标,现在的信号采样速率为50 kHz,在全部SNR性能下可提供更多带宽。

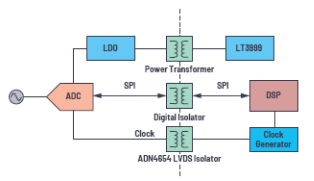

图9.使用LVDS时钟隔离器实现时钟隔离

? 图9:对于更高的输入频率,应使用LVDS隔离器。ADN4654提供2.6 ps抖动,接近ADC的最佳性能。在100 kHz输入时,时钟抖动导致的SNR限值将是110 dB。

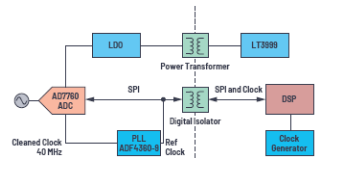

图10.使用额外PLL净化时钟抖动的时钟隔离

? 图10:使用PLL净化时钟。 ADF4360-9可以帮助减少时钟抖动。

图11显示了使用PLL净化时钟的更详细框图。您可以将ADF4360-9用作时钟净化器,并在输出端增加一个2分频器。AD7760额定支持1.1 MHz。

图11.ADF4360-9用作时钟净化器

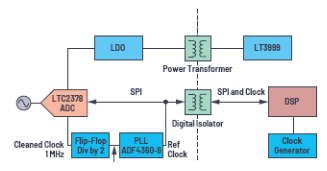

因此,不能直接支持LTC2378等1 MSPS SAR ADC。在这种情况下,低抖动触发器会有帮助。它将时钟2分频。

图12.触发器用于降低时钟以用于LTC2378

图13.隔离(热)侧的时钟产生

? 图13:本地产生时钟是获得具有所需抖动性能的时钟的另一个方案。本地时钟生成会使时钟架构更加复杂,因为它将异步时钟域引入系统。例如,若要使用两个单独的隔离ADC,则时钟的绝对频率将会不同,必须增加采样速率转换以重新匹配时钟。有关采样速率转换的一些细节,请参阅工程师对话笔记EE-268。

高性能Sigma-Delta ADC的时钟

时钟的类似问题也适用于高性能Sigma-Delta ADC,如AD7760。这里,重要的时钟信号是无抖动过采样时钟,例如40 MHz。这种情况下不需要额外的分频器。

结论

隔离式高性能ADC需要仔细设计隔离方案并选择隔离技术,以实现高于100 dB的高性能SNR。应特别重视隔离时钟,因为时钟抖动的影响可能会破坏性能。其次应注意隔离电源。简单的隔离拓扑(如反激)会引入高EMI瞬变。

为了获得更好的性能,应使用推挽式转换器。还需要关注数据隔离(尽管不太重要),可用标准器件能提供良好性能,对整体系统性能的影响较小。介绍这三个隔离主题有助于设计人员提出高性能隔离系统解决方案。

作者简介

Wilfried Platzer曾在德国卡尔斯鲁厄学习信息技术,侧重于射频技术。他1997年开始在ITT工作,后来在TDK-Micronas工作。Wilfried担任过多种职位,从现场应用工程师开始,然后专注于混合信号IC的概念和系统架构工程设计。11年后,他跳到Auma从事电子预开发工作。2015年,他加入凌力尔特公司(现为ADI公司的一部分)。目前,Wilfried是ADI公司的高级现场应用工程师,负责为瑞士提供区域支持。

图片新闻

技术文库

最新活动更多

-

1月8日火热报名中>> Allegro助力汽车电气化和底盘解决方案优化在线研讨会

-

1月9日立即预约>>> 【直播】ADI电能计量方案:新一代直流表、EV充电器和S级电能表

-

即日-1.16立即报名>>> 【在线会议】ImSym 开启全流程成像仿真时代

-

即日-1.20限时下载>>> 爱德克(IDEC)设备及工业现场安全解决方案

-

即日-1.24立即参与>>> 【限时免费】安森美:Treo 平台带来出色的精密模拟

-

即日-1.31立即参与>>> 【限时免费下载】村田白皮书

推荐专题

分享

分享

发表评论

请输入评论内容...

请输入评论/评论长度6~500个字

暂无评论

暂无评论