标准FPGA资源丰富却浪费,看eFPGA怎样实现“量体裁衣”?

FPGA以计算速度快、资源丰富、可编程著称,之前一直应用于高速数字信号领域和ASIC验证。随着逻辑资源的丰富和编程工具的改进,FPGA在机器学习和硬件加速上得到越来越多的重视,目前数据中心已经大量采用,大数据、云计算领域逐步采用FPGA器件。但是除了这些对计算能力和逻辑资源要求很高的应用,市面上还有很多功能简单的小型应用,如果采用现有的“大而全”的FPGA产品,不仅价格昂贵,而且资源浪费。于是有人想到了定制化服务,这样可以让工程师根据产品需求定制合适的FPGA产品,从而达到节约成本和功耗的目的,嵌入式FPGA有望解决这一问题。

最近,Achronix为其eFPGA IP解决方案推出Speedcore custom blocks定制单元块。其市场营销副总裁Steve Mentor介绍,“Speedcore custom blocks定制单元块可以大幅度地提升性能、功耗和面积效率,并支持以前在FPGA独立芯片上无法实现的功能。利用Speedcore custom blocks定制单元块,客户可以获得ASIC级的效率并同时保持FPGA的灵活性,从而带来了一种可以将功耗和面积降至最低、同时将数据流通量最大化的高效实现方式。”

通过两层裁剪让芯片面积缩小多达6倍

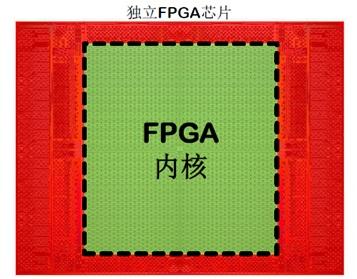

FPGA用户都指导,标准FPGA不仅包含FPGA内核中的逻辑设计、各种存储器、DSP以及布线,而且还包含内核以外的可编程I/O、SerDes以及各种接口控制器,这就使得芯片资源丰富,但体积庞大,成本昂贵,因此要实现成本的缩减就要裁掉设计中不必要的资源。Achronix的做法是进行了两层裁剪:

如图所示,第一层裁剪将外部的可编程I/O、SerDes以及各种接口控制器进行裁剪,只留下FPGA内核,这样面积可以缩小50%。

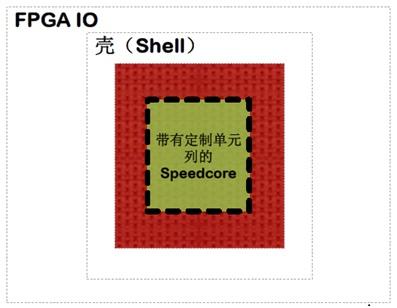

如图所示,裁剪掉外围模块以后,FPGA内核是否可以进一步缩小?那么,先从FPGA内核的结构分析,Steve Mentor指出,“Microsoft在其有关Catapult项目的白皮书中讲了一种云规模的加速架构,包括壳(shell)和应用(Application),其中shell布局IO及与电路板相关的逻辑电路,应用是核心逻辑,Shell占据了44%的总面积。”

Achronix进行了第二层裁剪,将shell去掉,剩下由用户定义功能的Fusion Custom Block定制单元块,包含在Speedcore的可编程结构中。经过这道裁剪,芯片面积缩减高达75%。

如何定义Fusion Custom Block单元块?

如何实现定义,这是很多用户最关心的问题。Steve Mentor解释,“Achroinx使用内部工具来分析客户的设计,以识别出可以用Fusion Custom Block单元块开进行优化的潜在功能,比如经常使用的重复性功能,从而实现面积缩减、性能提高和功耗降低。现在,Achronix eFPGA IP产品在添加了Speedcore custom blocks定制单元块以后,就使其在拥有可编程性的同时还能够拥有ASIC级的性能以及高片芯面积效率。”

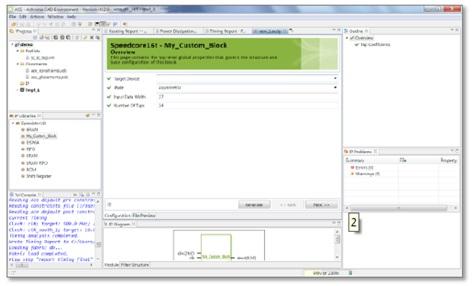

FPGA设计中开发工具很关键,Achronix也提供了ACE设计工具,可以全面支持Speedcore custom blocks定制单元块,可以与存储器和DSP单元块相同的方式,提供从设计捕获到比特流生产和系统调试等功能。

Achronix为每个Speedcore custom blocks定制单元块创建了一种独有图形化用户接口(GUI),它可以管理所有的配置规则。ACE拥有Speedcore custom blocks定制单元块所有配置的完整的时序细节,支持ACE去完成各种设计基于时序的布局和布线。客户可以用强大的版图规划器来优化设计,并为所有的单元实例去制定局域或者定点的任务安排。ACE还包括一个关键路径分析工具,它可以支持客户去分析时序。客户还可以使用ACE强大的Snapshot嵌入式逻辑分析仪,去创建复杂的触发器并展示Speedcore内的实时信号。

eFPGA既然如此灵活,那么它是否会在未来代替FPGA?Steve Mentor表示,“目前来看,标准FPGA的市场占有率大概是80%,eFPGA是20%,复杂应用的客户中有人愿意在ASIC设计中加入eFPGA,简单应用的客户有些愿意用eFPGA来代替标准FPGA完成设计,但是两者针对的客户群不同,会长期共存。”

“正是eFPGA的市场需求旺盛,Achronix在2017年实现了强劲的销售收入及业务增长,预计销售将超过1亿美元。与TSMC和做的16nm产品已经量产,7nm产品预计在2018年上半年完成测试芯片和首批设计。” Steve Mentor补充。

图片新闻

最新活动更多

-

11月28日立即报名>>> 2024工程师系列—工业电子技术在线会议

-

11月29日立即预约>> 【上海线下】设计,易如反掌—Creo 11发布巡展

-

11月30日立即试用>> 【有奖试用】爱德克IDEC-九大王牌安全产品

-

即日-12.5立即观看>> 松下新能源中国布局:锂一次电池新品介绍

-

12月19日立即报名>> 【线下会议】OFweek 2024(第九届)物联网产业大会

-

即日-12.26火热报名中>> OFweek2024中国智造CIO在线峰会

分享

分享

发表评论

请输入评论内容...

请输入评论/评论长度6~500个字

暂无评论

暂无评论