从架构日“宣言书”到CES全面展示,英特尔如何布局下一个计算时代?

了解PC硬件的朋友有言,Intel近几年有点儿水逆了。

先是近几代酷睿处理器的架构都是小幅改良,运算效能提升不大,被人冠以“牙膏厂”的外号,而10nm量产还要等待一段时间;AMD则凭借桌面端的Ryzen处理器叫好又叫座,虽然服务器领域的EPYC处理器一时间还没对Xeon造成严重威胁,但若Intel再不搞些大手笔,怕也得担心进一步的失守。

外界似已产生不少质疑。一向以架构和工艺扬名立万的Intel,似乎在自己最拿手的领域有些hold不住,又被其他领域占据许多精力。这些貌似有些毫无章法的动作,让一众玩家纷纷怀疑,Intel到底还能拿出什么来稳固在半导体产业的领导力?若真舍弃了架构和工艺上的优势,Intel还能剩下什么?

“Intel是一家数据公司。”

在上个月的架构日活动和刚刚过去的CES展会上,Intel的全新技术战略和产品展示似乎给出了答案。

六大支柱的由来

无论是刚刚过去的CES大展,还是上个月的架构日活动,Intel一直在着重介绍其聚焦于六个工程领域的全新技术战略,即:

制程——拥有领先的制程技术,仍是建构领先的产品之关键。先进的封装解决方案在三维空间中扩展晶体管密度,将带来指数级提升计算密度的能力。

架构——通过先进的封装和系统集成技术,把多样化的标量(scalar)、矢量(vector)、矩阵(matrix)和空间(spatial)计算架构组合部署到CPU、GPU、加速器和FPGA芯片中,并通过可扩展的软件堆栈释放强大的能力。

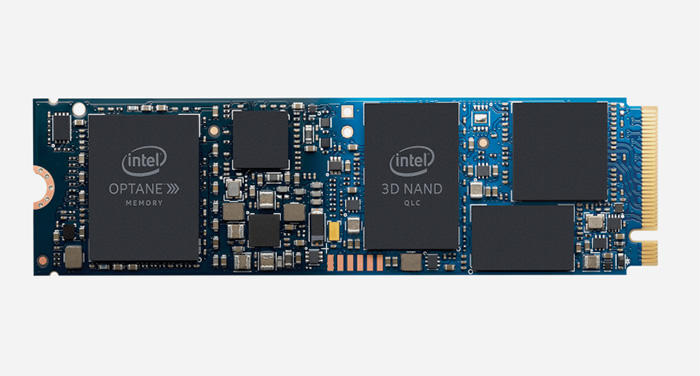

内存——大容量、高速度的存储对于下一代计算工作负载至关重要。通过将闪存和傲腾技术相结合,可填补内存层级中的空白,从而在更靠近硅芯片的地方提供带宽。

超微互连——通信技术大到面向5G基础设施的无线连接,小到芯片级封装和裸片互连。只有提供全面的领先互连产品,才能实现大规模的异构计算格局。

安全——随着安全威胁的不断涌现,Intel可提供安全技术,帮助实现端到端的全面提升,并让安全性成为关键的差异化因素。

软件——对于开发者来说,拥有一套利用好英特尔芯片的通用工具集,对于获得性能的指数级扩展至关重要。

对于大部分普通消费者来说,关注点往往集中在架构和工艺两方面,笔者作为一名资深DIYer也不例外,这也是与我们最直接相关且日常接触最多的领域。不过等到如愿以偿的时候,更多的却是一种情理之中的感觉,反而是其他几个新领域更能给人以新鲜的快感。

存在于回忆杀里的那个Intel,更多的是一家单纯的PC处理器公司,然而实际上,Intel早已将自己定位为一家数据公司,并将“万物互联”定为未来发展趋势。

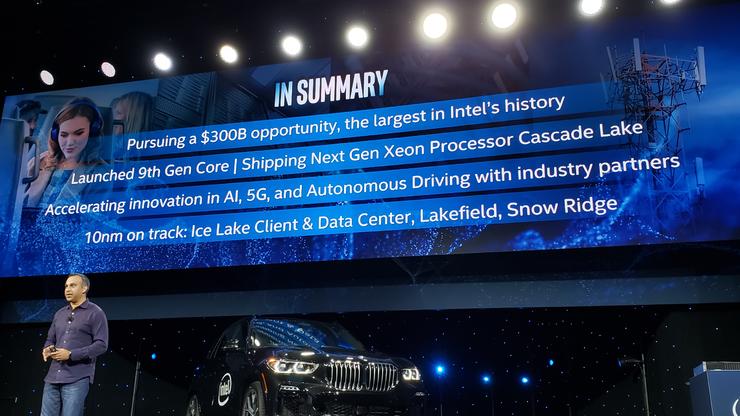

围绕这一点,Intel自己对这次的CES已经有了一个总结:这些技术的演进,是在为更加多元化的数据时代奠定基石。

《福布斯》资深分析师Patrick Moorhead此前曾表示,Intel通过让自己进入更大的市场,其潜在市场规模从只聚焦于传统笔记本电脑和服务器领域时的450亿美元,升级到集存储、网络、IoT和软件等多领域于一体的3000亿美元。

以Intel傲腾技术为例,在如今这个大数据时代,数据的海量规模、多样性和急剧增长已是司空见惯。Intel认为,数据洪流不应该仅仅视为一个存储问题,还可将它视为一次数据优化的机遇,一个成功的现代数据策略应该是软件定义的策略,以应用要求为基础,并能实现智能分层。

傲腾技术平衡了RAM的高性能和非易失性存储的大容量,通过将更多数据放到更接近CPU的位置,使应用在人工智能和大型数据库中的更大量的数据集能够获得更快的处理速度,减少进行访问时的延迟,从而提高工作负载的性能。

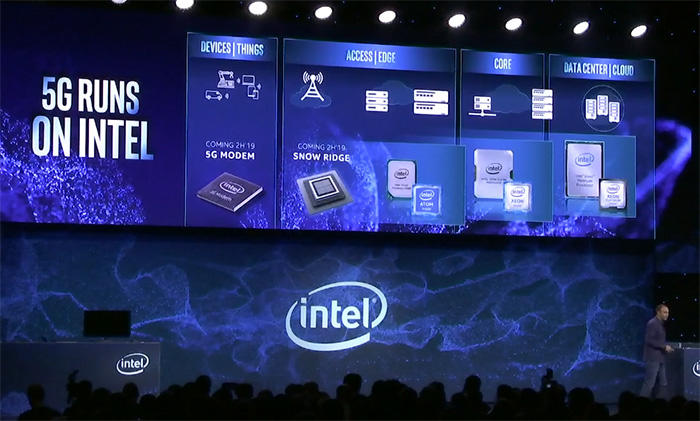

另一方面,5G也一直是Intel的一个技术和战略重点。Intel数据中心事业部总经理Navin Shenoy在CES上曾提到,5G的过渡及其对网络的影响,在加速数据和催化软件定义网络方面,与从模拟向数字的飞跃一样具有变革意义,届时定制芯片将被容器技术取代。

即是说,我们正处于以数据为中心不断演进的世界中央,5G是未来创新平台的DNA和基石,带来无缝连接、几乎无限的计算。

Navin Shenoy在会后透露,Intel将推出全新专门面向5G无线接入和边缘计算的、基于10nm工艺的网络系统芯片,研发代号“Snow Ridge”;使用多模5G LTE架构的Intel XMM 5G调制解调器支持全部3个毫米波频段和6GHz以下频段,将在2019年下半年交付给合作伙伴,并在2020年初推出产品。

同时由于网络束缚原理,一旦5G打破现有的通讯瓶颈,将会影响数据中心、云计算、边缘计算等多个方向,Intel也将面向零售、视频、工业和智慧城市等重点行业,为物联网设计高性能芯片,增强边缘计算,并大力发展计算机视觉技术。

而作为一家传统印象中的硬件公司,Intel对于软件环境的重要性也是心明眼亮。说白了, 光是东西自身素质好还不够,还要让大家用的好。完善的软件环境所带来的结果是,硬件底子差不多的情况下,Intel的产品可以跑的更快;实际表现差不多的两套系统,Intel的更好用。

这样的例子在处理器发展史上比比皆是,不说别的,单单是Intel专属ICC编译器相对通用型GCC编译器的性能优势,就让其在服务器领域从容接下了AMD和Arm一次又一次的挑战。这种“软”实力,也是Intel二三十年来能将霸主地位越坐越稳的重要因素。

归结起来看,Intel是在利用Core架构和Tick-Tock策略这些年积累下来的领先地位,为架构和工艺这两条好汉又拉来了四个帮。六大战略支柱所针对的某些领域,在普通消费者看来,似乎与传统印象中以CPU起家的芯片巨头并不搭边,但其实都是对架构和工艺的补完与助益。

未来会怎么样?未来的竞争基础是什么?怎样给用户带来更多价值?

Gregory Bryant认为,对整个计算系统的全面优化是未来的竞争基础。优化不止针对于一个方面,而是看哪个公司能将最好的CPU、GPU、AI加速器、通信系统、高速存储等部分有机的结合到一起,进行全方位优化,这样才能最终给终端用户带来更多的价值。

Intel客户端计算事业部总经理Gregory Bryant在CES结束后解释道,下一个计算时代要求创新在完全不同的层面进行,涵盖整个生态系统并横跨计算、连接以及其它各个方面。六大战略支柱为Intel建立了一个框架,是推动架构和芯片开发的基石,而架构师们则根据这些支柱,决定每年在发展路线图上实现的具体目标。

架构和工艺

认识过了这些相对陌生的技术领域后,回过头来再看架构和工艺这两个传统主场。

虽然上面分析了种种,看得出Intel在整个计算市场确实有着很大很长远的布局,可说回到与普通消费者最直接相关的架构和工艺上,不得不说Intel确实遇到了不少麻烦和困难:近几代处理器的架构都是小幅改良,运算效能提升不大,10nm新工艺也是久攻不下。

好在今年的CES上,Intel展示了第一款10纳米的Ice Lake处理器,以高集成度整合了Intel全新的“Sunny Cove”微架构、AI使用加速指令集以及第11代核心显卡,从而提升图形性能。2019年晚些时候,Sunny Cove将成为下一代PC和服务器处理器的基础架构。

实际上,早在前几年坊间便有传闻称,Intel已经意识到Core架构体系已经开始难以应对未来的发展需要,将在2020年前后推出全新的架构体系,而这恰好与如今的情况相吻合,一定程度上也表明Intel对于发展路线的规划还是比较全面且长远的。

雷锋网之前的文章已先行分析过,Sunny Cove架构旨在提高通用计算任务下每时钟计算性能和降低功耗,并包含了可加速人工智能和加密等专用计算任务的新功能,能够减少延迟、提高吞吐量,并提供更高的并行计算能力,有望改善从游戏到多媒体到以数据为中心的应用体验,其功能特性包括:

增强的微架构,可并行执行更多操作。

可降低延迟的新算法。

增加关键缓冲区和缓存的大小,可优化以数据为中心的工作负载。

针对特定用例和算法的架构扩展。例如,提升加密性能的新指令,如矢量AES和SHA-NI,以及压缩/解压缩等其它关键用例。

同时,随着眼下数据中心的计算类型正如同寒武纪大爆发一样增长,Intel也一直在构建不同计算类型的产品组合,包括Intel传统的CPU、Arria和Stratix的FPGA,及其Crest神经网络处理器等等。

Intel首席架构师Raja Koduri在架构日上曾指出,并非所有的晶体管都能适用于不同的场景,在不同的市场领域,需要的晶体管设计十分多样,如通信晶体管、I/O晶体管、FPGA晶体管,以及传统的CPU逻辑晶体管,即便可以用单一工艺大费周章的制造大型单芯片系统,也不是个明智的做法。

基于此,Intel在业界首创了名为Foveros的全新逻辑芯片3D堆叠技术,可实现在逻辑芯片上堆叠逻辑芯片。这是一种系统级封装集成,有望首次将晶片的堆叠从传统的无源中间互连层和堆叠存储芯片扩展到CPU、GPU和AI处理器等高性能逻辑芯片,为整合高性能、高密度和低功耗硅工艺技术的器件和系统铺平了道路。

Intel在CES现场展示了使用“Foveros”3D封装技术混合CPU架构和封装架构的Lakefield ,其采用22FFL IO芯片作为有源载板,并用TSV(硅通孔技术)连接了一颗10nm芯片,其中包含1个Sunny Cove内核和4个Atom内核(可能是Tremont)。这款微型芯片尺寸为12*12,待机功率仅为2mW。

至于10nm工艺,雷锋网曾分析认为,由于晶体管制造的复杂性,单纯用代次来对比已经不再准确。若以业内常用晶体管密度来衡量制程水平,Intel 10nm工艺的晶体管密度反而要比台积电的7nm DUV制程更高。

国外网站Semiwiki讨论了三星的10nm、8nm DUV以及7nm EUV制程的情况,其中10nm制程的晶体管密度是55.5MTr/mm2,8mm DUV是64.4MTr/mm2,7nm EUV也不过101.23MTr/mm2,堪堪超过Intel 10nm制程一点点。

中国工程院院士许居衍曾在一次学术会议上提到,从晶体管尺寸数据来看,90nm节点的物理栅长是25nm,32nm节点的栅长是24nm,节点进步带来的物理栅长收益越来越小,缩小的制程节点,实际上没有缩小半导体最关键的、有源区的部位“源-漏”上的问题。

从指标上可以看出,随着节点的更迭,制造工艺理应随着趋近极限而收益放缓,但Intel对晶体管密度的要求不减反增,并提出了“超微缩”这一理念。雷锋网认为,这也是为了逆破收益放缓的屏障,更加有效的延续摩尔定律。

若将晶体管理解为字,将光刻工艺理解为笔,那Intel就相当于要在不轻易更换笔尖的情况下写出更小的字,其中难度可想而知。虽然眼下进程受阻,但从长远来看,超微缩的技术经验显然会为后续工艺带来更大收益。

本届CES 2019发布会上,Intel一口气公布了10nm在PC、服务器、全新封装技术以及5G应用,涵盖了六大支柱所涉及的所有方向。可以看出,Intel在这个节点的布局上拼的并非是10nm工艺本身,而是围绕10nm制程打造的完整生态体系。

前沿之前的探索

雷锋网了解到,十年之前Intel曾做过一次路线图预测,包括对新材料、新工艺的预估。现在回过头来看,预测中大部分的方向都是没有问题的。

在推进摩尔定律的过程中,80%的工作是基于材料的改革,另外20%的工作则是在寻求化学工艺方面的进步,如原子层沉积、原子层蚀刻等技术,即不光要研究怎样把芯片做小,还要研究怎样用不同的方式来做这些器件。

据悉,Intel每年都会对半导体器件的性能进行评估。这些研究可以进一步发现如何更好的在电路中使用晶体管,如何将新式晶体管与新架构、新功能相结合。目前来看,CMOS所处的位置还是很不错的,其功耗和性能表现要优于大部分望半导体元器件。至少在最近的十年里,还是要以CMOS为主来制造芯片,其他的新技术可以与CMOS混合使用以提高性能、降低功耗或降低价格。

同时,对于未来的新型处理器,Intel在几个方面都有相应的工作在进行。例如神经拟态芯片,目前已经有了10nm的样片,这是一种非冯·诺依曼架构的芯片,完全把存储和计算单元融合在了一起,模拟了神经元和神经元之间的连接,是一种异步控制的芯片,可以在片上进行自学习,支持无监督学习、监督学习、自监督学习和强化学习模式。

而在量子计算方面,Intel已经在7、17、49三种量子比特节点上进行了大量实验。但量子的相互干渉是本世纪27个重大问题之一,目前只能做到毫秒级连续计算,且量子计算目前的容错率只有99.9%,而传统芯片为99.9999999%,因此硅CMOS+冯·诺依曼的模式还要持续很长一段时间。

Intel中国研究院院长宋继强称,CMOS的微缩还会继续进行下去,但会通过材料、化学工艺等不同方法来实现,可以通过3D封装技术将晶体管堆叠起来,此外还有一些新的电路控制方式,可以让摩尔定律继续推进下去。

可见,对于后摩尔定律时代,Intel的后手还很充足。

雷锋网总结

新的时代,是Intel几十年来最大的转变和革新。

如果说英特尔的架构日是“宣言书”,那么它在CES上一系列创新技术、产品与合作的发布,则是对“宣言书”更全面、更深刻的展示,意味着它对自己的方向更加地坚定和充满自信。

雷锋网认为,Intel的新战略需要从两个角度来衡量,“这是否是市场所需”,“它是否可以实现”。六大支柱战略非常有野心。考虑到不断变化的数据世界和摩尔定律的现状,这一策略很适合Intel。

顺便说一句,不仅是Intel,摩尔定律也是每家芯片厂商需要面临的新现实。如果芯片厂商未来五年还坚持只做单一的大芯片,很可能会被市场抛弃。

Intel的财务状况一直很好,但面对市场上出现的动荡,Intel的大手笔很大胆,也很艰难。在接下来的一年里,Intel还会有很多里程碑式的重要披露,雷锋网也会进一步追踪并研究Intel的新战略,看它如何落地,是否能引起大转折,敬请期待。

图片新闻

最新活动更多

-

4月16日预约观看>> 开发前服,优化项目投资价值 筑牢落地关键防线

-

4月17日立即报名 >> 【线下论坛】新唐科技×芯唐南京 2026 年度研讨会

-

4月22日立即报名>> 【在线会议】ADI六款仪器仪表方案助力产品快速上市

-

5月13日立即预约>>> 【线下会议】恩智浦创新技术峰会·深圳

-

5月14日立即下载>> 【白皮书】村田室内外定位解决方案

-

即日-5.20立即下载>> 【限时免费】物理场仿真助力生物医学领域技术创新

分享

分享

发表评论

登录

手机

验证码

手机/邮箱/用户名

密码

立即登录即可访问所有OFweek服务

还不是会员?免费注册

忘记密码其他方式

请输入评论内容...

请输入评论/评论长度6~500个字

暂无评论

暂无评论