一文读懂EMC测试实质

二、传导骚扰测试实质

LISN是电源端口传导骚扰测试的关键设备,从图4中可以看出,接收机接于LISN中的1 kΩ的电阻与地之间,当接收机与LISN进行互连后,接收机信号输入口本身的阻抗50 Ω与LISN中的1 kΩ电阻处于并联状态,其等效阻抗接近于50 Ω,由此也可以看出,电源端口传导骚扰的实质就是测试50 Ω 阻抗(这个阻抗由LISN中的1 kΩ的电阻与接收机的输入阻抗并联而成)两端的电压。

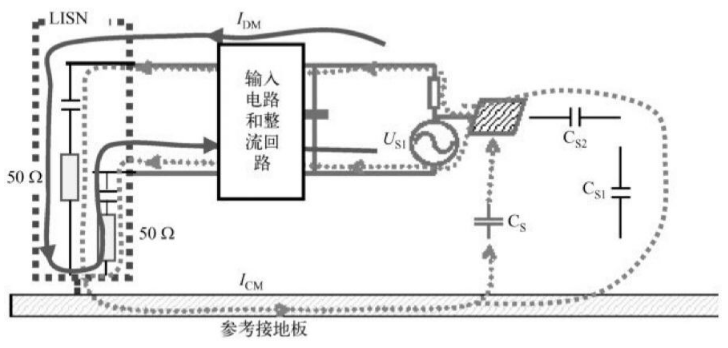

当阻抗50 Ω一定时,电源端口传导骚扰的实质也可以理解为流过这个50 Ω阻抗的电流的大小。在实际产品中有两种电流会流过这个50 Ω阻抗,一种是图4 中的IDM,另一种是图4中的 ICM。无论是IDM还是ICM,都会在接收机中显示出测试值,而接收机本身无法判断是哪种电流引起的传导骚扰。这需要设计者去控制与分析。控制产品中的骚扰电流不流过LISN和接收机并联组成的50 Ω阻抗是解决电源端口传导骚扰问题的关键。通过大量的实践证明,大部分的电源端口传导骚扰问题产生于ICM,它是一种共模电流,分析其路径和大小有着极其重要的意义。

图4 引起电源端口传导骚扰的电流

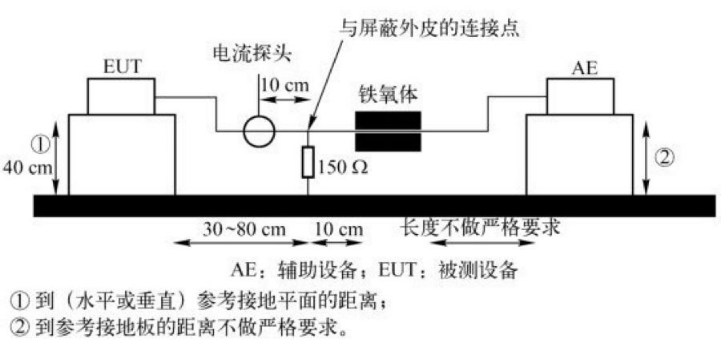

电流探头是信号端口传导骚扰测试的关键设备。图5是信号端口传导骚扰测试配置图,从图5 中可以明确看到电流探头实质上测试的就是EUT电缆上的共模电流。当然与单极天线或偶极子天线模型产生辐射发射一样,引起信号端口传导骚扰的共模电流通常不是信号端口上的正常工作电流信号,而是一些“无意”的共模电流引起的。可见,信号端口传导骚扰测试实质上与辐射发射测试中因产品中的电缆或长尺寸导体产生的等效单极天线或偶极子天线模型而产生的辐射发射是一致的,只是频段上不一样。

图5 信号端口传导骚扰测试配置图

三、ESD抗扰度测试实质

图6 某一产品进行ESD测试时的ESD放电电流分布路径

从ESD测试配置描述可以看出,在进行ESD测试时,需要将静电枪的接地线接至参考接地板(参考接地板接安全地),EUT放置于参考接地板之上(通过台面或0.1 m高的支架),静电放电枪头指向EUT中各种可能会被手触摸到的部位或水平耦合板和垂直耦合板,这就决定了ESD测试是一种以共模为主的抗扰度测试,因为ESD电流最终总要流向参考接地板。ESD干扰原理可以从两方面来考虑。首先,当静电放电现象发生在EUT中被测部位时,伴随着ESD放电电流也将产生,分析这些ESD放电电流的路径和电流大小具有极其重要的意义。

值得注意的是,ESD接触放电电流波形的上升沿时间会在1 ns以下,这意味着ESD是一种高频现象。ESD放电电流路径与大小不但由EUT的内部实际连接关系(这部分连接主要在电路原理图中体现)决定,而且还会受这种分布参数的影响。图6表达了某一产品进行ESD测试时的ESD放电电流分布路径。图6中的CP1、CP2、CP3分别是放电点与内部电路之间的寄生电容、电缆与参考接地板之间的寄生电容和EUT壳体与参考接地板之间的寄生电容。这些电容的大小都会影响各条路径上的ESD电流大小。

如果有一条ESD电流路径包含了产品的内部工作电路,那么该产品在进行ESD测试时受ESD的影响就会很大;反之则产品更容易通过ESD测试。可见,如果产品的设计能避免ESD共模电流流过产品内部电路,那么这个产品的抗ESD干扰的设计是成功的,ESD抗扰度测试实质上包含了一个瞬态共模电流(ESD电流)流过产品(瞬态共模电流)干扰正常工作电路的原理。

其次,ESD测试时所产生的ESD电流还伴随瞬态磁场,当这种时变的磁环经过电路中的任何一个环路时,该环路中都会产生感应电动势,从而影响环路中的正常工作电路。四、共模传导性抗扰度测试实质共模抗扰度测试以共模电压的形式把干扰叠加到被测产品的各种电源端口和信号端口上,并以共模电流的形式注入到被测产品的内部电路中(产品的机械结构构架对EFT/B共模电流的路径与大小起着决定性的作用,或直接以共模电流的形式注入到被测产品的内部电路中,共模电流在产品内部传输的过程中,会转化成差模电压并干扰内部电路正常工作电压(产品电路中的工作电压是差模电压)。

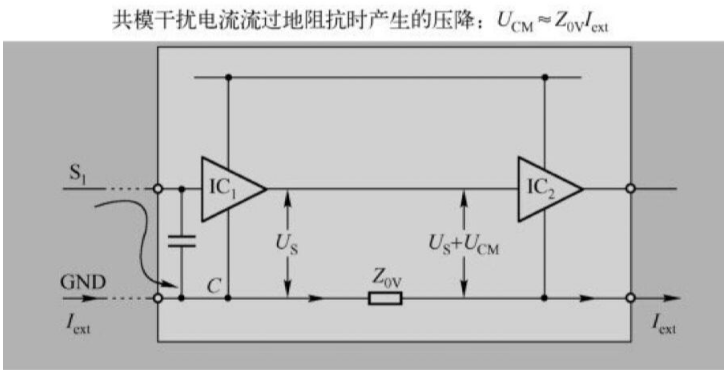

对于单端传输信号,如图1所示,当同时注入到信号线和GND地线上的共模干扰信号进入电路时,在IC1的信号的端口处,由于S1于GND所对应的阻抗不一样(S1 较高,GND较低),共模干扰信号会转化成差模信号,差模信号存在于S 1 与GND之间。这样,干扰首先会对IC1的输入口产生干扰。滤波电容C的存在,使IC1 的第一级输入受到保护,即在IC1 的输入信号端口和地之间的差模干扰被C滤除或旁路(如果没有C的存在,可能干扰就会直接影响IC1的输入信号),然后,大部分会沿着PCB中的低阻抗地层从一端流向地层的另一端,后一级的干扰将会在干扰电流流过地系统时产生(当然这里忽略了串扰的因素,串扰的存在将使干扰电流的流径路径复杂化,因此串扰的控制在EMC设计中也是非常重要的一步)。

图7共模干扰电流流过地阻抗时产生的压降

其中,图7中的Z0V表示PCB中两个集成电路之间的地阻抗,US表示集成电路IC1向集成电路IC2传递的信号电压。共模干扰电流流过地阻抗 Z0V时,Z0V的两端就会产生压降 UCM≈Z0V Iext。该压降对于集成电路IC 2 来说相当于在IC 1 传递给它的电压信号 U S 上又叠加了一个干扰信号U CM,这样IC 2 实际上接受到的信号为U S+U CM,这就是干扰。干扰电压的大小不但与共模瞬态干扰的电流大小有关,还与地阻抗 Z0V的大小有关。当干扰电流一定的情况下,干扰电压UCM的大小由Z0V决定。也就是说,PCB中的地线或地平面阻抗与电路的瞬态抗干扰能力有直接影响。

例如,一个完整(无过孔、无裂缝)的地平面,在100 MHz的频率时,只有3.7 mΩ的阻抗。即使有100 A的瞬态电流流过3.7 mΩ 的阻抗,也只会产生0.37 V的压降,这对于3.3 V的TTL电平的电路来说,是可以承受的,因为3.3 V的TTL电平总是要在0.8 V以上的电压下才会发生逻辑转换,这已经是具有相当的抗干扰能力了。又如,流过电快速瞬变脉冲群干扰的地平面存在1 cm的裂缝,那么这个裂缝将会有1 nH的电感,这样当由100 A的电快速瞬变脉冲群共模电流流过时,产生的压降:V= | L×dI/dt| =1 nH×100 A/5 ns=20 V20 V的压降对3.3 V电平的TTL电路来说是非常危险的,可见PCB中地阻抗对抗干扰能力的重要性。

实践证明对于3.3 V的TTL电平逻辑电路来说,共模干扰电流在地平面上的压降小于0.4 V将是安全的;如果大于2.0 V将是危险的。对于2.5 V的TTL电平逻辑电路,这些电压将会更低一点(0.2V和1.7V),从这个意识上,3.3V TTL电平的电路比2.5V电平的TTL电路具有更高的抗干扰能力。

对于差分传输信号,当共模电流ICM流过地平面时,必然会在地平面的阻抗Z0V两端产生压降,当共模电流ICM一定时,地平面阻抗越大,压降越大。像单端信号被干扰的原理一样,这个压降犹如施加在差分线的一根信号线与参考地之间,即图8中所示的 UCM1、UCM2、UCM3、UCM4。

图8 共模干扰电流对差分电路的干扰原理

由于差分线对的一根线与参考地之间的阻抗Z1、Z2,接收器与发送器的输入/输出阻抗Z S1、Z S2,总是不一样的(由于寄生参考的影响,实际布线中不可能做到两根差分线对的对地阻抗一样),从而造成UCM1、UCM2、UCM3、UCM4的值也不相等,差异部分即转化为差模干扰电压Udiff,对差分信号电路产生干扰。可见,对于差分电路来说,地平面的阻抗也同样重要,同时PCB布线时,保证差分线对的各种寄生参数平衡一致也很重要。

五、差模传导性抗扰度测试实质

差模传导性抗扰度测试原理非常简单,测试时,差模干扰电压直接叠加在正常工作电路上,然后观察电路工作是否正常。由于单一的差模传导性抗扰度测试通常都是低频的测试,而且都是针对瞬态干扰的抗扰度测试,这样传递干扰路径的分析也比较容易,因为较小的寄生参数不会对低频信号传输产生较大的影响。六、差模共模混合的传导性抗扰度测试实质差模共模混合的传导性抗扰度测试主要是指,在传导性抗扰度测试中,既要进行差模测试又要进行共模测试,或在差模过程中既有共模的干扰直接注入到产品被测端口上,又有差模的干扰直接注入到产品被测端口上的传导性抗扰度测试。

图片新闻

技术文库

最新活动更多

-

即日-1.16立即报名>>> 【在线会议】ImSym 开启全流程成像仿真时代

-

即日-1.20限时下载>>> 爱德克(IDEC)设备及工业现场安全解决方案

-

即日-1.24立即参与>>> 【限时免费】安森美:Treo 平台带来出色的精密模拟

-

即日-1.31立即参与>>> 【限时免费下载】村田白皮书

-

即日--2.7了解详情>> 【森海塞尔】TeamConnect系列产品——提升视听之体验,塑造音频之未来

-

限时免费立即试用>> 燧石技术,赋光智慧,超越感知

推荐专题

分享

分享

发表评论

请输入评论内容...

请输入评论/评论长度6~500个字

暂无评论

暂无评论