揭开一个等长不等时的“骗局”

“DDR4跑2400,等长控±25mil,时序有没有问题?”

“正常操作,没有问题”

“那时序差260ps有没有问题?”

“那怕是药丸”

“那等长控±25mil,时序差260ps有没有问题?”

瞬间这个问题就把我惊出了一身冷汗,我们的layout工程师,真是各种操作秀到人头皮发麻。虽然在SI领域还是个小学生,但我也知道等长相差在25mil左右时,时序是不可能相差260ps的。

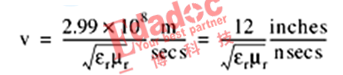

我们的layout工程师也知道,按照常规操作来讲,普通FR4级别的板材,时序和长度换算的经验公式是1ps≈6mil。像这种脱离常识的事情必须要用事实说话,于是反手就发了一张图,长度和时间如下图所示。

从上面的图上看来,信号之间的长度差只有4mil的情况下,时序相差266ps,这真的是刷新了三观。

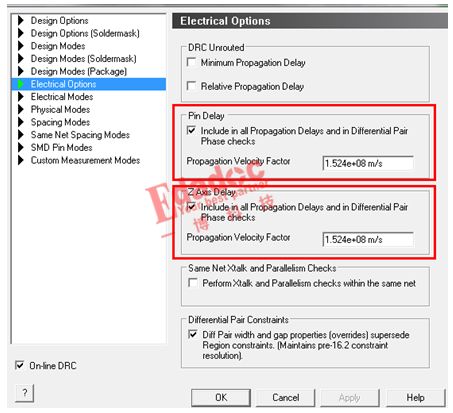

但是事实摆在了眼前,那就需要找到导致这种情况的原因了。等长不等时的情况虽然存在,但是目前还是设计阶段,时序差距又如此离谱,所以设置出现问题的可能性比较大。首先怀疑是不是pin delay时间没有填正确引起的,检查了PIN delay的设置。嗯,意料之中,PIN delay开关是打开的,问layout工程师,是不是pin delay没有填写正确,结果回复是软件中没有填pin delay的相关参数,这个可能性pass了。

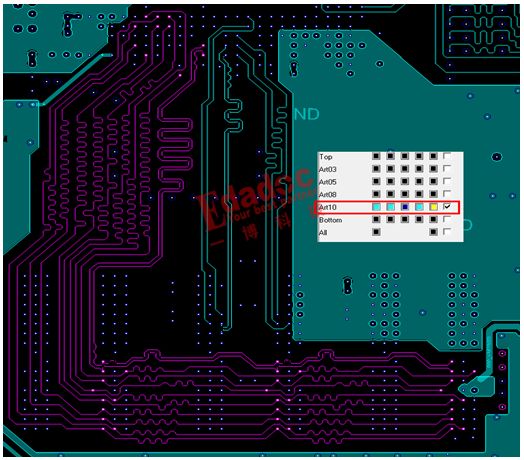

既然不是软件设置问题,那么把时间短的网络高亮,看看具体的走线情况,如下图所示,发现所有时序参数比较小的网络都集中在了第十层,如下图所示。

发现上面这个情况时,感觉到离真相只有一步之差了,但是又有一层纸挡在中间,感受不到那一闪而过的灵感。从头开始捋一下这个过程。从时序和长度的换算公式开始,看影响因素有哪些。下面是传输线在介质中的传输速度公式:

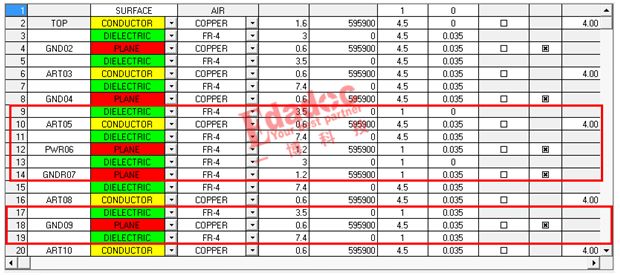

影响因素两个,一个是相对导磁率,一般不含铁磁体的介质材料,这个参数都为1;另一个是相对介电常数,这个和材料参数的设置有关系,可以在软件的层叠设置中体现。检查一下层叠,看这个参数的设置是否有问题。如下图所示,果然,DK的设置是有部分不正确的。

将DK按照设计的层叠重新正确填写后,时序回复了正常,如下图所示。

所以其实这种等长不等时的情况,实际上延时的误差并不存在,是软件设置欺骗了你,实际的板子生产后,并不会有这种延时差距。虽然不会带来什么影响,但是这个情况的出现,可能会让设计人员吓自己一跳,以致夜不能寐,于是就有了开头的提问。

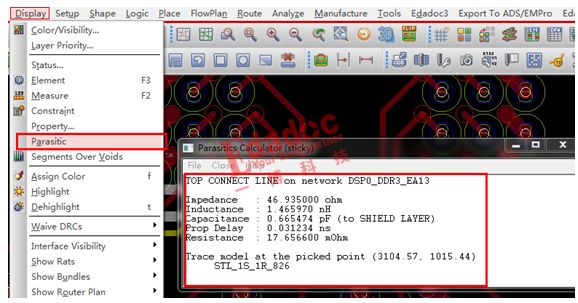

下面是文末彩蛋时间,设计中的层叠参数正确填写是很有必要的,影响不仅是时序方面,还可以根据这些参数用软件直接算阻抗,如下图所示,这是软件自带的一个小功能,可以计算传输线的阻抗和电容,电感参数。

— end —

本期提问

实际中,什么情况可能造成等长却不等时?

参与互动答题送定制记事本

1、参与有效答题,评论区前10名将获赠定制记事本(封面可刻字)

2、活动截止时间:2019年6月17日10点整

3、上周获奖名单如下:TROY/涌/whisper/柳辉/白开水/Shinen/杆/张广平/吉祥/zaki,请在后台私信小编,发送:姓名+公司名称+手机+地址+刻字内容(仅限4个字以内)。

微信公众号 | 高速先生

文作者| 刘为霞

图片新闻

技术文库

最新活动更多

-

即日-1.16立即报名>>> 【在线会议】ImSym 开启全流程成像仿真时代

-

即日-1.20限时下载>>> 爱德克(IDEC)设备及工业现场安全解决方案

-

即日-1.24立即参与>>> 【限时免费】安森美:Treo 平台带来出色的精密模拟

-

即日-1.31立即参与>>> 【限时免费下载】村田白皮书

-

即日--2.7了解详情>> 【森海塞尔】TeamConnect系列产品——提升视听之体验,塑造音频之未来

-

限时免费立即试用>> 燧石技术,赋光智慧,超越感知

推荐专题

分享

分享

发表评论

请输入评论内容...

请输入评论/评论长度6~500个字

暂无评论

暂无评论