漫谈板级有源测试

关于测试,分板级测试和芯片测试,板级测试又分无源测试,有源测试。板级测试的目的是验证在当前特定的这块PCB上,板材、拓扑结构、走线长度等等都已固化的情况下,信号质量如何。芯片测试的目的是验证这款芯片,它的各项性能最好能到什么程度、最薄弱的环节又在哪。因为芯片测试的仪器是误码仪,跟板级测试的手段、目的都不相同,所以今天我们先讲讲板级测试中的有源测试,芯片测试放到下次再讲。

上周关于测试的留言中点赞人数最多的问题是:“请讲解一下测试的具体步骤、需要测试哪些参数、如何看懂波形及如何从波形上判断信号质量。”这个问题看似寥寥两行,其实是个范围非常大的问题。

首先不同的信号有不同的测试方法:比如接口测试,那首先你得有个test fixture,将板子上的信号引到fixture上,然后用SMA cable或者probe进行测试,典型的有HDMI、USB、PCIE、网口等,如果你是板内信号测试,那你就在板上的测试点上用probe进行点测。

其次,不同的信号需要测试的参数不同:

有的要测skew,对间对内的skew都要测,典型就是各种显示接口,比如HDMI;

有的要测波形、时序,像需要参考外部时钟采样的信号基本都要测,比如I2C、DDR等,其中像I2C这种菊花链结构信号,总线上会挂多个device,每个device有自己唯一的地址代码,所以要根据地址代码把每个device都测到;

有的只要测眼图即可,内嵌时钟信号的serdes信号都属于这种,比如PCIE;

有的要测板子工作时的极限情况,比如所有设备都插上同时工作时的电压跌落、插拔动作造成的浪涌,典型的就是USB;

有的要测试晶振出来时钟信号的频率及偏差,此时不能示波器测,要用频率计测(由于频率计的操作实在是太简单了,就不展开讲了);

前面列举的“有的……有的”都是针对信号,电源除了要分别测轻载、重载时的电源压降、纹波噪声,有时还要测power on、power off的时序。

下面我们从设计阶段简单介绍测试的过程。

首先在设计时要考虑到这根信号是否有测试的需求,通常这个DFT(Design For Test)检查会放在设计基本完成时做。如果有测试需求,检查在RX BGA端附近有没有过孔或AC耦合电容,有就不需要再额外添加测试点,以避免引入多余的东西:一个开窗的圆形焊盘,肯定比你的走线要宽得多,这对于信号来说会额外增加一个阻抗不连续点。如果芯片直接表层出线且在芯片BGA 焊盘500mil以内都没有“天然的”测试点,那就需要人工额外加测试点了,测试点的要求是:位置加在500mil以内,越近越好,圆形测试点的直径越小越好,一般20mil。

PCB做好后,板厂会用TDR做基本的阻抗测试,但板厂做的是阻抗条测试,不是你板上真正的链路。所以一般你会拿到一两片光板,方便你自己做板内链路的阻抗测试。

等PCBA后,板子上电正常的才会拿去做SI测试,不要问什么……没有电哪来的信号。

下面以一个DDR4-2400的地址信号测试为例简单介绍测试过程:先选一台带宽≥6GHz的示波器,加一根单端探棒、一根差分探棒;挑选最近、最远两个颗粒;单端、差分探棒分别点在颗粒端的地址、时钟信号上,如果你有芯片公司提供的tool也行,不然就得老老实实焊接进行探测了;然后调整触发电平使信号稳定的显示在屏幕上。

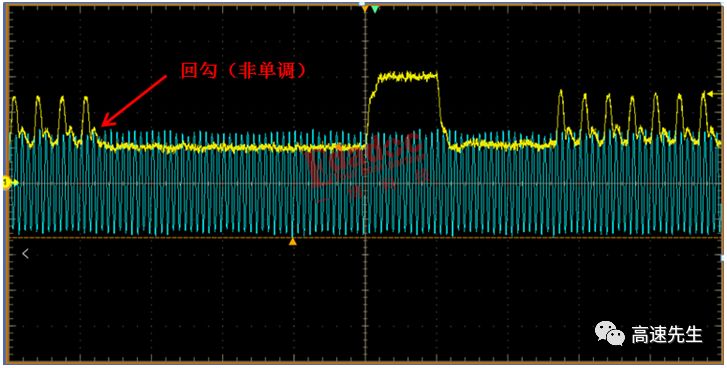

结果发现最近的颗粒上在400mV~500mV间地址信号存在明显的回沟。功能测试也发现DDR4信号有误码,甚至都不能初始化。

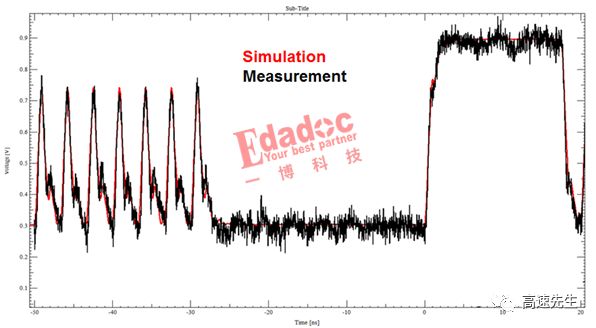

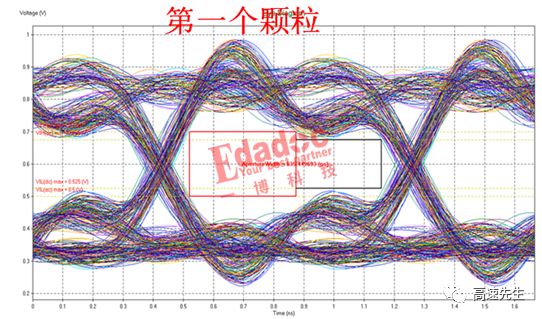

作为仿真工程师,就喜欢做一下仿测拟合确认问题,万一是因为测试点的原因呢,毕竟测试点和芯片die还有一段距离呢(就算测试点就在pin上,pin到die还有一段封装长度),而且之前也常遇到测试点上波形不行,但是die上波形好好的情况。所以把测试数据保存成.csv格式文档,做了一下仿测拟合,测试点上的波形和测试结果拟合上后,去看第一个颗粒所有地址信号在die上的眼图……咦~~~确实有问题哦,绝大部分的地址信号的回勾都压到VIH/VIL电平了。

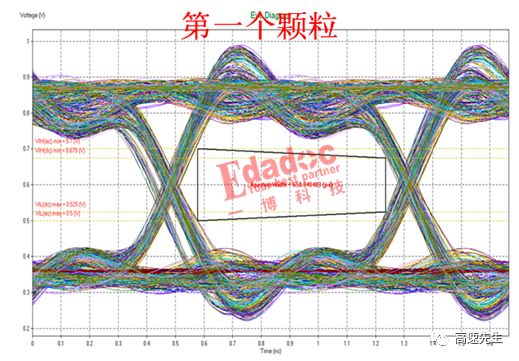

我们知道这个回沟是由于颗粒感受到的阻抗不匹配造成的,因为DDR的地址信号大多数情况下都是一拖多的结构,每一个颗粒处在链路的不同位置,所以多重反射后每个颗粒感受的阻抗也是不一样的。为此,我们调整了走线以使减弱阻抗不匹配的反射程度,调整后颗粒die上所有的地址信号回沟都远离了VIL/VIH。

上面只是以地址信号的波形质量为例,当然还有其它参数要测,只是操作方法大同小异,就不一一列举了,不然就成SOP了。

鉴于有些同学问的问题比较杂散,不太好穿插在文章里讲,只好单独给你们翻牌子了~~今天只能翻三位,不能更多啦~~

“wifi等信号如何测试阻抗,测试走线的起点和终点分别在哪?”

——阻抗测试不需要分起点和终点,从哪头测都行,哪头有测试点就在哪头测,但是通常情况下,像WiFi这种天线信号,只有芯片这边是有测试点的(信号pin开窗,同时有地pin),同时像WiFi这种天线信号测试,更通用的测试不是测阻抗,而是用矢网测驻波比。

“网络分析仪怎么测阻抗?”

——网分是频域的仪器,但时域和频域之间可以通过傅里叶变换/逆傅里叶变换的数学运算来实现互换,所以只要在网分上安装了TDR控件,仪器就能将频域的S参数通过数学运算转成时域的阻抗,并显示在屏幕。同理如果你用时域的TDR测出了TDT,也可以显示出S参数。

“高速连接器如何测试?”

——首先你得做套fixture:公头母头各一块,再加TRL校准板一块(或者买软件去嵌也可);然后你得有台矢网哦~~

微信公众号 | 高速先生

文 | 刘丽娟

图片新闻

技术文库

最新活动更多

-

即日-1.16立即报名>>> 【在线会议】ImSym 开启全流程成像仿真时代

-

即日-1.20限时下载>>> 爱德克(IDEC)设备及工业现场安全解决方案

-

即日-1.24立即参与>>> 【限时免费】安森美:Treo 平台带来出色的精密模拟

-

即日-1.31立即参与>>> 【限时免费下载】村田白皮书

-

即日--2.7了解详情>> 【森海塞尔】TeamConnect系列产品——提升视听之体验,塑造音频之未来

-

限时免费立即试用>> 燧石技术,赋光智慧,超越感知

推荐专题

分享

分享

发表评论

请输入评论内容...

请输入评论/评论长度6~500个字

暂无评论

暂无评论