Nerissa Draeger博士:全包围栅极结构将取代FinFET

作者:泛林Nerissa Draeger博士

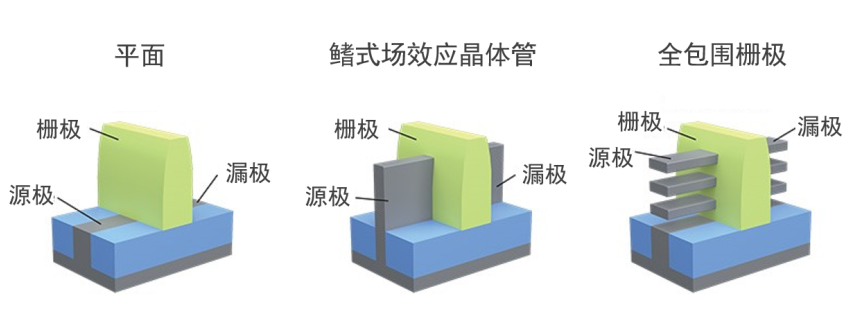

FinFET在22nm节点的首次商业化为晶体管——芯片“大脑”内的微型开关——制造带来了颠覆性变革。与此前的平面晶体管相比,与栅极三面接触的“鳍”所形成的通道更容易控制。但是,随着3nm和5nm技术节点面临的难题不断累积,FinFET的效用已经趋于极限。

晶体管缩放的难题

在每个技术节点,设备制造商可以通过缩小晶体管的方法来降低器件面积、成本和功耗并实现性能提升,这种方式也称为PPAC(功率、性能、面积、成本)缩放。然而,进一步减小FinFET的尺寸却会限制驱动电流和静电控制能力。

在平面晶体管中,可以通过增加通道宽度来驱动更多电流并提升接通与断开的速度。然而,随着CMOS设计的发展,标准单元的轨道高度不断降低,这就导致“鳍”的尺寸受到限制,而基于5nm以下节点制造的单鳍器件将会无法提供足够的驱动电流。

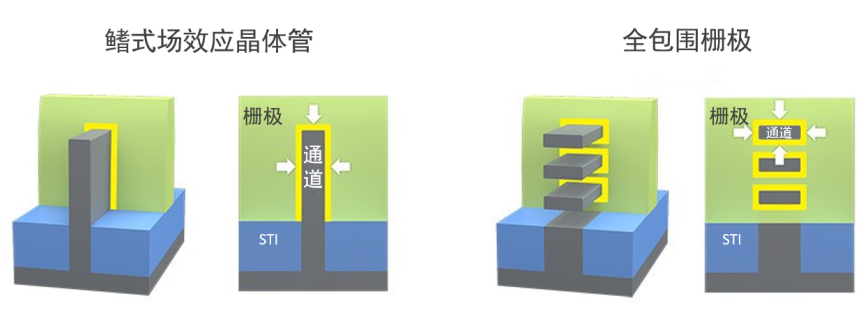

此外,虽然“鳍”的三面均受栅极控制,但仍有一侧是不受控的。随着栅极长度的缩短,短沟道效应就会更明显,也会有更多电流通过器件底部无接触的部分泄露。因此,更小尺寸的器件就会无法满足功耗和性能要求。

用纳米薄片代替鳍片

全包围栅极(GAA)是一种经过改良的晶体管结构,其中通道的所有面都与栅极接触,这样就可以实现连续缩放。采用这种结构的晶体管就被称为全包围栅极(GAA)晶体管,目前已经出现多种该类晶体管的变体。

早期的GAA器件使用垂直堆叠纳米薄片的方法,即将水平放置的薄片相互分开地置入栅极之中。相对于FinFET,这种方法下的通道更容易控制。而且不同于FinFET必须并排多个鳍片才能提高电流,GAA晶体管只需多垂直堆叠几个纳米薄片并让栅极包裹通道就能够获得更强的载流能力。这样,只需要缩放这些纳米薄片就可以调整获得满足特定性能要求的晶体管尺寸。

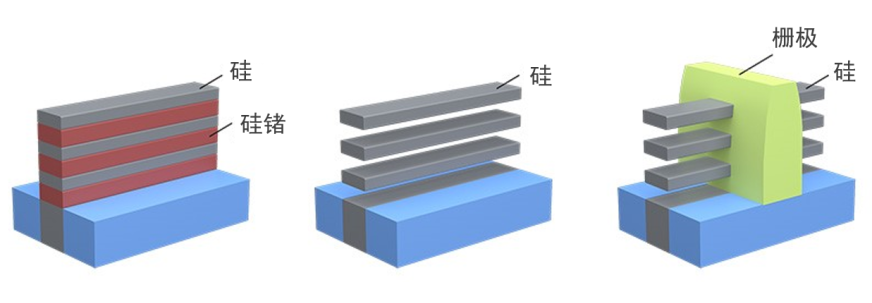

然而,和鳍片一样,随着技术进步和特征尺寸持续降低,薄片的宽度和间隔也会不断缩减。当薄片宽度达到和厚度几乎相等的程度时,这些纳米薄片看起来会更像“纳米线”。

制造方面的挑战

尽管纳米薄片的概念很简单,但它却给实际制造带来了诸多新挑战,其中有些制造难题源于结构制成,其他则与满足PPAC缩放目标所需的新材料有关。

具体而言,在构建方面的主要挑战源于结构的复杂性。要制造GAA晶体管首先需要用Si和SiGe外延层交替构成超晶格并用其作为纳米薄片结构的基础,之后则需要将电介质隔离层沉入内部(用于保护源极/漏极和确定栅极宽度)并通过刻蚀去除通道的牺牲层。去除牺牲层之后留下的空间,包括纳米片之间的空间,都需要用电介质和金属构成的栅极填补。今后的栅极很可能要使用新的金属材料,其中钴已经进入评估阶段;钌、钼、镍和各种合金也已被制造商纳入考虑范围之内。

持续的进步

GAA晶体管终将取代FinFET,其中的纳米薄片也会逐渐发展成纳米线。而GAA结构应该能够适用于当前已经纳入规划的所有先进工艺节点。

从最早的平面结构开始,晶体管架构已经取得了长足的进步并有效推动了智能互联的大发展,这一切都是早期的行业先驱们所难以想象的。随着全包围栅极晶体管的出现,我们也热切期待它能为世界带来更令人惊叹的终端用户设备和功能。

图片新闻

技术文库

最新活动更多

-

即日-12.26立即报名>>> 【在线会议】村田用于AR/VR设计开发解决方案

-

1月8日火热报名中>> Allegro助力汽车电气化和底盘解决方案优化在线研讨会

-

1月9日立即预约>>> 【直播】ADI电能计量方案:新一代直流表、EV充电器和S级电能表

-

即日-1.14火热报名中>> OFweek2025中国智造CIO在线峰会

-

即日-1.20限时下载>>> 爱德克(IDEC)设备及工业现场安全解决方案

-

即日-1.24立即参与>>> 【限时免费】安森美:Treo 平台带来出色的精密模拟

推荐专题

分享

分享

发表评论

请输入评论内容...

请输入评论/评论长度6~500个字

暂无评论

暂无评论