新型嵌入式机器视觉系统的设计研究

高清视频处理子系统(HDVPSS)有两个独立视频捕捉输入端口VIP0与VIP1.VIP0可配置成24 b、16 b、和两个独立的8 b模式,VIP1可配置成16 b、和两个独立的8 b.从捕捉频率和各种配置模式可看出,针对不同的流量,可以有多种实现方法。为了存储设计简单,本方案将VIP0配置为24 b进行采集。在此模式下,最高流量为165M×24 8 = 495 MB/s,可以满足流量要求。

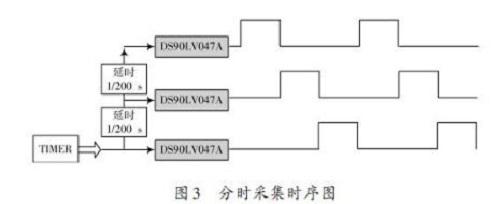

从最高捕捉时钟可知,每次采集间隔在1 165M,约为6.1 ns.经计算,也为了设计方便,拟采用三个帧频均为200 f/s的Base配置的Camera Link相机,帧频控制均为外部触发方式,该Camera Link相机一次输出两个像素,每像素12 b,即2×12 b,刚好可以和VIP0的24 b匹配采集。以三路信号分时采集为例,如图3所示,3路信号的采集方法为3个相机轮流采集,即一个循环内每个相机各采一帧,这就需要实现3路分时采集的时序信号。由定时器产生一个1/200 s的脉宽,经延时环节使帧频高电平分时分路送入三个相机;3路采集信号时序关系为一个相机不进行延时,一个相机延时1/200 s,最后一个延时2/200 s。

相机通过DS90LV047A收到指令后,将拍摄到的图像数据分为4路LVDS数据信号和1路LVDS时钟信号,通过接口连接器MDR26传输到DS90CR288A;DS90CR288A将串行数据转换成28路并行信号和1路随路时钟信号,并传送至TMS320DM8168视频捕捉端口VIP0进行采集。

2.3图像存储模块

从上述设计方案,系统存储速率约为160 MB/s,数据量较大,可选择大容量、高速的固态硬盘,通过其SATA2接口写入。

数据采集结束后,通过配置HDVPSS子系统将数据送入VPDMA,最后转入DDR内存,当DDR内存的数据量达到设定的数据量时产生中断,中断发生后,根据存放地址启动内存和固态硬盘之间的DMA传输,将采集的图像通过SATA2接口存储在SSD上,实现数据存储。

然后启动定时器产生下一个帧频脉冲,开始下一周期的数据采集。

外部扩展存储器选取系统支持的DDR3(1 600)存储器。按照系统存储控制器位宽32 b来算,内存速率可达32/8×1 600M=6.4 GB/s.在该模式下,采集和存储可并行处理。缓存所采集的数据移动到DDR3内存,其速率远高于端口采集的每秒数据量。因为该方案的采集方式是每帧轮流采集,并且帧内数据已按顺序紧凑排列,可大幅减少数据的重排工作,仅需去除一些辅助数据。采集系统将其余相关信号全部置成一帧一行的形式,让相机的时钟信号与系统采集端口的时钟信号通信,图像信号前有少量的辅助数据,设置DMA起始地址时直接跳过辅助数据。所以在本系统几乎不运行程序的情况下,固态硬盘可以最少有80%的时间占据DMA控制权进行内存图像数据的存储。按所选取的硬盘的持续写入速率250 MB/s来算,250×0.8=200 MB/s大于160 MB/s,所以1 s采集的数据可以进行实时存储。数据上传后,可以选择清除原有数据,释放硬盘空间。

2.4外围接口模块

基于TMS320DM8168芯片丰富的外设接口,本系统能够灵活的进行外部接口设计来控制外围设备,并实现与外部处理器的通信功能。根据需求可供选取的接口有:2个具有GMII和MDIO接口的千兆位以太网MAC(10 Mb/s,100 Mb/s,1 000 Mb/s);2个具有集成2.0 PHY的USB端口;双DDR2/3 SDRAM接口等,可参考图2。

图片新闻

最新活动更多

-

5月10日立即下载>> 【是德科技】精选《汽车 SerDes 发射机测试》白皮书

-

5月16日火热报名>>> OFweek锂电/半导体行业数字化转型在线研讨会

-

5月22日立即报名>>> OFweek 2024新周期显示技术趋势研讨会

-

5月28日立即观看>> 【在线研讨会】Ansys镜头点胶可靠性技术及方案

-

5月31日立即报名>> 【线下论坛】新唐科技2024未来创新峰会

-

6月18日立即报名>> 【线下会议】OFweek 2024(第九届)物联网产业大会

- 1 拆机实锤!华为Pura70使用新芯片,推测为7nm,性能如何?

- 2 华为P70系列即将强势来袭,能否再次复制华为Mate60系列的辉煌?

- 3 中国芯片基地诞生:一年产量1055亿颗,占全国30%,三省共占67%

- 4 华为麒麟9010、苹果A17、高通8Gen3对比,差距有多大?

- 5 避免内卷?中国大陆4大芯片代工厂,产能、营收、优势介绍

- 6 形势严峻!暴增256%,中国还在疯狂进口ASML光刻机

- 7 过去14个月,山东从荷兰进口了12台光刻机

- 8 华为Pura70又打脸了?美国商务部长:华为芯片没那么先进

- 9 MTK和Intel联手,投资RISC-V芯片新贵谋发展?

- 10 华为Pura70证明:我们7nm已没问题,接下来是5nm、3nm

分享

分享

发表评论

请输入评论内容...

请输入评论/评论长度6~500个字

暂无评论

暂无评论