嵌入式存储器的设计方法和策略

时序和功能验证

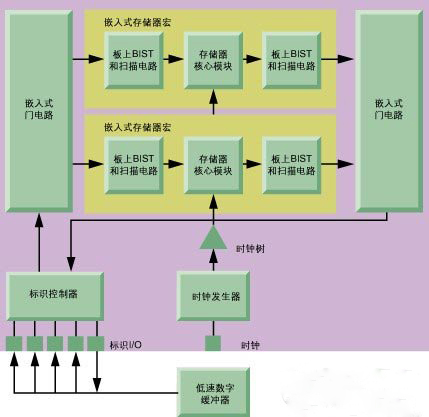

对高性能半导体芯片,精确的时序模型至关重要。为了提取嵌入式存储器中关键路径的特征并进行仿真,要采用了Avant!公司的Hspice软件。从仿真运行时间来看,仿真整个宏的LPE网表是不切实际的,为此要采用集总和加载技术(见图3)。

图3 采用集总和加载技术

集总和加载方法是通用技术,面临分布式载荷造成的模型不精确的问题,并受到由阻容(RC)网络引起的传输线效应的影响。RC网络不仅包含阻容元件,还包含要对栅极、源极和漏极电容精确建模的晶体管。为了获得精确时序,要建立验证关键路径中所有元件与实际宏的LPE网表之间匹配程度的工具。对我们感兴趣的节点,要比较关键路径和LPE网表之间的引线、栅极、源极、漏极、耦合电容和电阻。当这些参数不匹配时,就必须修正负载模型。

Hspice可以仿真温度、P-T-V曲线并对每个角作出测量说明和绘图分析,从而便于查找不正确的电路行为,例如分析信号偏移率变差的程度、由串扰引起的信号尖峰、不期望的脉冲重叠程度、传输延迟变坏的程度、时钟电路的建立和保持时间变坏的程度等。

我们通常利用Verilog或VHDL模型来仿真整个SoC并对其建模。为了确保精确度,每个嵌入式存储器都有一个与之对应的Verilog模型,这样才能确保电路的功能与HDL模型匹配。对每个存储器,要建立全面的测试平台来测试所有的地址组合、控制和测试模式(即扫描和BIST),然后,我们将测试矢量及其相关的预测数据应用到每个宏的所有LPE网表。

如上所述,可以证明用Hspice仿真大型网表和大型测试向量集(通常有数千个向量)是不切实际的。为了弥合Hspice和Verilog之间的差距,要采用Synopsys公司的Timemill测试工具, 该工具可将逻辑等价性测试和电路的电性能验证结合起来,它可将向量驱动的全部存储器的LPE网表作为输入置于Verilog环境中进行仿真,其优点在于能检测电路网表和Verilog模型之间功能上的差异,并具有良好时序精度,从而发现时序缺陷。Timemill测试工具不是故障仿真器,但是测试向量能够涵盖99%以上的待测节点。我们在与Hspice仿真相同的P-T-V曲线下运行了Timemill测试。此外,还检测了未驱动的节点、最低和最高工作频率及P-T-V曲线的极端情形。

物理验证

我们还采用Mentor Graphics公司的Calibre工具来验证物理设计,并用完整的LVS和DRC规则基准来检验电路连接的正确性、所有的间距和宽度等,用附加的质量保证规则基准来检验浮动层、阻抗连接和不期望出现的几何结构。

图片新闻

最新活动更多

-

4月16日预约观看>> 开发前服,优化项目投资价值 筑牢落地关键防线

-

4月17日立即报名 >> 【线下论坛】新唐科技×芯唐南京 2026 年度研讨会

-

4月22日立即报名>> 【在线会议】ADI六款仪器仪表方案助力产品快速上市

-

5月13日立即预约>>> 【线下会议】恩智浦创新技术峰会·深圳

-

5月14日立即下载>> 【白皮书】村田室内外定位解决方案

-

即日-5.20立即下载>> 【限时免费】物理场仿真助力生物医学领域技术创新

分享

分享

发表评论

登录

手机

验证码

手机/邮箱/用户名

密码

立即登录即可访问所有OFweek服务

还不是会员?免费注册

忘记密码其他方式

请输入评论内容...

请输入评论/评论长度6~500个字

暂无评论

暂无评论