嵌入式存储器的设计方法和策略

存储器的复杂性和独特性表明,采用存储器编译器并不完全可行,每种嵌入式存储器都需要采用新的电路技术来设计,以便满足微处理器的高性能、高密度、低功耗和极低噪声的要求。

这样的高速微处理器必须采用最先进的0.18μm、6层铜线双镶嵌金属CMOS工艺制作,其极小的特征尺寸和高性能的晶体管使存储器设计面临严峻的考验,因为窄金属导线(线高大于水平间距)尤其容易受到串扰及电子迁移效应的影响,而晶体管的低阈值将导致抗噪声性能降低。

嵌入式存储器设计方法

要制定出每个设计人员都必须遵循的设计指南,首先要开发出一套设计标准,该标准包括最优门比率、扇出数目、最大晶体管宽度以及预布线阻抗和电容的经验法则。在高密度、高速存储器的设计过程中,要采用先进的电路技术、抗串扰技术及噪声容限设计标准。串扰标准规定了邻近信号的布线规则,其它噪声容限标准则规定静态噪声容限和锁存电路的可写性规则。

芯片的多种宏设计要求与电路标准保持一致。时钟发生器和寄存器的标准尤为重要,它们是整个CPU输入设置和保持时间维持一致的前提。为了使时钟偏差最小,设计人员需要密切控制占空比和扇出数目以及所有时钟发生器的上升和下降时间。

另外,我们采用可测性设计(DFT)方法,如扫描和全频内建自检(BIST)方法来设计每个存储器。毫无无疑,BIST技术比采用测试仪器测试要复杂得多,后者要将嵌入式存储器的I/O信号复用到测试总线上,并通过布线连接到芯片的I/O端口以便测试仪器进行测试。但是,BIST方法的优点在于与测试仪器无关,并可全频测试存储器。利用BIST复杂的测试功能,可以用标记将故障与特定的例程或一个实际的I/O或一个存储单元隔离。该特性可实现冗余处理和详细的故障分析。BIST还具备测试存储器功能和确定宏或存储器最大工作频率的能力,但通常无法计算宏的存取时间。

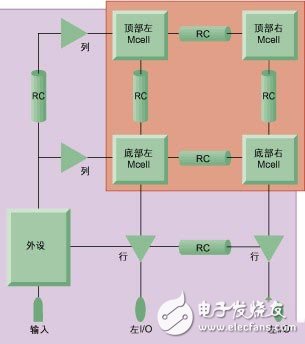

DFT方法虽然增加不到2%的开销,但对存储器的验证来说,其作用非常重要。采用这些技术及定制嵌入式ATE(自动测试设备)电路,我们已经制作了一些测试芯片来验证存储器设计过程中采用的复杂设计技术(图2)。

图2 验证存储器设计

现在,要驱动500MHz的外部I/O引脚很不实际,我们设计了专用嵌入式ATE电路来俘获并评估嵌入式宏的实际存取时间。通过建立片上测试器,可确保采用低成本的数字测试器来驱动及评测芯片。

图片新闻

最新活动更多

-

4月16日预约观看>> 开发前服,优化项目投资价值 筑牢落地关键防线

-

4月22日立即报名>> 【在线会议】ADI六款仪器仪表方案助力产品快速上市

-

5月13日立即预约>>> 【线下会议】恩智浦创新技术峰会·深圳

-

5月14日立即下载>> 【白皮书】村田室内外定位解决方案

-

即日-5.20立即下载>> 【限时免费】物理场仿真助力生物医学领域技术创新

-

5月29日立即下载>> 【白皮书】工业视觉AI实战白皮书合集

分享

分享

发表评论

登录

手机

验证码

手机/邮箱/用户名

密码

立即登录即可访问所有OFweek服务

还不是会员?免费注册

忘记密码其他方式

请输入评论内容...

请输入评论/评论长度6~500个字

暂无评论

暂无评论