一文读懂AI芯片:国产崛起的最佳时机?

近几年来,人工智能作为自互联网诞生以来的第二次技术形态的体现,随着智能产品的落地应用,不同场景的算法持续涌现,计算数据呈爆炸式增长。不少厂商为了追求产品多样化,不断推出新功能,在产品中提到的“人机交互”、“智能识别”等新鲜的概念词汇,以此吸引消费者的购买欲望。

与此同时,AI芯片作为人工智能技术的硬件基础和产业落地的载体,吸引了众多巨头和创企入局,各类AI芯片相继面世。

在近日胡润研究院发布的《2020胡润中国芯片设计10强民营企业》榜单中,按照企业市值或估值列出了中国10强本土芯片设计民营企业,分别为:韦尔股份、汇顶科技、兆易创新、卓盛微电子、君正集成电路、圣邦微电子、比特大陆、瑞芯微、晶晨半导体、地平线、寒武纪科技。11家芯片设计企业中比特大陆、地平线、寒武纪科技3家都是AI芯片公司,占据了将近1/3的比重,足以见得AI芯片发展的重要性。

从架构说起,AI芯片走了怎样一条路

其实最早AI芯片的出现并不是为了执行指令,而是为了进行大量的数据训练和应用的计算。由于传统CPU在解决深度学习任务时效率不够高,且耗费的成本昂贵,因此催生了专门解决特定任务的新硬件——AI芯片。

当前AI芯片的设计方案繁多,市面上对于AI芯片其实也没有明确统一的定义,广义上来说所有面向人工智能的芯片都叫做AI芯片。

指令级架构是主流

从芯片架构来看,目前市场上绝大多数AI芯片都是采用传统的指令集架构。

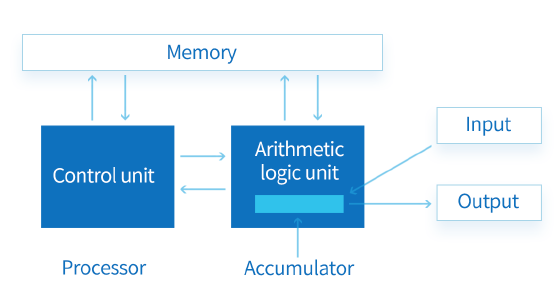

传统的指令集架构采用冯·诺依曼计算方式,通过指令执行次序控制计算顺序,并通过分离数据搬运与数据计算提供计算通用性。在本质上还是所谓的“计算优先”模式,需要通过扩展并行计算单元来提升芯片处理性能。

目前,市场上传统的通用指令集架构主要包括人们熟知的X86架构、ARM架构、RISC-V开源架构,以及SIMD架构。

虽然指令级架构凭借其通用性和广泛的应用,成为了AI芯片的主流架构,但是在AI芯片进行算法处理的过程中,涉及到大量的计算、并行处理、低时延等要求,给芯片存储器带来了巨大的挑战,这也就是冯·诺依曼计算方式下共享内存模式导致的存储性能瓶颈问题,我们又称其为“数据墙”、“内存墙”或者“冯·诺伊曼瓶颈”。

如何通过硬件体系架构的创新,克服存储性能瓶颈问题,进一步提升AI芯片深度学习算法运算效率,成为了当前AI芯片架构创新和发展的一大难题。

(基于冯诺依曼的典型指令集架构示意图)

另一条路:数据流AI芯片

要想解决内存性能跟得上计算单元算力提升的问题,就要打破冯·诺依曼架构的内存墙阻碍。由此也衍生出AI芯片架构的另一条路——数据流芯片。

相信很多人对“数据流AI芯片”了解甚少。在近日鲲云科技举办的新品发布会上,据鲲云科技创始人和CEO牛昕宇博士介绍,与传统指令集架构相比,数据流架构没有概念上的指令计数器,它是依托数据流流动次序控制计算次序,采用计算流和数据流重叠运行方式消除空闲计算单元,并采用动态配置方式保证对于人工智能算法的通用支持,突破指令集技术对于芯片算力的限制。

数据流架构采用了数据流引擎的计算架构,以实现更高的吞吐量和更低的延迟,最大优点在于大幅提升芯片利用率。目前,数据流架构在数字信号处理、网络路由、图形处理、遥感检测、以及数据库处理,以及当今许多软件体系结构中占据着重要地位。

(图片源自OFweek维科网)

当然,数据流架构AI芯片的研发难度远远大于指令集架构,目前全球基于数据流方式研究AI芯片的企业少之又少,主要有鲲云科技、Wave Computing、Sambanova、Groq,而目前能够实现数据流AI芯片量产的仅有国内的鲲云科技一家。总体而言,数据流架构也不失为未来AI芯片的一条重要发展路径。

图片新闻

技术文库

最新活动更多

-

即日-1.16立即报名>>> 【在线会议】ImSym 开启全流程成像仿真时代

-

即日-1.20限时下载>>> 爱德克(IDEC)设备及工业现场安全解决方案

-

即日-1.24立即参与>>> 【限时免费】安森美:Treo 平台带来出色的精密模拟

-

即日-1.31立即参与>>> 【限时免费下载】村田白皮书

-

即日--2.7了解详情>> 【森海塞尔】TeamConnect系列产品——提升视听之体验,塑造音频之未来

-

限时免费立即试用>> 燧石技术,赋光智慧,超越感知

推荐专题

分享

分享

发表评论

请输入评论内容...

请输入评论/评论长度6~500个字

暂无评论

暂无评论