ASML摊牌:1.4nm、0.5nm、0.2nm芯片时,才要换EUV光刻机

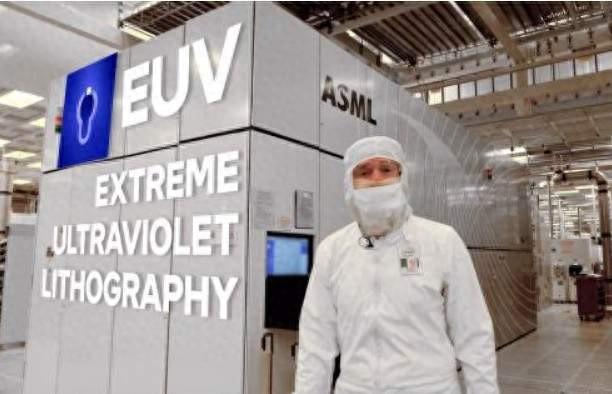

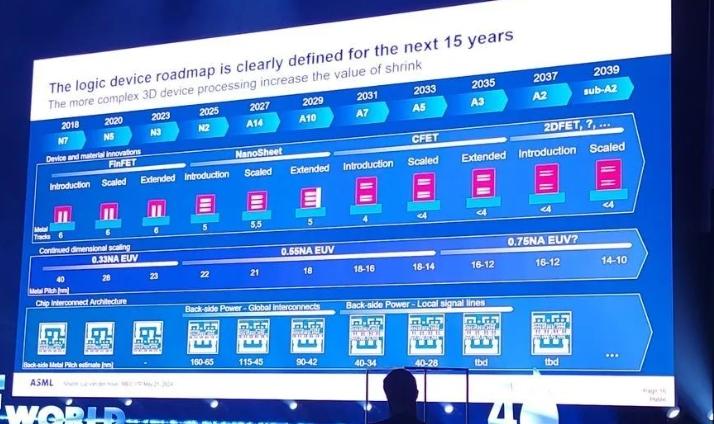

目前ASML对外大规模发售的光刻机叫做标准光刻机,也可称之为LOW NA EUV,意思就是其数值孔径是较低值的,所以称之为LOW,NA=0.33。

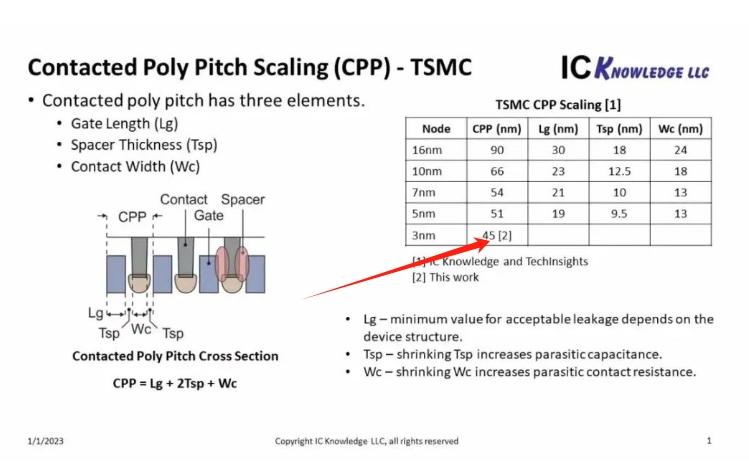

这种光刻机主要用于7nm及以下芯片的制造,至于往下能够支持到多少纳米?ASML没有说。

而按照晶圆厂的做法,intel计划在2nm时,换成新的光刻机,也就是High NA EUV光刻机。

而台积电则计划继续用LOW NA EUV光刻机,并且台积电认为,哪怕是到1.6nm时,还会继续使用LOW NA EUV光刻机,因为这样便宜,不需要更换。

毕竟一台High NA EUV光刻机,需要3.5亿欧元,而一台LOW NA EUV只需要1.5亿欧元左右,成本低很多。

那么LOW NA EUV究竟能用到什么工艺?近日,ASML摊牌了,称LOW NA EUV的数值孔径是0.33,可以打印13nm左右的线宽,最多可以制造2nm的芯片。

但是,往下还可以通过多重曝光技术来实现,但支持到2027年量产的1.4nm将会是极限,再多重曝光就不行了。

接下来,就必须更换光刻机,使用High NA EUV,这种光刻机的数值孔径达到0.55,所以也称之为高数值孔径光刻机。

NA=0.55时,可以打印8nm左右的线宽,这样可以支持到2029年1nm制程的量产,而如果再采用多重曝光,则可以支持到2033年来量产的5埃米(0.5nm)制程节点。

然后就必须现的光刻机了,再下一代EUV光刻机是 Hyper NA EUV,称之为超级,是因为其NA=0.75,比0.55还要更高了。

而采用0.75NA的Hyper NA EUV光刻机,或许可以支持到2埃米(0.2nm)以下的制程节点,至于再往下,ASML自己也不清楚,会不会有也搞不清楚。

有意思的是,虽然ASML规划了这种NA=0.75的EUV光刻机,但ASML也确定自己能不能生产的出来,因为ASML自己也表示,要NA=0.75,还需攻克很多难题,目前ASML还没有攻克的,可能需要10来年时间攻克,也许永远攻克不了。

可能很多人就有疑问了,一个硅原子的直径大概就在1埃米(0.1nm)左右,芯片工艺真的能够达到0.2nm么?感觉不可能啊。

事实上,大家要弄清楚一个事实,那就是当工艺进入28nm之后,所有的工艺其实是等效工艺,这个0.2nm并不是指线宽,栅极宽度,金属间距等,都与0.2nm没有关系了,XX纳米只是一种说法,并不是一个物理指标。

3nm时的晶体管的金属间距为22nm(45nm/2),而0.2nm芯片,对应的晶体管的金属间距为大约在16-12nm,0.2nm以下制程以下,金属间距才会进一步缩小到14-10nm。

EUV光刻机分辨率,只要能搞定这个间距间距就可以了,所以,实际上目前关于3nm、2nm、1nm等工艺,大家也不必太认真,只是一种营销上的说法。

但不管怎么样,从现在的情况来看,EUV光刻机机,也慢慢的走向末路了,哪怕XX纳米只是营销上的说法,也难以再前进了……

毕竟当0.2nm时,只有2个原子的大小了,到时候现有的光刻技术路线必然会终结。

原文标题 : ASML摊牌:1.4nm、0.5nm、0.2nm芯片时,才要换EUV光刻机

图片新闻

技术文库

最新活动更多

-

即日-12.26立即报名>>> 【在线会议】村田用于AR/VR设计开发解决方案

-

1月8日火热报名中>> Allegro助力汽车电气化和底盘解决方案优化在线研讨会

-

1月9日立即预约>>> 【直播】ADI电能计量方案:新一代直流表、EV充电器和S级电能表

-

即日-1.14火热报名中>> OFweek2025中国智造CIO在线峰会

-

即日-1.20限时下载>>> 爱德克(IDEC)设备及工业现场安全解决方案

-

即日-1.24立即参与>>> 【限时免费】安森美:Treo 平台带来出色的精密模拟

推荐专题

分享

分享

发表评论

请输入评论内容...

请输入评论/评论长度6~500个字

暂无评论

暂无评论