创新力Max,英特尔亮出最新产品矩阵

编者按:上周英特尔举办了一场引人注目的“架构日”活动,公布了未来多年的产品技术路线图、技术战略规划以及一系列新技术,新加入英特尔的业界大神Raja Koduri 、Jim Keller以及英特尔首席工程技术官Murthy Renduchintala也纷纷登台演讲并极为罕见地一起接受了外媒Anandtech的问答采访。在这里,我们摘译了当中一部分报道和访谈,向大家介绍一下英特尔的最新技术布局,还有英特尔高层对自己技术产品的一些评价。

英特尔被世人熟知的是CPU,存储,还有近年来收购的FPGA、但其实在GPU方面,也有不错的表现。过去通过在其CPU中集成显卡,英特尔已经在这方面完成了深厚的技术积累,但他们最近又宣布了其独立显卡计划,这将和3D封装等技术一起,共同构成英特尔未来角逐市场的、极具竞争力的产品矩阵。

独立显卡:英特尔的新“武器”

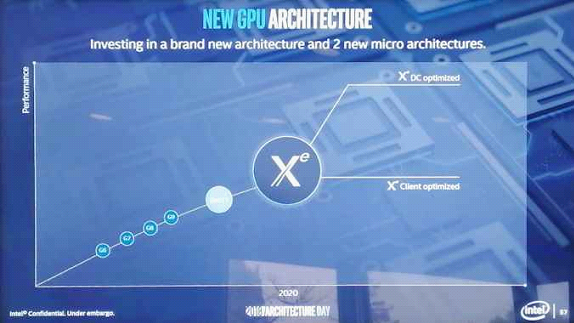

我们并不满足于仅仅谈论2019年将带来什么,我们还看到了英特尔在2020年将如何应对其显卡业务。就在此时,Raja宣布了英特尔独立显卡业务的新产品品牌:

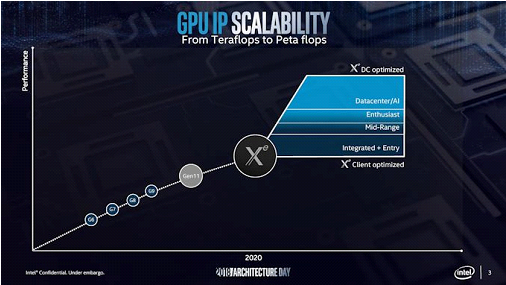

英特尔将使用Xe品牌为它的一系列显卡命名,这些显卡在之前的讨论中被非正式地称为“Gen12”。Xe将从2020年开始,覆盖从客户端显卡到数据中心显卡解决方案的所有领域。

英特尔实际上对这个市场进行了细分,这表明Xe也涵盖了未来的集成显卡解决方案。如果从这张幻灯片判断,英特尔似乎希望Xe覆盖从入门级到中档、再到发烧友、再到人工智能等诸多领域,与竞争对手最好的产品竞争。

英特尔表示,Xe将从10nm技术开始,并将遵循英特尔的单栈软件(single stack software)理念,因此英特尔希望软件开发人员能够利用CPU、GPU、FPGA和AI,所有这些都使用一套API。这款XE设计将为几代显卡奠定基础,并表明英特尔现在已经准备好围绕一个品牌向前发展。

其中一张幻灯片存在一些混淆,因为英特尔可能会使用新的品牌名称来引用它的一些FPGA和AI解决方案。我们要看看到时候能否得到答案。

延续摩尔定律的新方法:3D封装

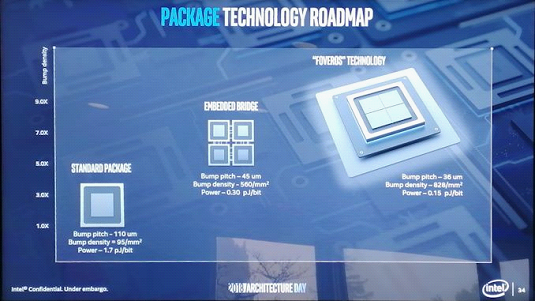

在半导体领域做过大量芯片设计的人都应该清楚,目前生产的大多数CPU和SoC都是基于单片裸片,单芯片内部已经具备了所需要的全部功能,然后放进一个封装里,进入一个系统。更罕见的是多芯片封装,多个芯片通过共享连接放在一个封装中。除此之外,我们还看到了内插器或嵌入式桥接器,旨在将不同的芯片与高速互连结合在一起。现在,英特尔已准备好将3D堆叠引入大众市场。

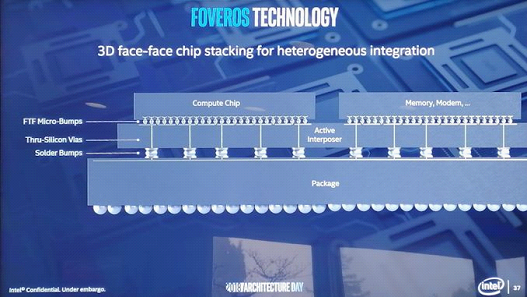

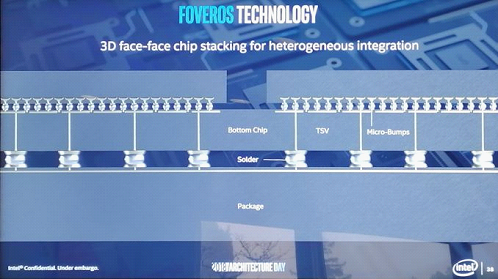

现代芯片设计面临的最大挑战之一是最小化裸片面积。小裸片可以降低成本,通常也可以降低耗电成本,并且可以使之更容易在系统中实现。然而,当涉及到提取性能时,我们却正处于微缩的极限,大型单片裸片,甚至是多芯片封装的一个缺点是内存太远了。英特尔现在已准备好谈论其Foveros技术,该技术包括以小的形式将不同技术结合在一起的有源内插器(active interposer)。

Foveros:显然是希腊语中“了不起”的意思

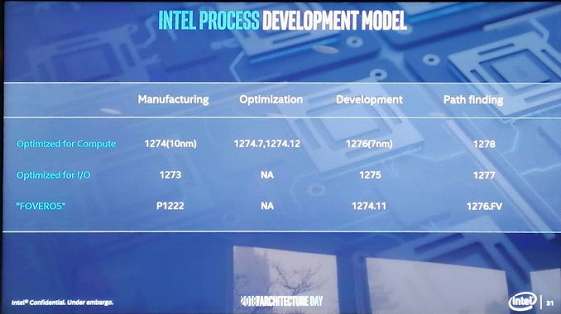

Raja介绍这项技术的方式是从讨论工艺技术开始的。英特尔多年来一直专注于高性能工艺节点,试图从其高性能核心中提取尽可能多的性能。除此之外,英特尔还以类似的节奏运行IO优化的工艺节点,但更适合PCH或SoC-type的功能。

126x和127x是英特尔工艺节点技术的内部编号系统,尽管他们没有区分BKM更新的“+”节点变体。但问题是,英特尔已经知道,它需要根据所需晶体管的类型、性能和功率进行某些流程优化。下一步,英特尔将扩大其节点基础,以便覆盖更多的功率和性能点。

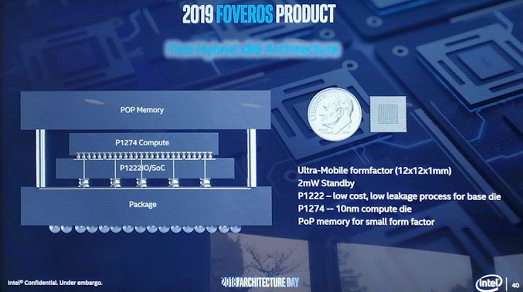

因此,在这个例子中,Raja推出了2019年的工艺技术。对于制造工艺,计算在10nm上有1274工艺,IO有1273工艺(14nm),而这个新的特殊Foveros技术是P1222下的。除了制造方面,英特尔还将致力于制造节点的计算方面的优化。此外,还将对未来节点技术进行一系列开发。这里的目标是,每种类型的晶体管用例可以是不同的,并且没有一种适用于所有类型的方法。

解决这个问题的一种方法是通过芯片集和封装。通过为每种情况下的工作选择最佳晶体管,无论是CPU、GPU、IO、FPGA、RF,还是其他任何东西,只要有正确的封装,就可以将其组合在一起,从而获得最佳的优化效果。

所以这就是Foveros所适用的地方。Foveros是英特尔新推出的有源内插器(active interposer)技术,这种设计是超越自身EMIB设计的一步,适用于小型实现或具有极高内存带宽要求的实现。对于这些设计来说,数据传输的每比特功率非常低,但封装技术必须处理降低的凹凸间距、增加的凹凸密度以及芯片堆叠技术。英特尔表示,Foveros已经准备就绪,可以大规模生产。

因此,Foveros “3D”封装听起来像芯片内插器,就像我们在AMD的Fiji或英伟达的高端数据中心GPU上看到的那样。然而,英特尔超越了那些产品正在做的工作,实际上是将内插器作为设计的一部分。内插器包含将电源和数据传送到顶部芯片所需的通硅孔和走线,但它也承载平台的PCH或IO。实际上,它是一个完全工作的PCH,但是有通孔,允许芯片连接在顶部。

这项技术的第一次迭代并不像上面的幻灯片那么复杂,只需使用一组CPU核心连接到下面的PCH,但其想法是,可以选择一些功能放在大型内插器上,这样这些功能就可以从上面的芯片中删除,以节省空间。这也让英特尔在不同的芯片中使用不同的晶体管类型,我们得到的例子是使用一个构建在22FFL工艺节点上的内插器,在顶部裸片上有一组10nm的CPU。在此之上,DRAM是在POP封装中的。听起来很酷对吧?

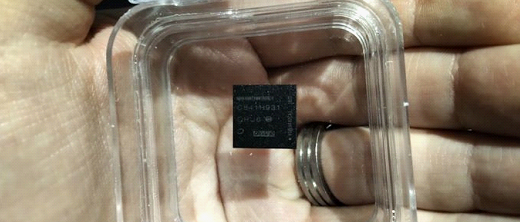

事实上,英特尔在演示区有一两个Foveros芯片。英特尔解释说,这些是x86混合设计,在同一块10nm的硅片上结合了一个大Core和四个较小的Atom核心。我肯定我以前听说过“big.Little”,但我很震惊英特尔真的要这么做!

Hybrid x86 CPU:不错的尝试

也许有人会纠正我,但我不记得哪一次英特尔把多个不同配置的x86核心放在同一块芯片上(是英特尔Edison吗?)。自从ARM开始在智能手机上使用其big.Little设计以来,一个长期存在的问题是,英特尔是否会做类似的事情,无论是将大小凌动核心,还是将高性能的酷睿纳入其中。当英特尔离开智能手机和平板电脑市场时,我们认为这个想法已经不复存在。但是,就像复活的僵尸一样,它已经从坟墓中复活了。我们来看看英特尔的Hybrid x86 CPU。

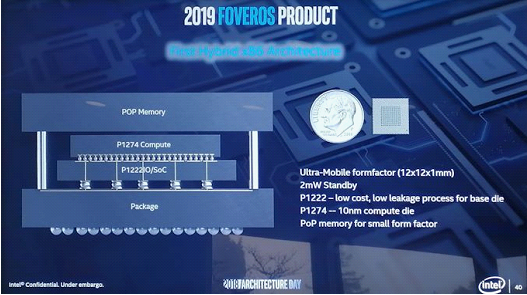

这款小巧的12x12封装采用英特尔的Foveros技术构建,采用22FFL IO芯片作为有源内插器(active interposer),用TSV连接至10nm裸片,其中包含一个Sunny Cove核心和四个凌动(Tremont?)核心。这款小芯片比一美分硬币还小,设计的待机功率为2mW。这种芯片似乎是为移动设备设计的。

此图是制造图。展示了将POP内存放置在Fovoros设计之上以提供最终产品的想法。非常像移动芯片。

英特尔展示的演示系统看起来与以前的Sunny Cove设计相似,但是这个散热器更小,并且有几个不同的连接器。我们被告知这个芯片将支持PCIe for M.2以及UFS,这两者都可以在移动设备上找到。这块主板上也有几个SIM卡连接器。

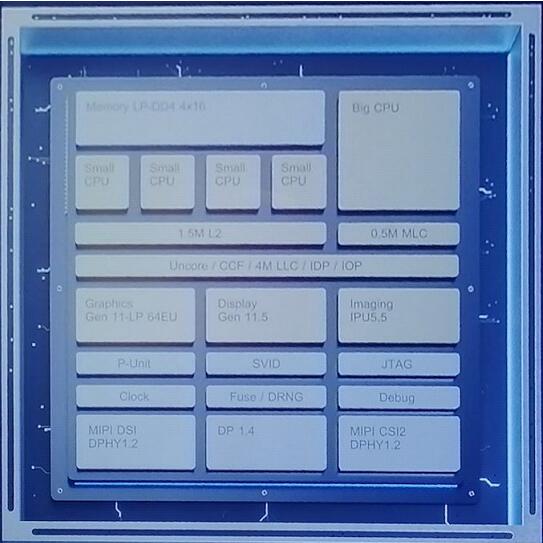

然而,关键部分是这张英特尔幻灯片上的框图。在这里,我们看到一个带有0.5 MB专用中型缓存的“Big CPU”,四个带有共享1.5 MB L2缓存的“Small CPU”,一个具有4MB最后一级缓存的非核心,一个支持LPDDR4的四通道内存控制器(4x16位),一个带有Gen11核显的64 EU设计,Gen 11.5显示控制器,新的IPU,支持DisplayPort 1.4的MIPI,所有这一切都在一个小型封装中。

不过说真的,这有可能成为英特尔的一大收入来源。他们制造的这款芯片可以让核心在不使用时进入C6休眠状态,裸片尺寸小于12x12mm(144 mm2),并面向7W以下的无风扇设备市场。这是一个大Core,四个Atom核心和一个GT2 64 EU设计。

英特尔实际上说,这个产品的出现是因为一个客户要求一款性能与之相当,但待机功率为2mw的产品。为了做到这一点,英特尔在公司内部创造并改进了一些技术。最终产品显然是这个客户的理想选择,但芯片也可供其他OEM使用。

从我们与英特尔高管的问答环节中可见,这项技术显然还处于起步阶段,英特尔现在有了一个新的玩具可以玩。Jim Keller表示,在内部,他们正在尝试使用这项技术的许多新东西,看看哪些是可行的,什么会成为一个好产品,因此,到2019年和2020年,我们应该会看到更多的Foveros设计。

英特尔高管对10nm进度、Foveros等问题的回应

问:英特尔的许多CPU微架构都受到了工艺节点技术延迟的影响。出了什么问题?采取了哪些措施来确保这种情况不会再发生?

Raja Koduri/Jim Keller:我们的产品与晶体管能力是两回事。英特尔拥有惊人的IP,但它们都位于10nm工艺节点。如果我们在14nm上使用它,那么我们在14nm上会有更好的性能。我们在公司内部采用了一种新的方法来将IP与工艺技术分离。你需要知道顾客购买的是产品,而不是晶体管系列。AMD在苦苦挣扎的时候,为了改变设计方法,也经历了同样的转变。在苹果,这种方法被称为“总线”(Bus)方法。

Murthy Renduchintala:这代表了我们作为一家公司过去考虑工艺节点技术的方式。这是公司向前发展的“框架记号”(限制因素)。我们已经了解了很多关于把它应用到14nm的知识。我们现在必须确保我们的IP不是节点锁定的。IP在多个节点之间的可移植性对于应急计划非常重要。我们将继续在我们的设计中大胆冒险,但我们也会有应急策略。我们需要尽可能多的无缝路线图,以备不时之需,并确保在需要时尽快执行这些路线图,以符合客户期望。你将看到未来的节点技术,如10/7nm,比以前有更多的重叠,以保持设计的流畅性。如果我们的产品设计不局限于10nm,那么我们在14nm上的产品组合可能会更好。

问:我们是否会在高端市场看到10nm单片台式CPU?

Raja Koduri:是的。

问:10nm怎么样了?它有变动吗?

Raja Koduri:它正在改变,但并没有变动。从英特尔开始应对的过程中学到了很多经验教训。我们在制造和设计之间建立了一个更好的模式。我们需要在产品和工艺节点上有好的抽象概念。当一切进展顺利时,这个问题并没有显现出来,所以也不是问题。当过程中发生了一些不好的事情时,就会变得复杂起来,因此道路也被堵住了。其他家用抽象的方法解决了这个问题。我们需要确保这种情况不会再次发生,我们希望在路线图中建立弹性。

问:是否有结合CPU/GPU/AI/FPGA做混合SoC的计划?

Raja Koduri:在我们的路线图中会结合可扩展矢量/矩阵。我们的客户需要的是可扩展的解决方案。无论什么样的芯片,客户都需要类似的编程模型。

问:聘请Raja、 Jim,并将外部人员引进英特尔有什么影响?

Murthy Renduchintala:英特尔极具创新精神。我们希望增加这种化学反应,确保我们引进了解英特尔并能带来创新的好想法的人。因为我们需要慎重看待市场竞争也要确保英特尔具备竞争力。通过让有经验的人参与进来,我们确保不断挑战自身执念和现状,从而平衡内部争论。这显示了英特尔吸纳外部想法的能力。我们在外面争取最好的人,因为我们需要他们加入,与内部最优秀的人协作。

问:英特尔目前的5G策略是什么?

Murthy Renduchintala:我们考虑的5G涵盖了数据中心、网络、边缘、设备。英特尔认为,向5G的过渡及其对网络的影响,在加速数据和催化软件定义网络方面,与从模拟向数字的飞跃一样具有变革意义,届时定制芯片将被容器技术取代。它将加速网络的“云化”。边缘非常重要,尤其是为了最大限度减少新服务的延迟,亚毫秒级延迟对于这些服务来说非常关键。无线接口也很重要。智能云领域将成为驱动这些行业飞快发展的“飞轮”。我们在11月份提到,XMM 5G调制解调器将在2019年下半年交付给合作伙伴,并在2020年初推出产品。它是一种多模5G LTE架构,支持全部3个毫米波频段和6 GHz以下频率。

问:由于Thunderbolt 3需要额外的芯片,你对未来OEM的采用怎么看?

Murthy Renduchintala:集成Type-C Thunderbolt 3是第一代。我们会在未来改进它,这是这项技术的自然谱系。我们在不断思考有多少集成在芯片中,有多少留在电路板上。

Raja Koduri:这是一个巨大的IP挑战,不仅对Thunderbolt 3如此,对其他IP也是如此。集成PHY(端口物理层)很重要。例如,通过分解FPGA阵列中的收发器,我们可以将大量精力放在解耦的IP上。

问:在Foveros的演示中,该芯片结合了基于酷睿微架构的大型x86内核和基于凌动微架构的小型x86内核。我们能否期待未来大核和小核具有相同ISA总线标准?

Raja Koduri:我们正在努力。它们必须拥有相同的ISA总线标准吗?Ronak和他的团队正在研究这个问题。但是,我认为我们的目标是让软件尽可能地简单,以便开发人员和客户使用。这是我们的架构师为确保此类产品顺利进入市场所面临的挑战。明年我们还将对这类产品的封装进行讨论。你今天看到的芯片,虽然它最初主要是为特定客户设计的,但它不是定制的产品,从这个意义上讲,它将适用于其他OEM。

Murthy Renduchintala:我们已经迈出了第一步。第一步是飞跃,下一步是渐进。正如我们所说的One API策略,如果我们将API一致化,那么它将适用于我们所有的CPU。Foveros也是一种新的部件/产品,它表明我们的产品组合中有一个空白,并帮助我们创建了解决问题的技术,我们希望在未来通过新IP扩展这一领域。

问:在Foveros上的尝试如何?

Jim Keller:Raja在负责GPU,因此他对计算元素之间的高带宽连接很感兴趣。这是一项新技术,我们也在进行一些试验。试验之路充满曲折,我们在实现堆叠技术的前一年就达到了这一行业电流密度的极限,所以为了提高堆叠的性能,我们在不同的领域做了很多尝试。如果依然不可行,那么就没有必要使用这项技术。但是我们很开心地尝试着,乐此不疲,在接下来的5年里,我们会在很多地方看到Foveros。我们将为自己甚至还不知道的问题找到新的解决办法。

图片新闻

技术文库

最新活动更多

-

1月8日火热报名中>> Allegro助力汽车电气化和底盘解决方案优化在线研讨会

-

1月9日立即预约>>> 【直播】ADI电能计量方案:新一代直流表、EV充电器和S级电能表

-

即日-1.16立即报名>>> 【在线会议】ImSym 开启全流程成像仿真时代

-

即日-1.20限时下载>>> 爱德克(IDEC)设备及工业现场安全解决方案

-

即日-1.24立即参与>>> 【限时免费】安森美:Treo 平台带来出色的精密模拟

-

即日-1.31立即参与>>> 【限时免费下载】村田白皮书

推荐专题

分享

分享

发表评论

请输入评论内容...

请输入评论/评论长度6~500个字

暂无评论

暂无评论