嵌入式硬件通信接口协议-IIC(二)分层架构设计模拟接口

2019-02-18 10:19

掘芯

关注

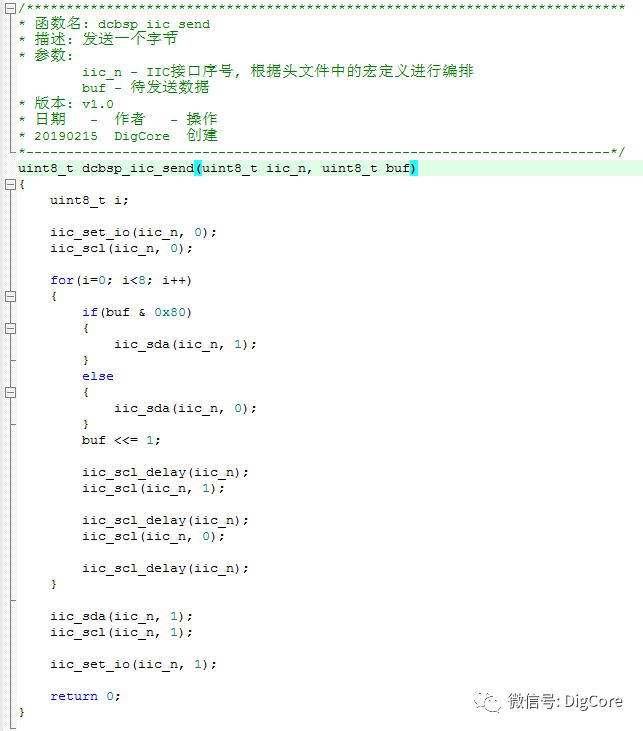

数据输出

如上示例发送一个16进制数据0xDC的时序示意图,最重要的原则是:SCL为低电平时,才可以改变SDA输出数据;SCL为高电平时,必须SDA不抖动不改变。

代码实现的过程,类似于SPI模拟时类似,数据位“踩着”时钟逐bit被输出,每输出一bit就要对数据进行移位“buf <<= 1;”,这样在下一个SCL低电平时候输出下一个bit。

完成输出后立即对SDA的IO管脚设为输入模式,即调用iic_set_io(iic_n, 1);函数来实现。

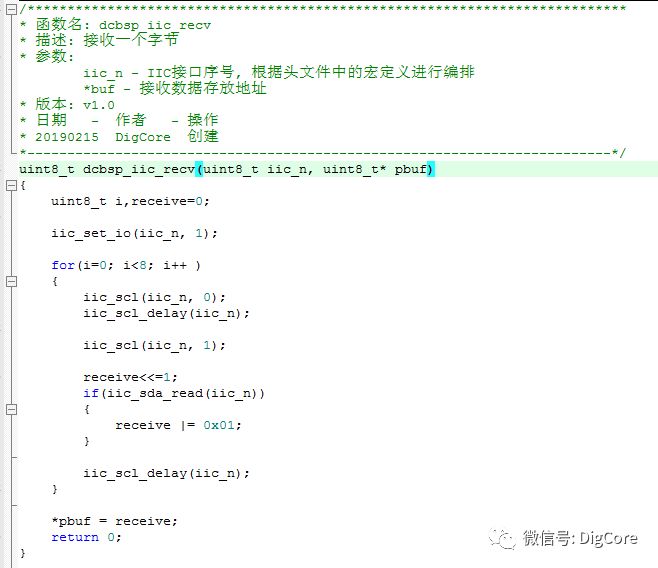

数据采样

类似于数据发送,逐bit踩着SCL接收。这里的数据采样,就是IIC主机接收来自外设器件发来的数据,最重要的原则是:SCL为低电平时,做延时等待保证SDA数据稳定;SCL为高电平时,读取SDA的IO管脚电平。

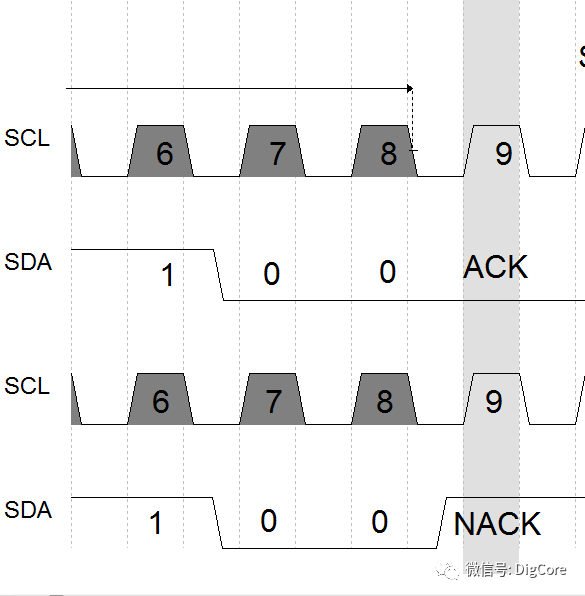

应答ACK/NACK

从时序图可以看到,应答位的ACK和NACK区别在于,第9个SCL高电平期间,SDA所呈现的电平状态不同。

从上篇文章我们可以知道,IIC总线的电路连接,一般地SCL和SDA都有上拉电阻Rp,也就是说如果IIC从机设备,由于不存在(硬件未焊接)、出故障(烧坏)或者其他原因,导致没有信号产生的时候,此时SDA会处于NACK的状态,也就是IO管脚电平被上拉电阻拉高了,可以理解为“默认”电平,没有“回应”。

声明:

本文由入驻维科号的作者撰写,观点仅代表作者本人,不代表OFweek立场。如有侵权或其他问题,请联系举报。

图片新闻

最新活动更多

-

4月16日预约观看>> 开发前服,优化项目投资价值 筑牢落地关键防线

-

4月22日立即报名>> 【在线会议】ADI六款仪器仪表方案助力产品快速上市

-

4月23日立即报名>> 【直播】 智测未来·2026海克斯康春季产品创新日

-

5月13日立即预约>>> 【线下会议】恩智浦创新技术峰会·深圳

-

5月14日立即下载>> 【白皮书】村田室内外定位解决方案

-

即日-5.20立即下载>> 【限时免费】物理场仿真助力生物医学领域技术创新

分享

分享

发表评论

登录

手机

验证码

手机/邮箱/用户名

密码

立即登录即可访问所有OFweek服务

还不是会员?免费注册

忘记密码其他方式

请输入评论内容...

请输入评论/评论长度6~500个字

暂无评论

暂无评论