嵌入式硬件通信接口协议-IIC(二)分层架构设计模拟接口

应答的目的,就是“接收方”告知“发送方”,我已正常收到刚刚发来的数据。

等待应答ACK

既然是应答,就有两向性:IIC从机应答IIC主机;IIC主机应答IIC从机。

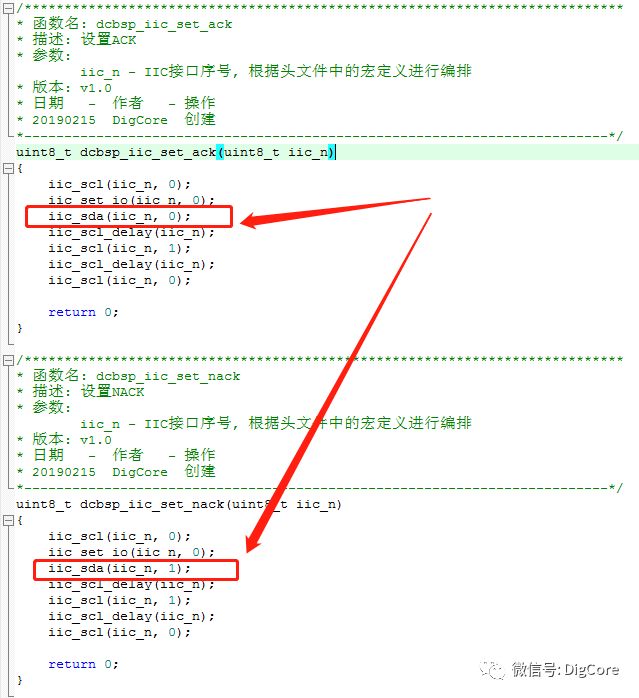

上图的应答ACK/NACK都是IIC主机主动输出的,是用来告知从机“我主机已正常收到”。

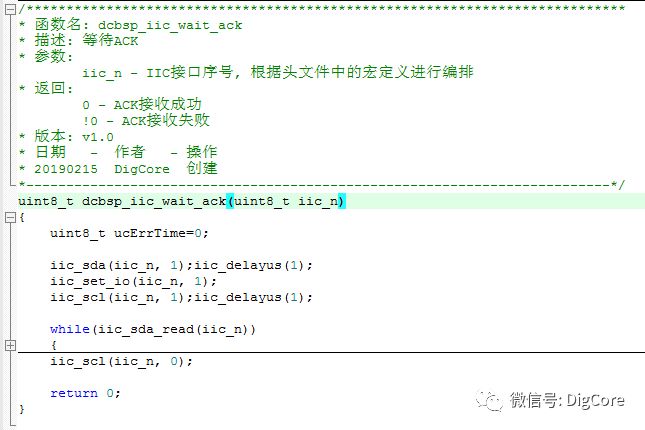

而IIC从机告知主机的应答ACK,这里要用等待ACK的概念,主机通过读取SDA管脚电平来检测ACK信号。

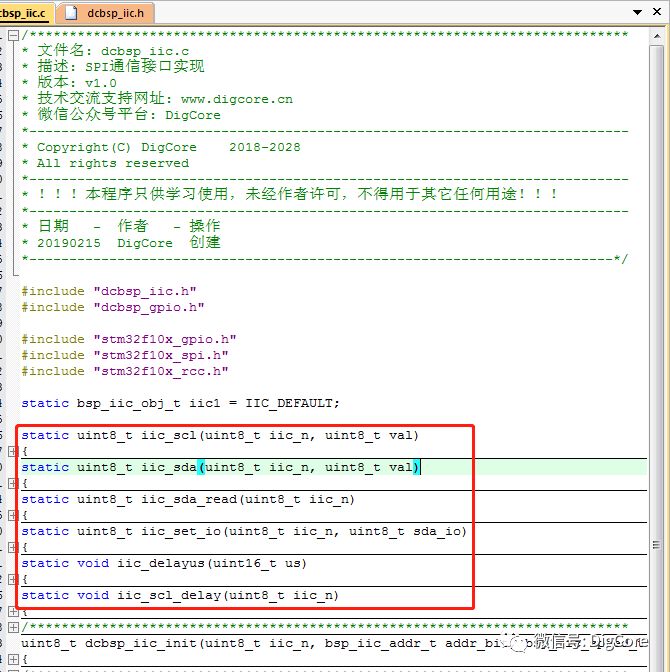

以上是利用GPIO管脚模拟实现的时序,封装成DigCore_Embed嵌入式软件架构的BSP层接口,对上层提供IIC硬件接口,向下操作GPIO和时序的模拟。移植过程中可以根据目标平台,在上述这些已经封装好的接口内,做适当调整。

比如采用官方Demo程序代替GPIO模拟方案,只需要修改这以上接口中的代码即可,对于上层应用库,不论是温湿度传感器SHT20,还是EEPROM存储芯片AT24C1024B,甚至是BS81163-A的触摸键盘芯片,这几个使用了BSP层的IIC接口,这些代码都无需改动。

这就是嵌入式软件的分层设计思想的优势。

以上函数内部所调用的接口,都是当前BSP层里IIC模块源码中的静态函数:

总结,IIC时序的模拟,主要思路是根据IIC时序特点,在对应的信号后面做对应的时延,以达到时序的展现!难点之处就是把IIC时序拆解成多个信号特征进行模拟时,如果对信号时序图了解不深,在对比代码时比较绕,需要静下心仔细核对!

以上代码仅仅完成初步的编写和整理,未在具体外设上验证。此BPS层的IIC模块最终源码,敬请期待下回分享出来!

图片新闻

最新活动更多

-

4月16日预约观看>> 开发前服,优化项目投资价值 筑牢落地关键防线

-

4月22日立即报名>> 【在线会议】ADI六款仪器仪表方案助力产品快速上市

-

4月23日立即报名>> 【直播】 智测未来·2026海克斯康春季产品创新日

-

5月13日立即预约>>> 【线下会议】恩智浦创新技术峰会·深圳

-

5月14日立即下载>> 【白皮书】村田室内外定位解决方案

-

即日-5.20立即下载>> 【限时免费】物理场仿真助力生物医学领域技术创新

分享

分享

发表评论

登录

手机

验证码

手机/邮箱/用户名

密码

立即登录即可访问所有OFweek服务

还不是会员?免费注册

忘记密码其他方式

请输入评论内容...

请输入评论/评论长度6~500个字

暂无评论

暂无评论