3nmЕФаОЦЌеНељЃЌВХИеИеПЊЪМ

ВЛЙмЯВВЛЯВЛЖНёФъЕФ iPhone 15ЃЌДѓИХЖМЛсШЯПЩвЛМўЪТЃЌКмЖрШЫбЁдёЙКТђ iPhone 15 Pro ЯЕСаЕФвЛДѓЖЏЛњЃЌОЭЪЧГхзХЬЈЛ§Еч 3nm ЙЄвеЕФ A17 ProЁЃ

A17 Pro ВЩгУСЫЬЈЛ§ЕчзюаТЕФ 3nm ЙЄвеЃЈN3BЃЉжЦдьЃЌОЇЬхЙмЪ§СПДяЕНСЫОЊШЫЕФ 190 вкЃЌетЪЧШЋЪРНчЕквЛПюВЩгУЬЈЛ§Еч 3nm ЙЄвеЕФЪжЛњаОЦЌЃЌвВЪЧ 3nm ЙЄвеЕквЛДЮГіЯжЦеЭЈШЫОЭПЩвдТђЕНЕФДѓжкЯћЗбЦЗЩЯЁЃ

вЊжЊЕРЃЌЫцзХаОЦЌГпДчдНРДдНБЦНќЮяРэМЋЯоЃЌУПвЛДњЙЄвеНкЕуЩ§МЖашвЊЭЖШывВдкМгЫйдіМгЃЌНіЬЈЛ§ЕчвЛМвЕФ 3nm аТдіЭЖШыОЭГЌЙ§СЫ 200 вкУРдЊЁЃ

ОоДѓЕФЭЖШывтЮЖзХОоДѓЕФГЩБОЃЌгШЦфЪЧдкЧАЦкЙЄвеЩаВЛГЩЪьЁЂСМТЪНЯЕЭЕФЧщПіЯТЃЌУЛгаЖрЩйаавЕКЭЙЋЫОФмЙЛИКЕЃ 3nm аОЦЌЕФжЦдьГЩБОЁЃ

етЦфжаЃЌжЧФмЪжЛњвЛжБЪЧзюгаЪЕСІКЭЖЏСІЭЦЖЏЯШНјжЦГЬЙЄвеВЛЖЯЧАНјЕФСІСПЁЃ

вЛЗНУцЪЧвђЮЊжЧФмЪжЛњашвЊдкМЋаЁЕФФкВППеМфРяШћЯТЫуСІОЊШЫЕФаОЦЌЃЌЭЌЪБЛЙвЊМЋПЩФмНЕЕЭаОЦЌЕФЙІКФКЭЗЂШШЃЛ

ЭМ/ЦЛЙћ

СэвЛЗНУцЪЧаОЦЌжЦдьЬЋЩеЧЎЃЌвВжЛгавЛФъОЭФмТєГіЪЎЖрвкЬЈЕФжЧФмЪжЛњПЩвдаЮГЩЙцФЃаЇгІЃЌВЛЖЯЭЦЖЏЯШНјжЦГЬИФНјЙЄвеЁЂЬсИпСМТЪЃЌЕУвдШУЗўЮёЦїЁЂPCЁЂгЮЯЗжїЛњЩѕжСЪЧЦћГЕгУЩЯИќЯШНјЕФаОЦЌжЦдьММЪѕЁЃ

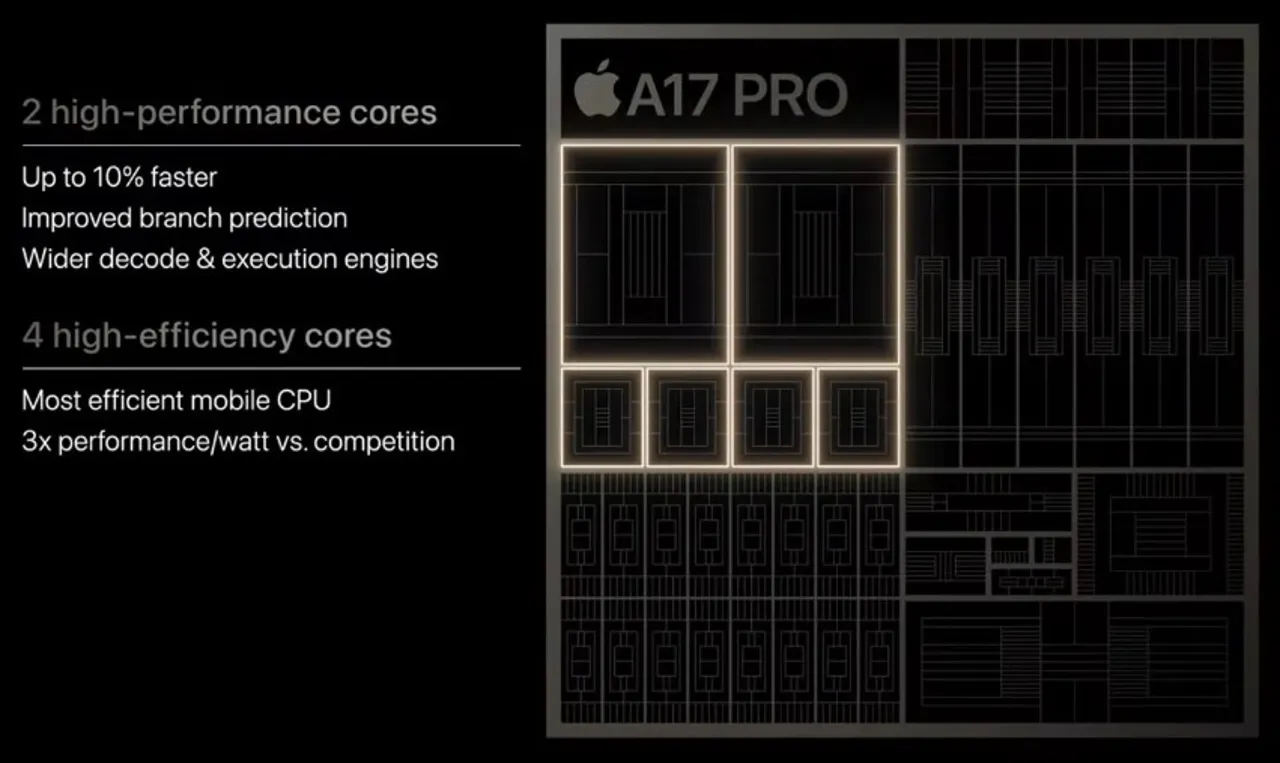

ЕЋИќДѓЕФЭЖШыЁЂИќЯШНјММЪѕЪЧВЛЪЧОЭЕШЭЌгкЁИе§ШЗЁЙЃППЩФмвВЮДБиЃЌiPhone 15 Pro ЯЕСаЕФЩЂШШЗчВЈЛЙУЛгаЙ§ШЅЃЌЙигкСМТЪЛђепЫЕГЩБОЕФПНЮЪЃЌвВвЛжБЪЧ 3nm ЩЯПеЕФЁИЮкдЦЁЙЁЃ

СМТЪКЭГЩБОЃЌ3nm ЕФвЛЖфЁИЮкдЦЁЙ

10 дТ 9 ШеЃЌЁЖПЦДДАхШеБЈЁЗв§ЪівЕФкаавЕЗжЮіГЦЃЌШ§аЧЁЂЬЈЛ§ЕчЕФ 3nm ЙЄвеСМТЪФПЧАЖМдк 50%зѓгвЁЃвЛЮЛНгНќШ§аЧЕФШЫЪПЛЙЭИТЖЃЌвЊгЎЕУИпЭЈЕШДѓПЭЛЇУїФъЕФ 3nm вЦЖЏаОЦЌЖЉЕЅЃЌСМТЪжСЩйашвЊЬсИпЕН 70%ЁЃ

дкАыЕМЬхжЦдьЩЯЃЌСМТЪжБНгвтЮЖзХвЛећЦЌМгЙЄГіРДЕФОЇдВЩЯФме§ГЃЙЄзїЕФаОЦЌЕФеМБШЁЃЭЈГЃРДЫЕЃЌвЛЦЌОЇдВЩЯПЩвдЭЌЪБжЦдьГіЩЯАйПХЭЌбљЕФТуаОЦЌЃЌжЎКѓНЋОЇдВЦЌЩЯЕФТуаОЦЌЧаИюПЊРДЃЌОЭПЩвдЗтзАКѓАВзАЕНВњЦЗЩЯЁЃ

ЭМ/ЬЈЛ§Еч

дкГЩЪьЙЄвеЩЯЃЌДњЙЄГЇЕФСМТЪвЛАуЖМФмДяЕН 99%ЃЌЕЋдкЯШНјжЦГЬЩЯЃЌгЩгкЙЄвеФбЖШКЭЧАЦкЕФДѓСПЮЪЬтЃЌСМТЪОЭПЩФмЗЧГЃЕЭЁЃЕЋАДееЙпР§ЃЌДњЙЄГЇВЂВЛИКд№ГаЕЃВЛСМаОЦЌЕФжЦдьГЩБОЃЌетВПЗжЗбгУЛЙЪЧгЩаОЦЌЩшМЦПЭЛЇГаЕЃЃЌБШШчЦЛЙћЁЂгЂЮАДяЁЃ

ЕБШЛЃЌЁИ50%ЕФСМТЪЁЙЮДБиПЩаХЃЌДЫЧАОЭгаДѓСПИїжжРДдДЕФаХЯЂИјГіСЫИїВЛЯрЭЌЕФСМТЪЃЌАќРЈ A17 Pro ДгВњвЕСДДЋГіЕФСМТЪОЭЮЊ 70-80%ЁЃЕЋетаЉЯћЯЂЮовЛР§ЭтЃЌЖМЭИТЖГівЛИіЙиМќаХЯЂЃЌМД 3nm ЕФСМТЪКмЕЭЁЃ

СМТЪдНЕЭЃЌГЩБОдНИпЁЃ

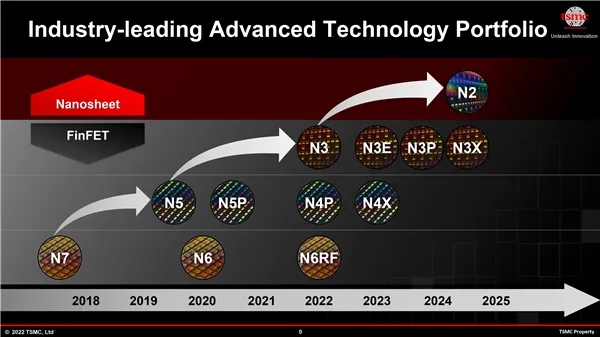

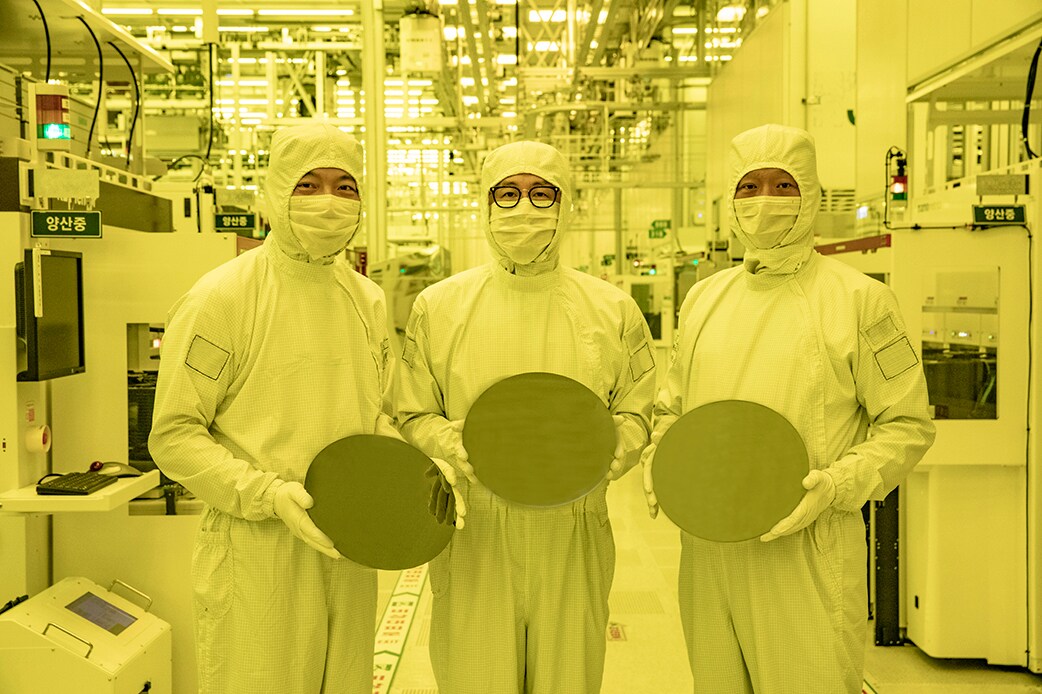

етвВЪЧЮЊЪВУДГ§СЫЦЛЙћЃЌЦфЫћЫљгажївЊаОЦЌЩшМЦЙЋЫОЖМУЛгабЁдёдк 2023 ФъетИіНкЕуВЩгУ 3nm ЙЄвеЃЌИќЖрЛЙЪЧУщзМ N3B жЎКѓЕФЙЄвеЁЃАДееЬЈЛ§ЕчдчЧАЕФЙцЛЎЃЌЬЈЛ§Еч 3nm ЙЄвеЦфЪЕЪЧАќРЈ N3BЃЈМД N3ЃЉЁЂN3EЁЂN3PЁЂN3X ЕШЖрИіАцБОЁЃ

ЬЈЛ§ЕчжЦГЬТЗЯпЭМЃЌЭМ/ЬЈЛ§Еч

ЩѕжСдквЕНчДЋЮХжаЃЌОЭСЌЦЛЙћвВЪЧгыЬЈЛ§ЕчЧЉЖЉСЫвЛЗнЁИЖдЖФЁЙавщЃЌЙцЖЈЮДРДвЛФъЬЈЛ§Еч N3B ЙЄвеЮЊЦЛЙћзЈгУЃЌЧвЗЯЦЌОљгЩЬЈЛ§ЕчГаЕЃГЩБОЃЌЖјЗЧЦЛЙћТђЕЅЁЃ

ЖјШчЙћЫЕСМТЪКмДѓГЬЖШЩЯОіЖЈСЫ 3nm ЕФГЩБООгИпВЛЯТЃЌНјЖјЬсИпСЫаОЦЌЩшМЦЙЋЫОЕМШыЕФУХМїЃЌФЧ 3nm ЕФЙІКФКЭЗЂШШЮЪЬтЃЌвВЪЧзшжЙЫћУЧНЯдчЕМШыЕФЙиМќдвђЁЃ

ЗЂШШКЭЙІКФЃЌ3nm ЕФСэвЛЖфЁИЮкдЦЁЙ

iPhone 15 Pro ЯЕСаЕФЗЂШШЮЪЬтетРяОЭВЛдйзИЪіСЫЃЌЮвУЧжЎЧАОЭдкЮФеТжаЗжЮіЃЌiPhone 15 Pro ЯЕСаЗЂШШЕФЁИзяП§ЛіЪзЁЙОЭЪЧЩшМЦКЭаОЦЌСНДѓВПЗжЃЌКѓепздШЛОЭЪЧВЩгУ 3nm ЙЄвеЕФ A17 ProЁЃ

ЬЙТЪЕиЫЕЃЌiPhone 15 Pro ЕФЗЂШШЕНЕзгаЖрДѓГЬЖШЪЧвђЮЊ A17 ProЃЌA17 Pro ЕФЮЪЬтгаЖрДѓГЬЖШЪЧвђЮЊЬЈЛ§Еч N3 ЙЄвеЃЌФПЧАРДНВЖМЛЙУЛгаБШНЯЧаЪЕЕФТлЖЯЁЃ

ЕЋЮЪЬтвЛЖЈЪЧгаЕФЁЃАДееЦЛЙћИјГіЕФЪ§ОнЃЌA17 Pro ЕФОЇЬхЙмЪ§СПЮЊ 190 вкЃЌБШЧАДњ A16 діМгСЫНќ 20%ЃЌCPU адФмШДжЛЬсЩ§СЫдМ 10%ЃЌGPU КЫаФЪ§Дг 5 ИідіМгЕН 6 ИіЕФЭЌЪБЃЌЗхжЕадФмЬсЩ§СЫ 20%ЁЃВЛЙ§АДее GeekBench Ъ§ОнРДПДЃЌЗхжЕадФмДѓЗљЬсИпЕФСэвЛУцЃЌЪЧ A17 Pro TDP ЗхжЕЙІТЪДяЕНСЫОЊШЫЕФ 14WЁЃ

ЭМ/ЦЛЙћ

етВЛжЛЪЧЦЛЙћКЭЬЈЛ§ЕчУцЖдЕФЮЪЬтЁЃ

ЫцзХОЇЬхЙмГпДчВЛЖЯБЦНќЮяРэМЋЯоЃЌСПзгЫэДЉаЇгІДјРДЕФЮЪЬтвВдНЗЂбЯжиЃЌЪЇПиЕФЕчзгв§ЗЂЕФТЉЕчЃЌЛсЕМжТаОЦЌИќбЯжиЕФЗЂШШКЭЙІКФЮЪЬтЁЃЫљвдДг 7nm вдКѓЃЌећИівЕНчЕФЁИжЦГЬНЙТЧЁЙдНЗЂУїЯдЃЌЖдФІЖћЖЈТЩаТГіТЗЕФЬНЫїдНЗЂМгПьЁЃ

ЕБШЛЛиЕН 3nm ЩЯЃЌЬЈЛ§ЕчКЭШ§аЧвВВЛЪЧКСЮозМБИЕФЁЃ

N3E ВХЪЧЬЈЛ§Ечеце§ЕФ 3nmЃЌШ§аЧбКБІ GAA

ЯрБШ A17 Pro ЩЯВЩгУЕФ N3B ЙЄвеЃЌN3E ЪЧЬЈЛ§ЕчМЦЛЎЭЦГіЕФвЛИіЭъШЋВЛЭЌЕФЙЄвеНкЕуЃЌдкЙІКФПижЦЗНУцИќМгРэЯыЁЃ

ЬЈЛ§ЕчВЛНігУЩЯСЫЁИДДаТЕФзшЕВЙЄвеЁЙЃЌИќживЊЕФЪЧ FINFLEX ММЪѕЕФЕМШыЃЌШУаОЦЌЩшМЦШЫдБПЩвддквЛИіФЃзщФкЛьДюВЛЭЌЕФБъзМЕЅдЊЃЌЪЕЯжЭЌЪБгХЛЏадФмЁЂЙІКФКЭУцЛ§ЁЃАќРЈ N3PЁЂN3XЁЂN3AEЁЂN3S ЕШЙЄвеНкЕуЃЌЪЕМЪЖМЪЧ N3E ЕФКѓајБфЬхЁЃ

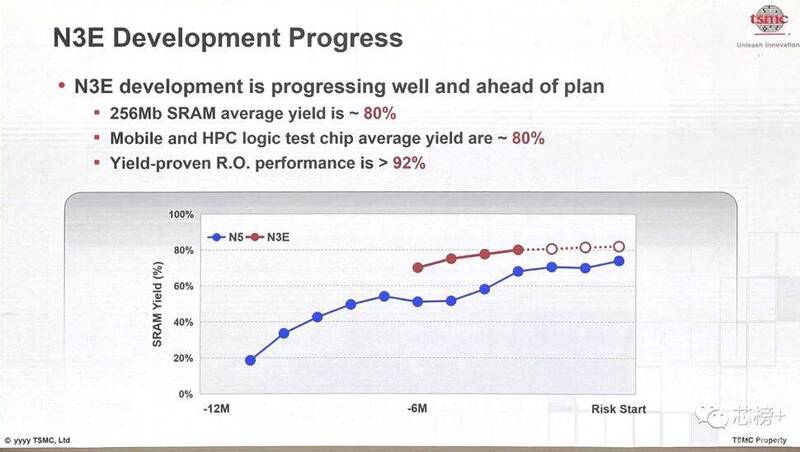

ЖјЧвДгЙ§ШЅАыФъЕФЯћЯЂРДПДЃЌЦеБщжИГі N3E ЕФСМТЪвЊКУгк N3BЃЌвЛЗнЮФМўЯдЪОЃЌN3E 256Mb SRAM ЦНОљСМТЪДяЕН 80%ЃЌMobile гы HPC аОЦЌЕФСМТЪвВДя 80%ЁЃДЫЧАЃЌвВвЛжБДцдкЬЈЛ§ЕчПМТЧЗХЦњ N3B НкЕуЃЌЭЦГйЕН N3E НкЕуе§ЪННјШы 3nm ЕФДЋЮХЁЃ

ЭМ/ЬЈЛ§Еч

9 дТ 7 ШеЃЌСЊЗЂПЦгыЬЈЛ§ЕчЙВЭЌаћВМЃЌСЊЗЂПЦЪзПюВЩгУЬЈЛ§Еч 3 ФЩУзжЦГЬЩњВњЕФЬьчсЦьНЂаОЦЌвбОГЩЙІСїЦЌЃЌИУПюЬьчсЦьНЂаОЦЌНЋгк 2024 ФъЯТАыФъЩЯЪаЁЃЛљБОШЗЖЈЃЌетПюЬьчсЦьНЂаОЦЌЃЈЬьчс 9400ЃЉВЩгУСЫЬЈЛ§Еч N3E ЙЄвеЃЌЖјЙйЗНЭИТЖЃК

ЬЈЛ§Еч N3E ЙЄвеЕФТпМУмЖШЯрБШ N5 ЙЄведіМгСЫдМ 60%ЃЌдкЯрЭЌЙІКФЯТЫйЖШЬсЩ§ 18%ЃЌЛђепдкЯрЭЌЫйЖШЯТЙІКФНЕЕЭ 32%ЁЃ

ЯрБШжЎЯТЃЌШЅФъФъФЉЕФ IEDMЃЈIEEE ЙњМЪЕчзгЦїМўДѓЛсЃЉЩЯЃЌЬЈЛ§ЕчХћТЖ N3B ЙЄвеЪЕМЪжЛНЋ SRAM УмЖШЬсИпСЫдМ 5%ЃЈЯрБШ N5 ЙЄвеЃЉЃЌгыЦфзюГѕЩљГЦЕФ 20% вВЪЧЯрШЅЩѕдЖЁЃ

СэЭтЃЌ9 дТЕзвЕФкгжДЋГігЂЮАДявВЯТЕЅСЫЬЈЛ§Еч 3nm жЦГЬЃЌвдЩњВњ Blackwell ЙЙМм B100 Ъ§ОнжааФ GPUЃЌдЄМЦНЋВЩгУИќВржиадФмдіЧПЕФ N3P Лђ N3X ЙЄвеЁЃ

ПЩвдетУДЫЕЃЌN3E МАЦфБфжжЖдгкДѓЖрЪ§аОЦЌГЇЩЬРДЫЕЃЌВХЪЧеце§ЕФ 3nmЁЃ

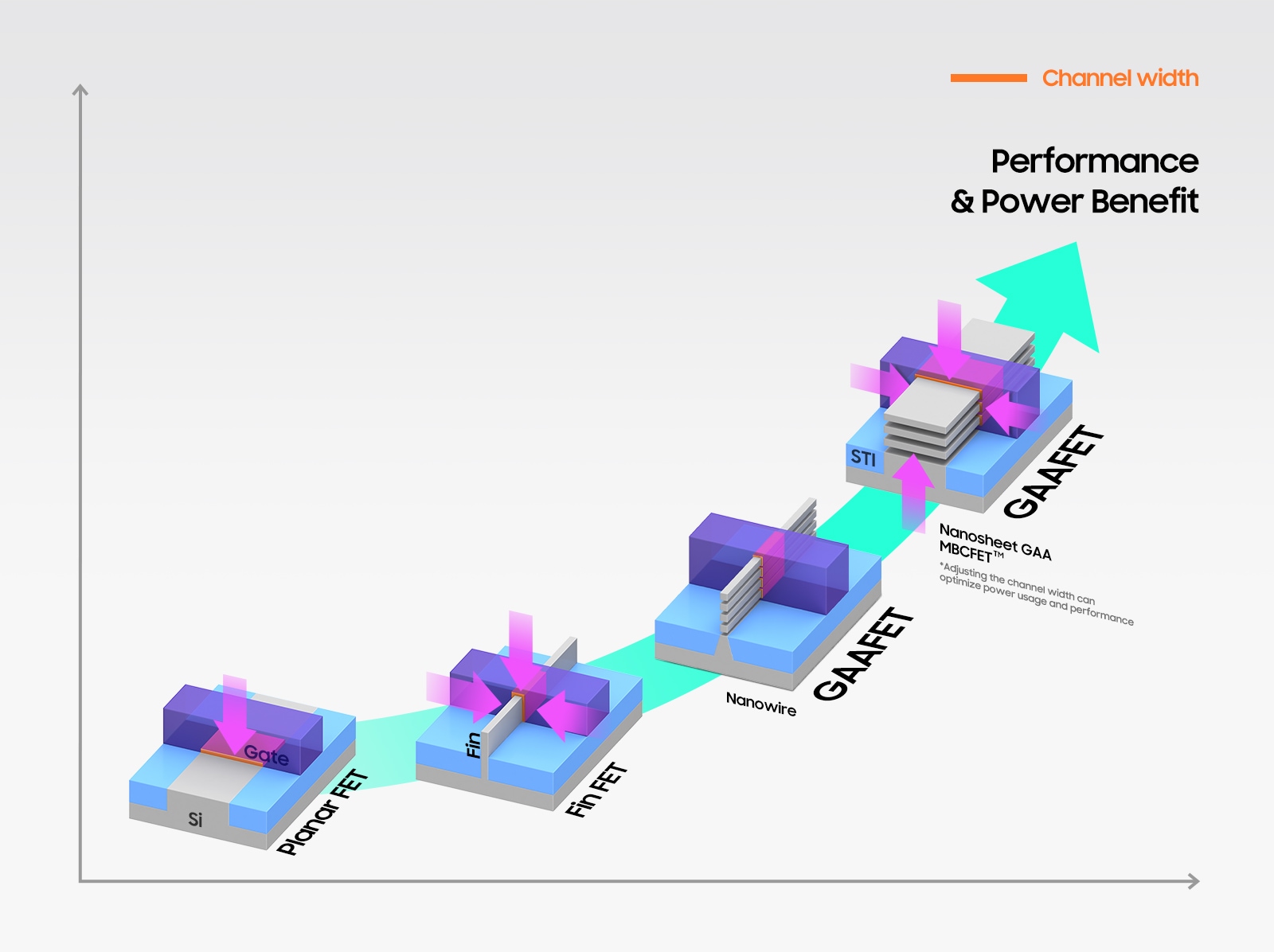

ЖјдкШ§аЧетБпЃЌШЅФъ 6 дТОЭТЪЯШаћВМСЫдк 3nm ГЩЙІгІгУ GAAFET ММЪѕЁЃGAAFET ЕФе§ЪНУћГЦЪЧШЋЛЗШЦеЄМЋОЇЬхЙмЃЈGate-All-Around FETЃЉЃЌМмЙЙЩЯзюУїЯдЕФБфЛЏдкЕЅЮЛУцЛ§ФкЕФРћгУаЇТЪЁЃ

ОЇЬхЙмМмЙЙБфЧЈЃЌЭМ/Ш§аЧ

жкЫљжмжЊЃЌМЦЫуадФмзюЕзВуЦфЪЕОЭЪЧОЇЬхЙмЕФЁИвЛПЊвЛЙиЁЙЃЌДњБэСЫЖўНјжЦжаЕФЁИ0ЁЙКЭЁИ1ЁЙЃЌИќЕзВуЪЧЖдОЇЬхЙмФкЭЈЕРЃЈгжГЦЙЕЕРЃЉЕФПижЦФмСІЁЃFinFET ЕквЛДЮНЋЭЈЕРДгКсЯђзЊЮЊЪњЯђЃЌЖјШ§аЧВЩгУСЫПэЭЈЕРЃЈФЩУзЦЌЃЉЕФ GAAFET ММЪѕЃЌдкЕЅЮЛУцЛ§ФкжЇГжИќЖрЭЈЕРЕФПижЦЃЌгЩДЫЕУвдЪЕЯжСЫЃК

гы 5nm ЙЄвеЯрБШЃЌЕквЛДњ 3nm ЙЄвеПЩвдЪЙЙІКФНЕЕЭ 45%ЃЌадФмЬсЩ§ 23%ЃЌаОЦЌУцЛ§МѕЩй 16%ЃЛЖјЕкЖўДњ 3nm ЙЄведђЪЙЙІКФНЕЕЭ 50%ЃЌадФмЬсЩ§ 30%ЃЌаОЦЌУцЛ§МѕЩй 35%ЁЃЃЈзЂЃКШ§аЧЕкЖўДњ 3nm вВвЊЕШЕНУїФъЁЃЃЉ

ЯрБШЬЈЛ§ЕчЛЙдкгУЕФ FinFET ММЪѕЃЌGAA гЕгаИќКУЕФОВЕчПижЦФмСІЁЃЗЈЙњаХЯЂММЪѕЕчзгЪЕбщЪвИпМЖМЏГЩЙЄГЬЪІ Sylvain Barraud вВжИГіЃКЁИгы FinFET ЯрБШЃЌGAA ЖбЕўЕФФЩУзЯпЛЙОпгаИќИпЕФгааЇЙЕЕРПэЖШЃЌФмЙЛЬсЙЉИќИпЕФадФмЁЃЁЙ

ЪТЪЕЩЯЃЌЬЈЛ§ЕчКЭгЂЬиЖћвВдчдчаћВМНЋдк 2nm НкЕуе§ЪНЕМШы GAA ММЪѕЃЌжЎЫљвдУЛгадк 3nm НкЕуЃЌжївЊЙЫТЧЛЙЪЧММЪѕГЩЪьЖШВЛИпДјРДЕФСМТЪЮЪЬтЃЌШ§аЧ GAA 3nm ДЫЧАОЭЖрДЮДЋГібЯжиЕФСМТЪЮЪЬтЃЌЩѕжСЪЧдкаћВМСПВњКѓевЩЯУРЙњ Silicon Frontline Technology ЙЋЫОЃЌКЯзїЬсИп 3nm GAA ЙЄвеЕФСМТЪЁЃ

ЫљвдЖдШ§аЧРДЫЕЃЌЙиМќЛЙЪЧдкгкБЃГж 3nm GAA ФмаЇгХЪЦЕФЭЌЪБЃЌШчКЮОЁПЩФмЕиЬсИпСМТЪЁЃ

ЙшОЇдВЃЌЭМ/Ш§аЧ

аДдкзюКѓ

ЪБжСНёШеЃЌЫљгаШЫЖМУїАзЃЌдкЮяРэГпДчЩЯМЋЦфЮЂаЁЕФаОЦЌЃЌдкЯжЪЕЪРНчЪЧКЮЕШЕФживЊЃЌЖјаОЦЌЩЯЕФУПвЛДчНјВНЃЌЪЕжЪЩЯвВЛсЭЦЖЏШЋЪРНчЫуСІЕФДѓЗљЬсЩ§ЃЌетвВЪЧЙ§ШЅМИЪЎФъШЫРрПЦММНјВНЕФжївЊЖЏСІжЎвЛЁЃ

гы 1nm жЎКѓЕФЮДРДЯрБШЃЌ3nm ФПЧАгіЕНЕФЮЪЬтМШВЛРЇФбвВВЛвтЭтЃЌОЇдВГЇдчОЭгаЫљдЄЯыКЭзМБИЁЃЕЋМДБуЪЧаОЦЌжЦГЬЮоЯоБЦНќЮяРэМЋЯоЕФМИФъКѓЃЌДгРДвВУЛгаЪВУДЮоНтЕФЮЪЬтЁЃ

ДѓЙцФЃМЏГЩЕчТЗаЫЦ№ЕФЪБКђЃЌдуИтСМТЪвЛЖШШУКмЖрЙЋЫОЪЇШЅСЫаХаФЃЌЕЋЛЙЪЧЯЩЭЏАыЕМЬхЁЂЕТжнвЧЦїЕШЙЋЫОНЋаОЦЌжЦдьГЕМфЛЛГЩСЫЮоГОЕФГЌОЛМфЃЌНјШыЕФШЫЖМвЊДЉЩЯМЋЦфбЯУмЕФЗРЛЄЗўЃЌШЗБЃЛвГОЁЂКЙвККЭУЋЗЂВЛЛсЫ№ЛЕДрШѕЕФОЇдВЃЌЪЕЯжСЫзуЙЛИпЕФСМТЪЁЃ

MOS ЙмЃЈГЁаЇгІОЇЬхЙмЃЉНгНќадФмМЋЯоЕФЪБКђЃЌКмЖрШЫвВШЯЮЊОЇЬхЙмВЛФмдйБфаЁЃЌаОЦЌадФмЬсЩ§ЕНСЫОЁЭЗЁЃЕЋзюжеЃЌFinFET МмЙЙМЬајЭЦЖЏСЫаОЦЌММЪѕЕФЧАНјЁЃ

2019 ФъЃЌдкЬЈЛ§ЕчФкВПОйАьЕФдЫЖЏЛсЩЯЃЌЬЈЛ§ЕчДДЪМШЫеХжвФББЛУНЬхЮЪЕНСЫФІЖћЖЈТЩЪЧЗёзпЕНОЁЭЗЪБЃЌЫћШЯЮЊетИіЮЪЬтЕФД№АИЃЌ]гаШЫжЊЕРЃЌвђЮЊКѓУцжСЩйЛЙга 5nmЁЂ3nm КЭ 2nm ЕФММЪѕЁЃЕЋЫћЯраХЃЌФІЖћЖЈТЩЕФЮДРДЛсЪЧЃК

ЩНЧюЫЎОЁвЩЮоТЗЃЌСјАЕЛЈУїгжвЛДхЁЃ

ЬтЭМРДздЦЛЙћ

РДдДЃКРзПЦММ

дЮФБъЬт : 3nmЕФаОЦЌеНељЃЌВХИеИеПЊЪМ

ЗжЯэ

ЗжЯэ

ЭМЦЌаТЮХ

-

вЕМЈДѓКУЃЁаОЦЌДѓГЇдБЙЄНБН№ьЩ§200%ЃЁ

-

аОЖЏПЦММгыЬкбЖдЦДяГЩеНТдКЯзїЃЌЮЊПЭЛЇДђдьвЛеОЪНаОЦЌЩшМЦЗўЮёдЦЦНЬЈ

-

РГЕЯЫМзЈЗУ | ШЫЛњНЛЛЅаТЮЌЖШЕФгаСІЭЦЪжЁЊLattice Drive

-

СЂбЖММЪѕЃКИпадФмЁАAIЪ§ОнжааФНтОіЗНАИЁБ

-

Н№АйдѓПЦММЦьЯТдьЮяЪ§ПЦИГФмЕчзгЕчТЗВњвЕЪ§зжЛЏЩ§МЖ

-

2024жаЙњЙњМЪвєЦЕВњвЕДѓЛс ЈO ЁАПЩППадЩњВњСІЁБМгЫйЪгЬ§ВњвЕжЧФмЛЏЩ§МЖ

-

аЏЪжВњвЕЛяАщДДдьЮоЯоПЩФм

-

НјЛїЕФДДТѕЫМЃЌв§СьНќКьЭтЙтЦзИіШЫМЖгІгУЕФЛЎЪБДњДДаТ

ММЪѕЮФПт

зюаТЛюЖЏИќЖр

-

МДШе-12.26СЂМДБЈУћ>>> ЁОдкЯпЛсвщЁПДхЬягУгкAR/VRЩшМЦПЊЗЂНтОіЗНАИ

-

1дТ8ШеЛ№ШШБЈУћжа>> AllegroжњСІЦћГЕЕчЦјЛЏКЭЕзХЬНтОіЗНАИгХЛЏдкЯпбаЬжЛс

-

1дТ9ШеСЂМДдЄдМ>>> ЁОжБВЅЁПADIЕчФмМЦСПЗНАИЃКаТвЛДњжБСїБэЁЂEVГфЕчЦїКЭSМЖЕчФмБэ

-

МДШе-1.14Л№ШШБЈУћжа>> OFweek2025жаЙњжЧдьCIOдкЯпЗхЛс

-

МДШе-1.16СЂМДБЈУћ>>> ЁОдкЯпЛсвщЁПImSym ПЊЦєШЋСїГЬГЩЯёЗТецЪБДњ

-

МДШе-1.20ЯоЪБЯТди>>> АЎЕТПЫЃЈIDECЃЉЩшБИМАЙЄвЕЯжГЁАВШЋНтОіЗНАИ

ЭЦМізЈЬт

- 1 140МвжаЙњАыЕМЬхЦѓвЕБЛСаШыЪЕЬхЧхЕЅЃЌЩЬЮёВПЛигІЃЁЃЈИНУћЕЅЃЉ

- 2 аЁУз15 UltraГЌЧПадФмШЋЦиЙтЃКгАЯёАВзПЪжЛњЬьЛЈАхЃЁ

- 3 ЗтЩБвЛЧаЯШНјММЪѕЃЁУРЙње§ЪННЋет140МвжаЙњАыЕМЬхЙЋЫОСаШыЪЕЬхЧхЕЅ

- 4 AWSзюЧПAIаОЦЌ ЃЁTrainium 2ММЪѕЯИНкНтЮі

- 5 УРЙњжЦВУТфЕижЎМЪЃЌжаЙњАыЕМЬхЙњВњЛЏЧщПіШчКЮЃП

- 6 EUVЙтПЬЛњОоЭЗЗчдЦељЖсеН

- 7 АыЕМЬхаавЕЩюЖШЖДВьЃЈЩЯЃЉЃКЯжзДгыЮДРДЧїЪЦЗжЮі

- 8 КУШЫЛЦШЪбЋЃКЪЧИєАЖЙлЛ№ЃЌЛЙЪЧЭцЛ№здЗйЃП

- 9 жаЙњАцгЂЮАДяФІЖћЯпГЬЦєЖЏIPO

- 10 ЙњВњEUVЙтПЬЛњЃЌЭђжкжѕФПЃЌГЩУРЙњаОЦЌНћСюЕФЦЦОжЕу

- ИпМЖШэМўЙЄГЬЪІ ЙуЖЋЪЁ/ЩюлкЪа

- здЖЏЛЏИпМЖЙЄГЬЪІ ЙуЖЋЪЁ/ЩюлкЪа

- ЙтЦїМўбаЗЂЙЄГЬЪІ ИЃНЈЪЁ/ИЃжнЪа

- ЯњЪлзмМрЃЈЙтЦїМўЃЉ ББОЉЪа/КЃЕэЧј

- МЄЙтЦїИпМЖЯњЪлОРэ ЩЯКЃЪа/КчПкЧј

- ЙтЦїМўЮяРэЙЄГЬЪІ ББОЉЪа/КЃЕэЧј

- МЄЙтбаЗЂЙЄГЬЪІ ББОЉЪа/В§ЦНЧј

- ММЪѕзЈМв ЙуЖЋЪЁ/НУХЪа

- ЗтзАЙЄГЬЪІ ББОЉЪа/КЃЕэЧј

- НсЙЙЙЄГЬЪІ ЙуЖЋЪЁ/ЩюлкЪа

ЗЂБэЦРТл

ЧыЪфШыЦРТлФкШн...

ЧыЪфШыЦРТл/ЦРТлГЄЖШ6~500Иізж

днЮоЦРТл

днЮоЦРТл