2nm团战全面展开:台积电领先,欧洲发力

材料和工艺:互连技术将升级

着先进工艺一步步向高端迈进,芯片制造商持续在最新工艺节点的晶体管制造技术上取得进步,但互连技术似乎跟不上先进工艺的步伐。

随着晶体管尺寸的缩小,连接它们的金属线也必须在多层互连堆积的整体层高结构中进行。

传统上一般采用铜互连,但是发展到2nm,相应的电阻电容(RC)延迟问题非常突出。

目前,面向2nm及更先进制程的新型互连技术主要包括:

混合金属化或预填充,将不同的金属嵌套工艺与新材料相结合,以实现更小的互连和更少的延迟;

半金属嵌套,使用减法蚀刻,实现微小的互连;

超级通孔、石墨烯互连和其他技术。

混合金属化在互连中使用两种不同的金属。对于2nm来说,这很有意义,与双金属嵌套相比,通孔电阻更低,可靠性会提高;同时可以保持互连中铜的低电阻率。

台积电和台湾地区交大联手,开发出全球最薄、厚度只有0.7纳米的超薄二维半导体材料绝缘体,可望借此进一步开发出2nm,甚至是1nm的电晶体通道。

在先进工艺上,目前台积电、三星及英特尔等几家实力强大,日本公司主要是在光刻胶、硅片等材料有较大优势,但日本也没有放弃先进工艺上的努力。

日本产业技术综合研究所与中国台湾半导体研究中心( TSRI )等展开合作,开发了用于新一代半导体的新型晶体管结构。

与此前的晶体管相比, CFET结构的晶体管性能高、面积小, 有助于制造 2nm 以下线宽的新一代半导体。

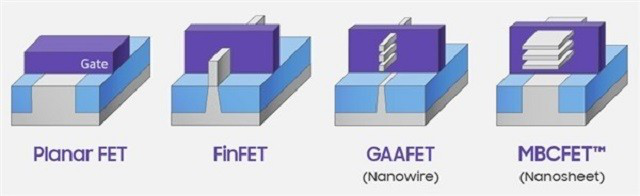

三星计划在3nm的时候生产下一代晶体管,称为环栅场效应晶体管。台积电计划将FinFETs扩展到3nm,但将在2nm左右迁移到环栅。

当鳍(fin)宽度达到5nm(相当于3nm节点)时,FinFETs接近其实际极限。环栅晶体管比FinFETs具有更好的性能、更低的功耗和更低的漏电,但它们的制造难度更大,成本也更高。

其他新的和更有前途的互连解决方案即将出现,但它们可能要到2023年的2nm到来时才会出现。

EDA工具:高精尖技术集中在少数人手中

EDA作为集成电路产业链的命脉,自始至终连接和贯穿着芯片制造和科技应用的发展;芯片设计、晶圆制造、封装测试,直至电子产品的设计,每个环节都离不开EDA工具。

中美贸易战拉开大幕,EDA禁运首当其冲,成为卡脖子工程。EDA的的战略性,重要性被推到空前高度。

面对2nm高精尖的制程工艺,Cadence和Synopsys创建了全新的EDA工具堆栈,并开发全新的IP库。

2nm制程要求芯片开发人员必须采用全新的设计规则和流程,并重新制作他们以前可能使用过的所有内容。

目前国内的EDA工具很分散,提供不了全套的工具链,而国际EDA公司提供给芯片企业的一般都是全套工具。

国内EDA产业面临的最大问题就是国内没有形成一个完整的、互相促进的产业链,抱团一直是半导体产业发展的最重要方向。

国内EDA工具厂商鲜少参与晶圆厂和设计公司的合作研发,有EDA产品生产出来,也得不到使用和反馈,进而难以进步。

中国EDA已迎来最好的时代,华大九天、国微集团、芯华章、广立微、概伦电子、芯和半导体等多家国产EDA公司已整装待发,期待能以厚积薄发的技术实力快速完善中国集成电路产业链,支持5G、人工智能、云计算等多项未来科技的发展。

未来本土EDA的发展之路,还得靠脚踏实地、一步一个脚印地走出来,最终实现真正的本土化。

结尾

2nm先进制程的每个环节和细分领域均环环相扣,只有通过产业链上下游联动,才能获得成功。而苹果最有可能成为最先尝鲜2nm芯片的厂商,此外在2024年之后,高通、英伟达、AMD等都会成为其2nm技术的厂商。

图片新闻

技术文库

最新活动更多

-

即日-1.16立即报名>>> 【在线会议】ImSym 开启全流程成像仿真时代

-

即日-1.20限时下载>>> 爱德克(IDEC)设备及工业现场安全解决方案

-

即日-1.24立即参与>>> 【限时免费】安森美:Treo 平台带来出色的精密模拟

-

即日-1.31立即参与>>> 【限时免费下载】村田白皮书

-

即日--2.7了解详情>> 【森海塞尔】TeamConnect系列产品——提升视听之体验,塑造音频之未来

-

限时免费立即试用>> 燧石技术,赋光智慧,超越感知

推荐专题

分享

分享

发表评论

请输入评论内容...

请输入评论/评论长度6~500个字

暂无评论

暂无评论