台积电2nm工艺研发突破,或采用环绕栅极晶体管技术

最近,半导体业界公认的晶圆代工之王台积电再次传出芯片利好消息,外媒援引产业链消息人士的信息,台积电2nm工艺的研发进展超出预期,甚至快于原计划。

2nm似乎是目前已知芯片工艺能达到的极限所在,关于2nm工艺的消息并不多。此前台积电曾透露出公司已经获得了建造2nm工艺芯片生产工厂所需的土地,或将位于新竹科学园区;另外一则关于台积电2nm工艺的消息则是在上月底举办的台积电2020年度全球技术论坛上,他们透露正在同一家主要客户紧密合作,加快2nm工艺研发进展,不过并未透露具体客户。

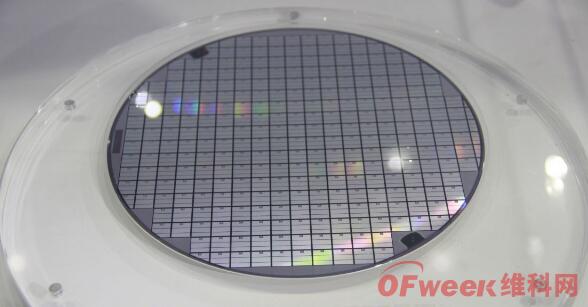

图片源自OFweek维科网

2nm工艺终于要用上环绕栅极晶体管技术(GAA)

根据消息人士透露台积电的2nm工艺,不会继续采用成熟的鳍式场效应晶体管技术(FinFET),而会采用环绕栅极晶体管技术(GAA)。要知道,在3nm工艺节点上,台积电选择了采用FinFET放弃了GAA,而三星却在3nm工艺上一直坚持着GAA路线,如今台积电率先来到2nm工艺路口,其作出的选择也基本意味着接下来半导体行业整体的到前进方向。

为什么考虑选择GAA,这还得从FinFET说起。众所周知,晶体管的演化与半导体发展进程息息相关,晶体管是一种控制电流大小与开关的电子器件,其作用就跟水龙头用来控制水流的大小以及开关一样。而晶体管中一个重要影响因素就是场效应,是指通过施加一个电场来实现对电流的控制,所以也就有了场效应晶体管(Field-Effect Transistor,FET)一说。

FinFET就是源自于场效应晶体管,在FinFET的架构中,闸门的形状类似鱼鳍的叉状3D架构(“鳍式场效应晶体管”命名的由来),可于电路的两侧控制电路的接通与断开。这种设计可以大幅改善电路控制并减少漏电流,也可以大幅缩短晶体管的栅长。

芯片工艺节点发展到5nm之后,FinFET也面临一系列难题。首先是随着栅线之间间距的减小,再想像以往一样在一个单元内填充多个鳍线已不现实,同时栅线间距的减小还会导致FinFET的静电问题急速加剧并直接制约晶体管性能的提升,此外FinFET的出现虽然突破了平面晶体管的短沟道效应限制让电压得意降低,但是还不够,在理想情况下沟道应该被栅极完全包围。因此在5nm之后,业界迫切需要一个新的结构来替代鳍式晶体管结构,这就带来了全环绕栅极晶体管,也就是我们所说的GAA。

当然,受限于摩尔定律等原因,采用GAA结构也需要满足以下几个条件:1、新的结构需要的生产工艺应该与FinFET相似,可使用现有的设备及技术成果实现;2、新的结构应实现对通道更好的控制,例如栅极与通道之前的接触面积更大;3、新的结构带来的寄生电容和电阻问题应得到显著改善。

以台积电2nm目前的研发进度来看,预计台积电2023年下半年可望进入风险性试产,2024年正式量产。

图片新闻

技术文库

最新活动更多

-

即日-1.16立即报名>>> 【在线会议】ImSym 开启全流程成像仿真时代

-

即日-1.20限时下载>>> 爱德克(IDEC)设备及工业现场安全解决方案

-

即日-1.24立即参与>>> 【限时免费】安森美:Treo 平台带来出色的精密模拟

-

即日-1.31立即参与>>> 【限时免费下载】村田白皮书

-

即日--2.7了解详情>> 【森海塞尔】TeamConnect系列产品——提升视听之体验,塑造音频之未来

-

限时免费立即试用>> 燧石技术,赋光智慧,超越感知

推荐专题

分享

分享

发表评论

请输入评论内容...

请输入评论/评论长度6~500个字

暂无评论

暂无评论