7.30-8.1 全数会2025(第六届)机器人及智能工厂展

火热报名中>>

几张图让你轻松理解DDR的串扰

让你评估高速串行信号的串扰,你会说它们的串扰在-40db以下,没什么影响。但是如果让你评估像DDR这种并行信号的串扰,你说DQ0和DQ1的串扰-30db,DQ1和DQ2的串扰-25db,DQ2和DQ3的串扰……你慢慢数,我先走了。

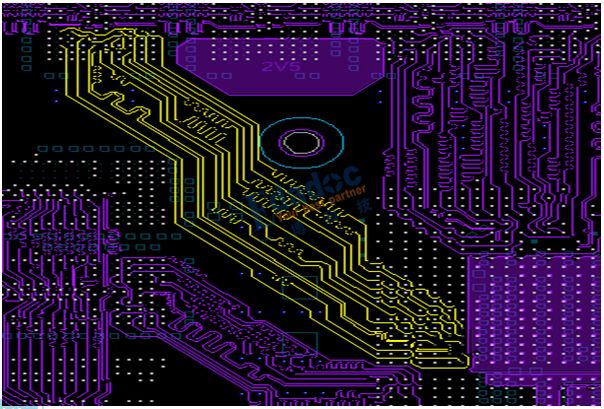

根据以往的经验,今天大家都会怀着无比沉重的心情来到公司上班,高速先生也表示深深的理解哈,所以今天的文章是非常的简洁而形象的,以便满足大家今天不想多动脑的欲望。记得前几篇文章提到过人工智能的话题,我们就接着说一点技术上的东西哈。在人工智能迅速冒起的热潮中,作为核心算力的DDR模块无疑出了一次很大的风头。因为在追求超大算力的情况下,人们对DDR的容量和速率要求越来越高。我们高速先生接触的算力卡一块比一块小,但是板内的DDR模块却有越来越多的趋势,动不动就上4通道、8通道,甚至更多。而且在颗粒数量不断提高的同时,我们要求的速率基本也越来越高,基本都是2400Mbps起步,最高的有做过3200Mbps的。加上板子密度越来越小,从我们这一年多以来接触的各种DDR的设计来看,可以毫不夸张的和大家说,现在DDR的设计难度可能已经超过了很多人的想象了……

做过DDR设计的同行都知道,在非常密的颗粒排布下,想成功的把所有的信号拉出来可能都要去条命,然后导通之后还要把手抓稳去做抖一下就让你想剁手的等长(5mil,2mil,我们有见过客户要求做1mil的……),当你以为可以收工的时候,客户还要抱着看上去和你商量的态度说你的间距能不能再拉开一点。

行……我们的设计工程师是非常严谨的,能拉开1mil也是爱的,虽然可能自己也不知道辛辛苦苦拉开的1mil到底有什么用,就好像做等长的时候辛辛苦苦做的2mil等长有什么用是一样一样的。

一般的结果都是这样的:我们工程师经过不断挣扎之后,时间也去得差不多了,客户也终于体谅了我们工程师的痛苦,大家终于强行达成了共识:辛苦了,要不就这样好了。终于,不用再做更严格的等长了,终于不用再拉开0.5mil的间距了。虽然客户的内心是在想:其实应该还可以继续……

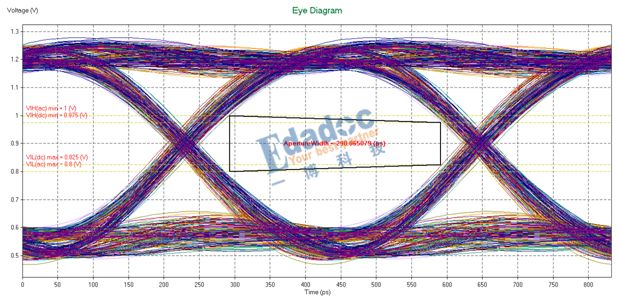

那等长做好了,间距也看起来不能再拉开了,交给我们SI成员进行仿真,在我们的眼中这样的一组数据信号的结果已经是非常不错了。大概是这样的:

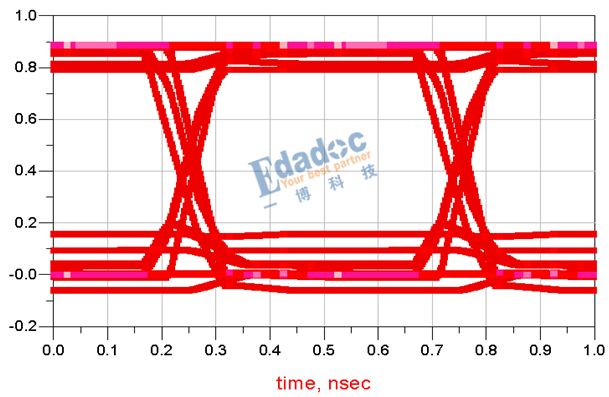

从这组数据信号眼图的Aperture来看,整个高低电平的裕量是非常大的,这样的眼图在实际调试肯定是PASS的。但是如果我把一些point标出来让大家再看同一个眼图的话,你们可能会觉得有点惊讶:为什么我的等长都做到了2mil,间距也已经拉开到不能再开了,但是看这组数据的延时居然差了快50ps(下图蓝色mask),电平上面的幅度振荡也超过了100mV(下图红色mask)。

数据信号是严格点对点的信号,我们的阻抗是40欧姆,然后我们的芯片驱动和芯片接收的ODT也是40欧姆,那说明了这样的延时和电平振荡并不是由阻抗不匹配的反射造成的(至少很大部分不是)。那这个时候我们又把目光集中到了很难分析的串扰了。

从我们的专业角度来看,的确是串扰要背这个锅。在这里我们不说一些很复杂的理论和公式,我们仅以下面的几张图来让大家理解串扰到底是怎么影响到我们的电平振荡和延时的。

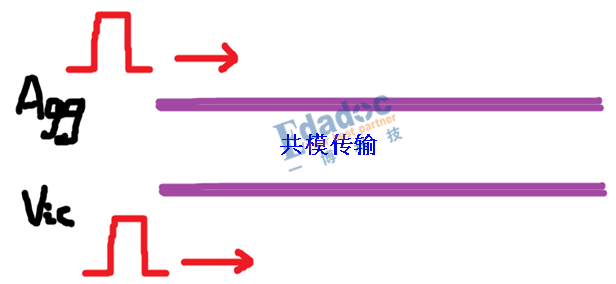

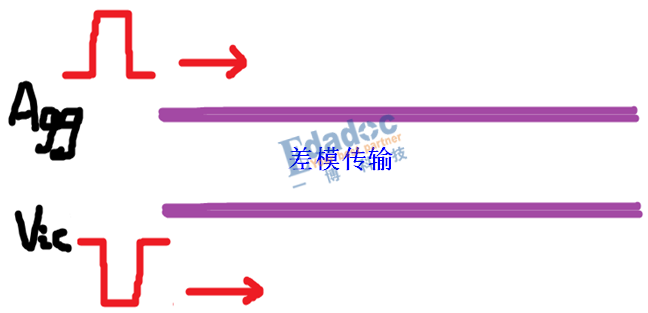

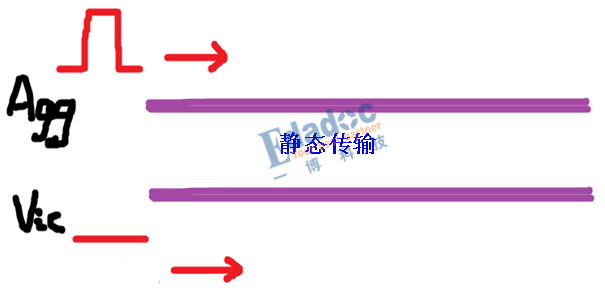

相邻的两根线会有3种传输的模式,分别是下面这样的:

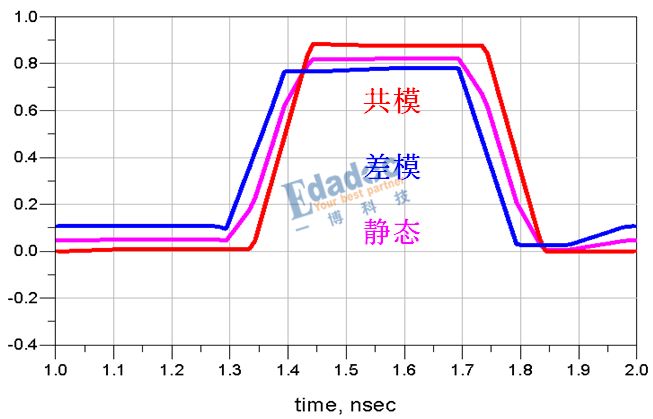

然后攻击信号达到接收端之后,他们的结果是这样的:

这里回答你们可能想问的两个问题:

1,为什么达到的时间会不一样?共模速度慢,差模速度快,静止排中间。因为在共模的影响下,两线之间的容性最弱;在差模的影响下,两线的容性最强,这时就好像差分线一样,两线互为参考,因此传输延时最快。

2,为什么电平幅度不一样?同样,共模的时候两线电平是同向的,互相补充,幅度偏高;差模的时候两线的电平反向,互相抵消,幅度降低。

所以当这两根线跑不同的随机码型时,你看到的其中一根线的信号是下面这样的就不奇怪了。

再回到我们上面的一组DDR数据信号,对于他们而言就更复杂了,一组8根DQ加上DM信号都有着不同的码型,互相之间的串扰影响就导致了他们的眼图呈现出不同的延时和电平振荡了。其实理论可能很复杂,但是他的表现形式就是这样的。总之,对于像DDR这种并行信号的串扰,还是在时域的角度上去分析会更直观和有说服力。当然难度也摆在这里,你必须把整组信号乃至整个通道的信号一起分析,才能得到串扰影响的最大化。

所以呢,我们做了5mil甚至更小的等长和上面仿真波形的50ps来比,真的是很微不足道。实际上串扰在DDR模块里的确会有更为严重的影响,试想一下,我们在高速串行信号里面5mV的串扰都觉得非常大了,在DDR模块里居然能有上百mV。当然两者还是有很大差异的,高速串行信号的眼图裕量目前和DDR相比还是小很多,一般只有100mV以内,我们目前的DDR系统的高低电平的裕量有几百mV,而且DDR的速率也决定了走线的损耗基本对它没太大的影响。

所以我们对100mV的串扰结果还是可以接受,而且从整个波形来看,裕量也还是很大。但是随着DDR的电平越来越低,相应的裕量肯定也会越来越小,到那时候串扰可能就会影响很严重了。

黄刚 | 文

— end —

图片新闻

技术文库

最新活动更多

-

3月27日立即报名>> 【工程师系列】汽车电子技术在线大会

-

4月25日立即报名>> 【线下论坛】新唐科技2025新品发布会

-

在线会议观看回放>>> AI加速卡中村田的技术创新与趋势探讨

-

4月30日立即参与 >> 【白皮书】研华机器视觉项目召集令

-

即日-5.15立即报名>>> 【在线会议】安森美Hyperlux™ ID系列引领iToF技术革新

-

5月15日立即下载>> 【白皮书】精确和高效地表征3000V/20A功率器件应用指南

推荐专题

分享

分享

发表评论

请输入评论内容...

请输入评论/评论长度6~500个字

暂无评论

暂无评论