7.30-8.1 全数会2025(第六届)机器人及智能工厂展

火热报名中>>

围殴DDR系列之设计与仿真分析篇

作为高速先生的宝藏话题,DDR的设计与仿真一直是我们关注的重点,上周五的文章介绍了DDR的发展历史、关键技术和JEDEC标准,本周继续对DDR设计及仿真分析的文章进行分类导读。

01

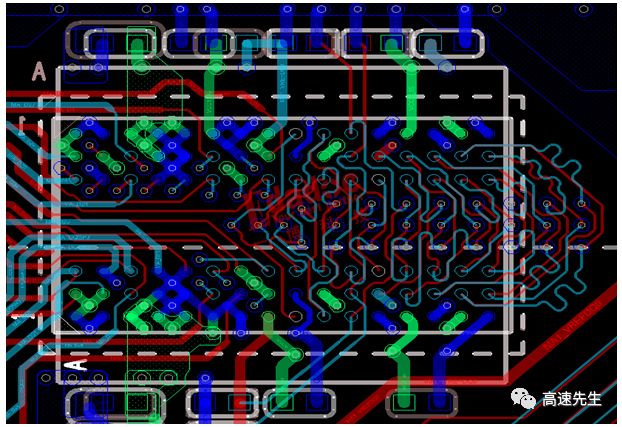

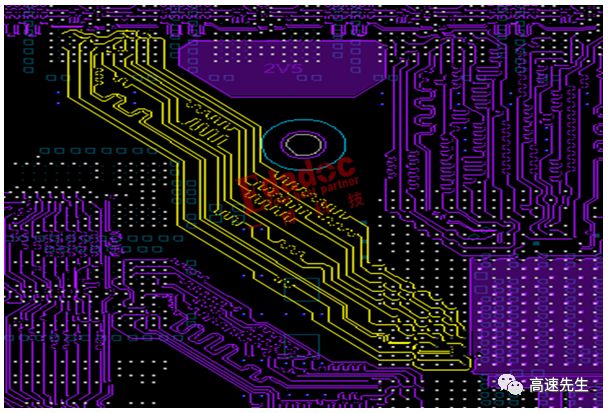

对于Layout工程师而言,最关心的莫过于DDR的设计要点。比如,在布局阶段,需要评估DDR走线拓扑对布局的影响(主要针对地址控制类信号)、滤波电容的布局要求、VREF电路布局、匹配电阻的布局等;在布线阶段,除了走线拓扑,还需要关注等长要求和电源设计。《DDR3布局的那些事儿》、《DDR3布线的那些事儿》

02

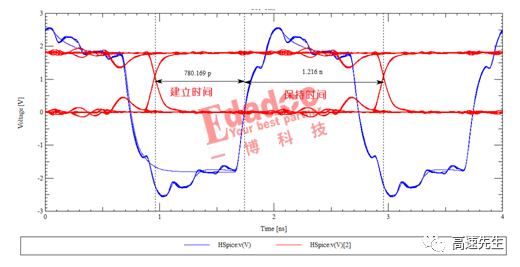

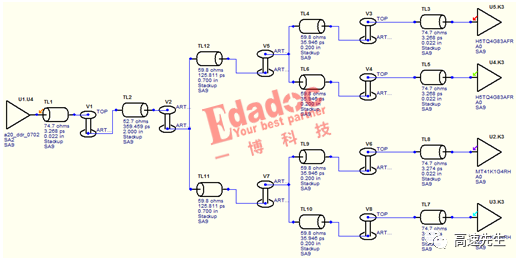

提到DDR设计,少不了线长匹配和时序要求,对于DDR等长要求的总体原则是:地址、控制/命令信号与时钟做等长。DQ/DM信号与DQS做等长。本文用仿真实例向大家展示DDR中地址相对于时钟的建立时间与保持时间。《DDR线长匹配与时序(上)》

03

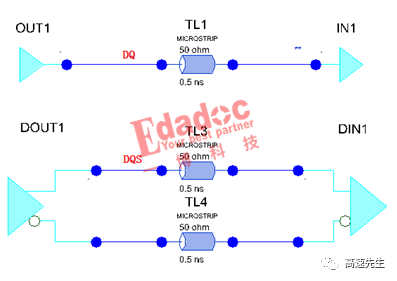

数据信号与DQS又是什么样的关系呢?DDR和普通的SDRAM相比,读取速率翻番,这个又该怎么理解?对等长要求的影响如何?《DDR线长匹配与时序(下)》

04

DDR信号网络多,走线密度大,速率较高,DDR信号质量直接关系到整块板子的设计成败,此时,仿真分析会为我们的设计提供有力的支撑。本文通过几个案例让初学者对DDR仿真有一个简单的认识。《DDR信号完整性仿真介绍一》、《DDR信号完整性仿真介绍二》

05

此外,对于DDR这种并行信号的串扰该如何评估?希望这篇文章对你有所启发。《几张图让你轻松理解DDR的串扰》

文 / 姜杰(微信公众号:高速先生)

图片新闻

技术文库

最新活动更多

-

3月27日立即报名>> 【工程师系列】汽车电子技术在线大会

-

在线会议观看回放>>> AI加速卡中村田的技术创新与趋势探讨

-

4月30日立即参与 >> 【白皮书】研华机器视觉项目召集令

-

即日-5.15立即报名>>> 【在线会议】安森美Hyperlux™ ID系列引领iToF技术革新

-

5月15日立即下载>> 【白皮书】精确和高效地表征3000V/20A功率器件应用指南

-

5月16日立即参评 >> 【评选启动】维科杯·OFweek 2025(第十届)人工智能行业年度评选

推荐专题

-

10 功率半导体,嗅到风险

分享

分享

发表评论

请输入评论内容...

请输入评论/评论长度6~500个字

暂无评论

暂无评论