7.30-8.1 全数会2025(第六届)机器人及智能工厂展

火热报名中>>

无法任性的AC耦合电容,选值有什么考量?

作者:王萍

刚刚纠结完AC耦合电容的摆放位置,接着我们又遇到了选值的问题!显然,在选值问题上,AC耦合电容无论如何是任性不起来的。

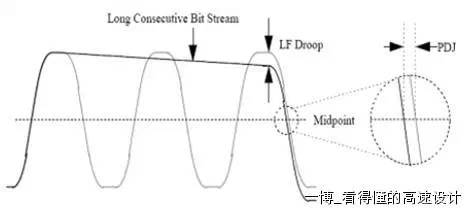

我们知道,在串行信号中串个AC耦合电容,这个电容可以提供直流偏压和过电流保护,但也会给链路带了另一个问题PDJ(pattern-dependent jitter)。顾名思义,这和码型有关。我们的链路可以等效成高通RC电路,当出现连续的“1”或“0”时,会出现下图的直流压降,这不仅会影响眼高,还会造成PDJ。

怎样才能减小这个直流压降呢?这和RC时间常数有关,RC值越大,能通过的直流分量就越多,直流压降越小。由于链路中等效R是相对固定的,只能调节耦合电容值了。如下图电容值越大,压降越小。

那我们就把电容无限加大吧!

答案是:No,不行!

因为,实际安装后的电容不是理想电容,除了ESR,ESL,还有安装电感,所以就存在一个串联谐振频率。电容在此频率之前呈容性,之后呈感性。电容值越大,谐振频率越小,电容在较低频率就会呈现感性,这样会造成信号高频分量衰减增大,同样会使眼高减小,上升沿变缓,jitter增加。

所以选值时要综合以上两点考量,一般业界都推荐0.01uF~0.2uF,最常见的就是0.1uF的电容。封装的选择不建议使用大于0603的封装,最好是0402的。

图片新闻

技术文库

最新活动更多

-

3月27日立即报名>> 【工程师系列】汽车电子技术在线大会

-

4月1日立即下载>> 【村田汽车】汽车E/E架构革新中,新智能座舱挑战的解决方案

-

即日-4.22立即报名>> 【在线会议】汽车腐蚀及防护的多物理场仿真

-

4月23日立即报名>> 【在线会议】研华嵌入式核心优势,以Edge AI驱动机器视觉升级

-

4月25日立即报名>> 【线下论坛】新唐科技2025新品发布会

-

4月30日立即参与 >> 【白皮书】研华机器视觉项目召集令

推荐专题

分享

分享

发表评论

请输入评论内容...

请输入评论/评论长度6~500个字

暂无评论

暂无评论