4日10日 OFweek 2025(第十四届)中国机器人产业大会

立即报名 >>>

7.30-8.1 全数会2025(第六届)机器人及智能工厂展

火热报名中>>

面对PDN目标阻抗的设计要求,我们如何选择电容?

作者:吴均 一博科技高速先生团队队长

承前:介绍了电容的参数ESR和ESL,以及电容并联与串联

本节:面对PDN目标阻抗的设计要求,我们如何选择电容

上一篇文章提出的问题是:2.5V电源,最大工作电流为5安培,手册上要求设计电源噪声小于5%,那么我们设计的目标阻抗是多大?很多朋友都回答正确,答案是50毫欧,大家一起加3分。其实目标阻抗计算也是有很多争议性问题的,比如转折频率如何确定,电流随频率的变化如何界定与评估。这些问题讨论起来篇幅很长,也欢迎大家移步到PCBTime的相关帖子进行交流。

图1是采用100uf,10uf和0.1uf电容组成的阻抗曲线。黑色曲线没有考虑安装电感,紫色曲线简单评估了一下安装电感。这是我们大部分项目采用的电容组合,能看到基本可以满足100M以内50毫欧的目标阻抗设计要求。这也验证了我们现在使用这样的电容组合是符合电源设计要求的。唯一的缺点就是在部分频段,电容的数量有点过设计。

图1

但是随着电压降低,电流增大,最直接的后果就是目标阻抗减小。部分的低压Core电源,设计目标阻抗在10毫欧以下,甚至只有几毫欧。这时候可以有两种方法达到这个目标。

1、 继续增加各频段电容的数量,通过电容并联的效果,拉低谐振频率点的PDN阻抗,从而拉动整个阻抗曲线降低。这个做法往往事倍功半,大量的同种类电容(如0.1uf电容)起的效果并不好,对反谐振的抑制作用很小。

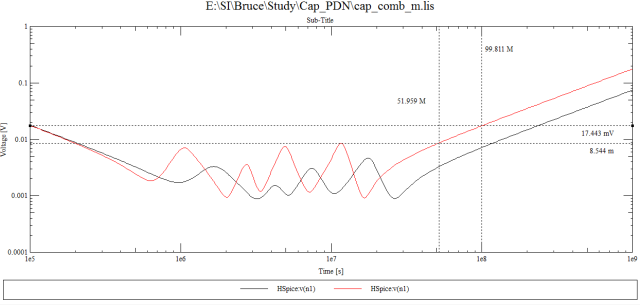

2、 增加电容种类,可以用最合适的电容组合来实现PDN的设计要求。如图2所示,没有增加电容的总数量,只是优化了电容容值选择,就基本实现了50M以内8毫欧的阻抗设计,100M以内的阻抗设计也比图1要小很多。

图2

(注:图1和图2采用了Hspice仿真,模拟多种电容并联的效果,由于等效电路网表的写法,纵坐标单位显示是电压V,但是取值等效于阻抗。大家如果对这个Hspice网表有兴趣,可以在PCBtime论坛上进行讨论交流)

(注:其他软件,如Designer和ADS也可以实现多种电容并联效果的仿真,电路的处理会有不同的技巧,也可以在PCBtime论坛上进行讨论交流)

从以上的讨论可以看出,电容取值的技巧,可以很大程度上改变PDN的阻抗曲线,从而影响到电源噪声。如何进行电容取值,会有很多的经验与技巧,需要在实践中进行摸索。当然,现在也有很有很多智能式的软件可以帮助我们进行评估,如Sigrity的Optimize PI工具,功能就非常强大。

当然,电容取值是不是满足自阻抗的Target要求就够了,还是需要考虑更复杂的如EMC设计需求,业内也还有一些不同的看法。

不管是同事,还是自媒体网友,大家都希望高速先生给出一些简单实用的设计规则。在现实的世界里,设计的复杂性越来越高,简单的规则很难保证准确性。很可能我们的文章在介绍误区,然后我们又继续给出一些还是“误区”的规则。

电容选择总结,先做一些限定,方便后面描述:

? 常规电源设计:在本文定义为目标阻抗要求在20毫欧以上的电源设计,普遍来说,要么就是电压不是很低,或者电流不是非常大。

? 低电压大电流的设计:在本文定义为目标阻抗要求在10毫欧以下的电源设计。

1、 常规的电源设计,现在普遍采用的电容选择方案是可行的,可以满足电源的噪声需求。但是电容数量过多,导致浪费,同时浪费了板上的有效布局布线空间。

2、 常规的电源设计,可以通过PDN的仿真评估,或者一些芯片公司提供的电容设计Excel表格工具来进行评估,大幅减少电容的使用。

3、 低电压大电流的设计,推荐进行直流电压跌落仿真和PDN仿真,可以有效改善电源设计质量

4、 低电压大电流的设计,如果不做仿真,电容取值可以遵循10倍容量范围选择三种电容的方案,增多电容的种类,降低反谐振。

问题来了!

电源PDN设计本来业内的争议就较多,本期问题也是有一定争议性的,或许没有标准答案,看看大家的意见:目标阻抗的设计方法,从自阻抗角度保证了芯片或者系统自身的正常工作的电源供电需求。那我们该如何理解转移阻抗?在什么情况下,我们需要考虑转移阻抗?

图片新闻

技术文库

最新活动更多

-

3月27日立即报名>> 【工程师系列】汽车电子技术在线大会

-

4月1日立即下载>> 【村田汽车】汽车E/E架构革新中,新智能座舱挑战的解决方案

-

4日10日立即报名>> OFweek 2025(第十四届)中国机器人产业大会

-

即日-4.22立即报名>> 【在线会议】汽车腐蚀及防护的多物理场仿真

-

4月23日立即报名>> 【在线会议】研华嵌入式核心优势,以Edge AI驱动机器视觉升级

-

4月25日立即报名>> 【线下论坛】新唐科技2025新品发布会

推荐专题

-

1 HBM4大战

分享

分享

发表评论

请输入评论内容...

请输入评论/评论长度6~500个字

暂无评论

暂无评论