4日10日 OFweek 2025(第十四届)中国机器人产业大会

立即报名 >>>

7.30-8.1 全数会2025(第六届)机器人及智能工厂展

火热报名中>>

摩尔定律不会死去!这项技术将成为摩尔定律的拐点

遥想当年,英特尔(Intel)创始人之一戈登·摩尔创造了摩尔定律,为半导体行业发展指明了一条罗马大道。不过,毕竟理论自1965年至今已有五十余年,节点已微缩至几近纳米极限,行业摩尔定律逐渐放缓,甚至有言道“摩尔定律已死”。

摆在现实的是,纳米节点转换越来越难了,物理极限越来越近了。处在后摩尔时代的企业只能默默面对纳米极限的逼近吗?最近,英特尔为记者揭秘摩尔定律探索中的新拐点,即封装技术。

封装技术成为摩尔定律的新拐点

摩尔定律到底是什么,封装技术和摩尔定律到底有什么关系?请听笔者细细道来。1965年起初,戈登·摩尔表示集成电路上可容纳的元器件数量约18个月便会增加一倍,后在1975年将这一定律修改为单位面积芯片上的晶体管数量每两年能实现翻番。

回望摩尔定律整个历史,让晶体管沟道进一步缩短,突破物理极限也曾先后经历多个瓶颈。首先碰到的便是半导体材料的限制,由此行业发明了电化学镀铜和机械平面化的双镶嵌结构技术;而后遇到了设备物理限制,Si栅极和SiO2栅极电介质材料被金属栅极和高K电介质取代;再到193nm节点以上,受到光刻技术限制,行业光刻技术得以发扬,在制程节点45nm-32nm下产生了浸没工艺、16nm-10nm下产生了多重曝光工艺、7nm-5nm则引入了极紫外线(EUV)工艺。

因此,可以看出,为了延续摩尔定律,专家绞尽脑汁想尽各种办法,包括改变半导体材料、改变整体结构、引入新的工艺。但不可否认的是,摩尔定律在近几年逐渐放缓。10nm、7nm、5nm……芯片制程节点越来越先进,芯片物理瓶颈也越来越难克服。

因此,业内专家指出了后摩尔时代的硅技术的发展方向。一种是继续采用“硅-冯诺依曼”范式,通过改变结构形成新型器件,使得摩尔定律能够继续;另一种则是采用类脑模式的新兴架构,利用3D封装模拟神经元特性,构建存算一体的计算,这种架构不仅低功耗,还拥有并行性。

反观摩尔定律的“忠实粉丝”英特尔,一直以来默默按照戈登·摩尔描绘的路线发展,通过窥探巨头的发展,我们能看出什么?

近期,英特尔宣布进入IDM 2.0时代,彼时英特尔CEO帕特·基辛格宣布英特尔将开放代工服务(IFS)。上个月,帕特·基辛格向投资者表示:“我们已经看到潜在的代工客户对封装技术非常感兴趣”。

英特尔院士、封装研究与系统解决方案总监Johanna Swan表示,封装从未如此备受青睐。根据定义,封装是围绕一个或多个硅晶片的外壳,可以保护晶片免受外界影响,实现散热,提供电源,并将它们连接至计算机的其余组件。封装是用来建立外部连接的,但同时可以优化内部性能,一直达到晶体管这一级别。

那么封装究竟和摩尔定律有什么关系呢?Swan表示,封装的下一个基石是“功能致密化……即最大化单位体积性能”。

简单来说,封装能够减少芯片间的凸点间距,增大凸点密度。整体的密度越大,实际上也代表着单位面积上晶体管数量越密。所以说,封装虽然和摩尔定律没有直接关联,但却又影响着摩尔定律的发展。

而目前来说,英特尔已逐渐将芯片从单一芯片拆分成为数个小芯片,然后进行自由组合,这就是英特尔的小芯片Chiplet 2.0的技术。因此,这样的方式之下,对于封装和互连技术要求则会更高。

除此之外,需要注意的是,英特尔还宣布过神经拟态芯片“Loihi”,该产品相比传统计算机架构来说,完全模糊了内存和处理之间的界限。实际上,这也对应了之前业内专家的分析,之所以能够模拟神经元特性,得益于先进的3D封装技术,因此在此方面封装也“立了大功”。

英特尔的封装技术正迈向新的凸点间距

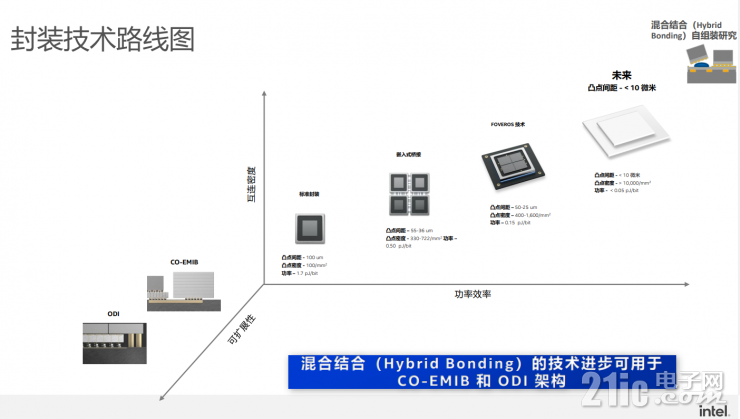

那么巨头英特尔的封装技术是如何发展的?根据Swan的介绍,从标准封装到EMIB(嵌入式多管芯互联桥接)再到Foveros,凸点间距从100μm缩减到50-25μm。展望未来,英特尔要做到小于10μm的凸点间距。

据英特尔介绍,EMIB是英特尔的一种2.5D高密度微缩技术,通过EMIB技术可以实现更好的导线密度。通过将硅中介层放入封装内,因而可进行局部高密度布线,并非全部芯片的高密度布线。利用EMIB技术,可将典型FCBGA(有机封装)的IO层提升至256-1024 IO/mm/层。这项技术能够实现55-36μm的凸点间距和每平方毫米330-722/m㎡的凸点密度,功率可以控制在0.5pJ/bit。

Foveros则是一种3D高密度微缩技术,如若在此基础上进行完美的设计,IO就甚至可以达到从400至10000IO/mm2。这项技术能够实现50-25μm的凸点间距和400-1600/m㎡的凸点密度,功率可以控制在0.15pJ/bit。

既然英特尔的目标是10μm以下,那么如何实现?答案是“混合结合”的Hybrid bonding技术。去年第二季度,这项技术的测试芯片已经流片,利用该技术不仅能够实现10μm凸点间距的愿景,还能使得凸点密度达到10000/m㎡,功率控制在0.05 pJ/bit。并且,混合结合技术可以使用与晶片到晶圆,也可以使用与晶圆到晶圆。

Swan强调,Hybridbonding能够使两芯片间实现更多互连,让英特尔能够提供更小、更简单的电路,也不必做扇入(fan-in)和扇出(fan-out)。有了更简单的电路,英特尔可以使用更低的电容,以降低通道的功率。

随着摩尔定律的继续推进,芯片的尺寸可能会变得越来越小,为了保证足够的带宽,必须要在导线上下功夫。整个小芯片尺寸变得越来越小,其实随着间距变得越来越短,传统基于焊料的技术已经快要到极限了,这就是为什么英特尔要使用全新的技术混合结合Hybrid bonding封装。

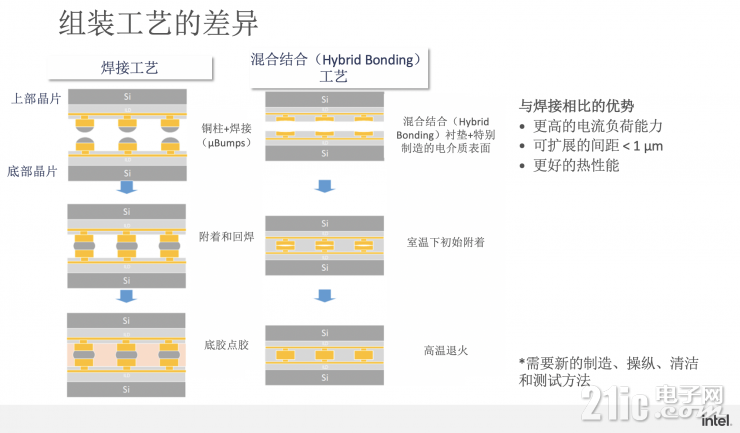

那么Hybrid Bonding到底和Foveros有什么区别,凭什么混合结合封装就能减少凸点间距?根据Swan的介绍,硅晶片分布在顶部和底部,中间则是带焊料的铜柱,英特尔所做的就是将它们附着在一起和回焊,让它升温。这些芯片之间有不同的温度,需要熔化焊料,将其放在一起,进行连接和回焊,再制作电气接头。在这之后,进行底部填充胶的分配,将填充有环氧树脂的硅放入模具之间以确保它们密封并能够完成放入并组装。

Hybrid Bonding与Foveros的焊接工艺不同,与焊接技术相反,混合结合技术使电介质的芯片非常光滑,而不是有突出的凸点,甚至实际上还会略微凹陷。当采用混合结合技术将这两个组件放在一起时,不必升高温度,可以在室温粘合两个组件。在其相互附着后,再升高温度并进行退火,铜在这时会膨胀,从而形成电气连接。Swan强调,这是非常有用的,因为这样可获得更高的载流能力。

“我们甚至可以将间距缩小到10微米以下。这样使我们目前在这些接口之间获得了比底部填充和紧密的铜密度更好的热性能。不过,当使用混合结合技术时,将需要一种新的制造、清洁和测试方法”,Swan如是说。

实际上,这种更小的间距颇具吸引力,能够联动许多技术的进化。Swan为记者解释,英特尔曾在2020年架构日中展出晶片的分解技术,英特尔将其分为GPU、CPU、IO等芯片或区块,这样就可以利用单独的IP的复用减少开发时间和芯片缺陷。

在Hybrid Bonding技术诞生之际,能够有效减少凸点间距,实现更高的凸点密度和更低的功耗。

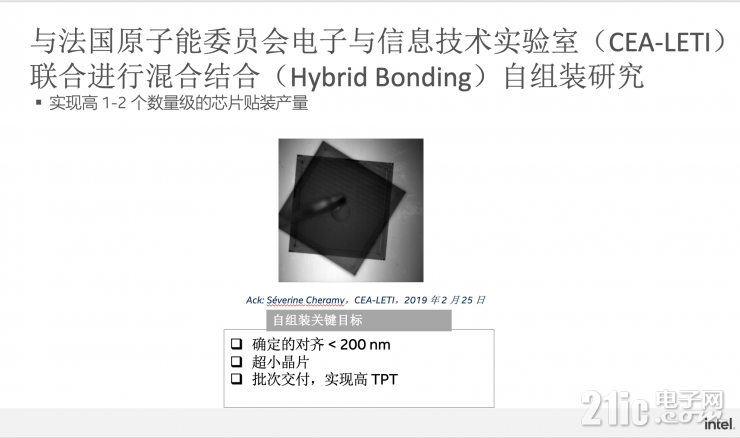

“不过,在焊接转向Hybrid Bonding后,依然需要面对另一个挑战”,Swan坦言,突然有了这么多区块,如果保持制造流程以相同的速度进行,但现在又有更多的晶片需要放置。“

我们正在考虑的解决方案是批量组装,我们称之为自组装”,Swan这样为记者介绍。

目前自组装已经有一些研究在进行中,英特尔正在积极与CEA-LETI合作研究,旨在一次能够放置更多个晶片,同时确定性使用非常小的晶片快速放置。目前来说,混合结合自组装已成为英特尔研究的重点,放在了研究路线图之中。

英特尔的封装技术是三位一体的

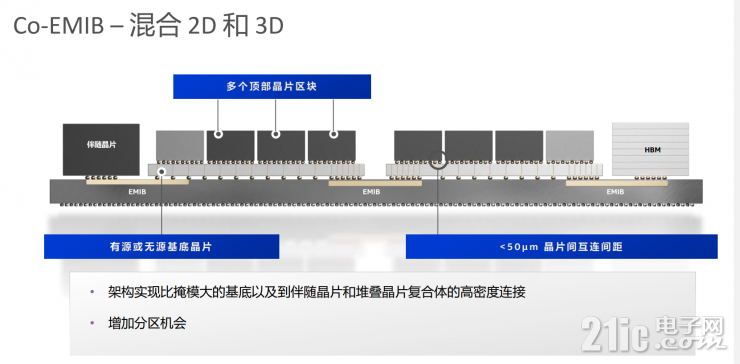

除了在功率效率和互连密度上的提升,英特尔还将封装技术分出可扩展性这个维度。这一维度之上,包括Co-EMIB和ODI两个技术。

按照之前英特尔的介绍来说,Co-EMIB是融合EMIB技术和Foveros技术的一种封装,是融合2.5D和3D的技术。如果将EMIB理解成水平方向,Foveros理解成垂直方向,那么Co-EMIB就是三位一体的兼顾两个方向的封装方式,能够真正发挥高密度微缩的效果。

可以说,可扩展的Co-EMIB的技术是发挥所有封装方式优势的平台,也是2.5D和3D封装技术碰撞交融、各自发挥优势的汇集地。

实际上,市场大趋势下,友商也开始逐渐将2.5D和3D封装技术进行组合。Swan认为,这种组合的趋势将继续持续下去,并且这种趋势能够为产品带来更多的机会和差异化优势。

英特尔利用2.5D和3D封装组合的成果就是Ponte Vecchio,该产品定位于超级计算机加速器。根据最近帕特·基辛格透露的信息,Ponte Vecchio采用了英特尔迄今最先进的封装工艺,晶体管规模突破1000亿,最多可集成多达47颗不同芯片模块,提供千万亿次(PFlops)的计算能力。

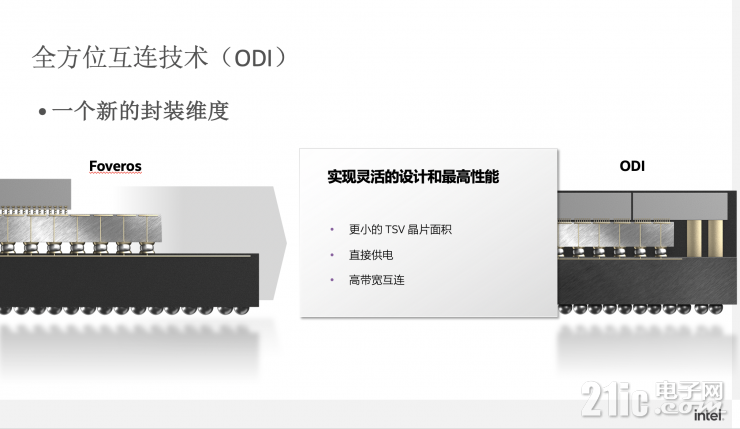

另一个颇具可扩展性的技术就是ODI(全方位互连技术)。根据此前的介绍,在常规的叠加方式下,下面的基础裸片必须是较大的,它要大于上面叠加的所有小芯片的总和。通过ODI技术可以改变这一点,两者之间可以进行更好的协调,并且可以上下做到面积统一。

英特尔的全新全方位互连技术(ODI)为封装中小芯片之间的全方位互连通信提供了更大的灵活性。顶部芯片可以像EMIB技术下一样与其他小芯片进行水平通信,同时还可以像Foveros技术下一样,通过硅通孔(TSV)与下面的底部裸片进行垂直通信。另外,这种方法减少了基底晶片中所需的硅通孔数量,为有源晶体管释放了更多的面积,并优化了裸片的尺寸。

ODI属于另一种优化,通过添加 ODI 封装技术能为客户带来更多定制化的方案。

总结

“仅仅将英特尔这一封装技术引起的芯片设计制造变革称作“小改变”,过于轻描淡写了”,Swan如是说。

通过上文的内容来看,实际上英特尔推进的现今封装技术,不仅达到了晶体管的级别,使得成为摩尔定律探索的新关键,还与未来新架构息息相关。

自从英特尔推出英特尔代工服务(IFS)后,现今的封装技术不仅吸引了潜在代工客户,还使英特尔能够提供各种领先产品。

在笔者看来,在摩尔定律逐渐逼近极限之时,未来集成电路行业在后摩尔时代不仅要着眼于半导体材料、结构和工艺,还要注意封装互连技术对晶体管的影响,或许这是未来破局的关键。

在第一颗7nm芯片诞生之后,每次制程的提高都会有着摩尔定律将死的语言。反观行业,已逐渐显露一些对1nm制程后的研究成果。

最后,笔者想要引用一句非常喜欢的话:“每一次遇到摩尔定律的极限,我们都能车到山前必有路,找到新的方向和发展空间,摩尔定律不会死去,会死的或许只是跟不上时代前进的公司。”

图片新闻

技术文库

最新活动更多

-

即日-3.27立即报名>> 【在线直播】解密行业检测流量密码——电子与半导体行业

-

3月27日立即报名>> 【工程师系列】汽车电子技术在线大会

-

即日-3.28立即报名>>> 【在线会议】汽车检测的最佳选择看这里

-

即日-3.31立即报名>>> 【在线会议】AI加速卡中村田元器件产品的技术创新探讨

-

4月1日立即下载>> 【村田汽车】汽车E/E架构革新中,新智能座舱挑战的解决方案

-

4日10日立即报名>> OFweek 2025(第十四届)中国机器人产业大会

推荐专题

分享

分享

发表评论

请输入评论内容...

请输入评论/评论长度6~500个字

暂无评论

暂无评论