4日10日 OFweek 2025(第十四届)中国机器人产业大会

立即报名 >>>

7.30-8.1 全数会2025(第六届)机器人及智能工厂展

火热报名中>>

计算隔离式精密高速DAQ的采样时钟抖动的简单步骤

作者:Lloben Paculanan,ADI 应用开发工程师

John Neeko Garlitos,ADI 产品应用工程师

简介

出于鲁棒性、安全性、高共模电压考量,或为了消除可在测量中带来误差的接地环路,许多数据采集(DAQ)应用都需要隔离DAQ信号链路径。ADI的精密高速技术使系统设计人员能够在相同的设计中实现高交流和直流精度,无需牺牲直流精度来换取更高的采样速率。然而,为实现高交流性能,如信噪比(SNR),系统设计人员必须考虑采样时钟信号或控制ADC中采样保持(S&H)开关的转换启动信号上的抖动所带来的误差。随着目标信号和采样速率的增加,控制采样保持开关的信号抖动会成为主要误差源。

当DAQ信号链被隔离之后,控制采样保持开关的信号一般来自进行多通道同步采样的背板。系统设计人员选择低抖动数字隔离器至关重要,以使进入ADC的采样保持开关的控制信号具有低抖动。精密高速ADC应首选使用LVDS接口格式,以满足高数据速率要求。它还会对DAQ电源层和接地层带来极小的干扰。本文将说明如何解读ADI公司的LVDS数字隔离器的抖动规格参数,以及与精密高速产品(例如ADAQ23875DAQ μModule?解决方案)接口时,哪些规格参数比较重要。本文的这些指导说明也适用于其他带有LVDS接口的精密高速ADC。在介绍与ADN4654千兆LVDS隔离器配合使用的ADAQ23875时,还将说明计算对SNR预期影响采用的方法。

抖动如何影响采样过程

通常,时钟源在时域中存在抖动。在设计DAQ系统时,了解时钟源中包含多少抖动是非常重要的。

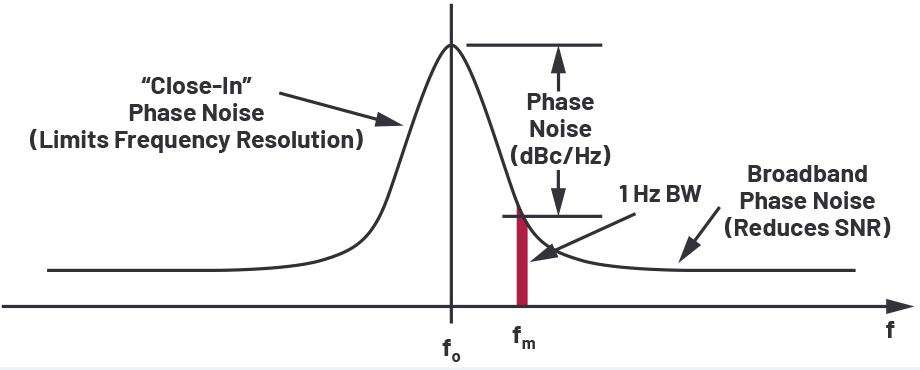

图1展示了非理想型振荡器的典型输出频谱,在1 Hz带宽时噪声功率与频率成函数关系。相位噪声的定义为指定频率偏移fm下1 Hz带宽内的噪声与基波频率fo下振荡器信号幅度的比率。

图1.受相位噪声影响的振荡器功率频谱

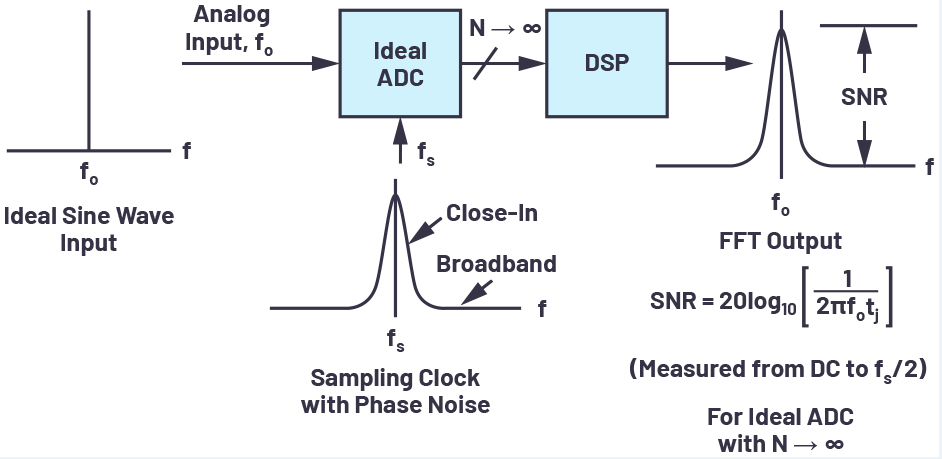

采样过程是采样时钟与模拟输入信号的乘法。这种时域中的乘法相当于频域中的卷积。所以,在ADC转换期间,ADC采样时钟的频谱与纯正弦波输入信号卷积,使得采样时钟或相位噪声上的抖动出现在ADC输出数据的FFT频谱中,具体如图2所示。

图2.带相位噪声采样时钟对理想正弦波采样的影响

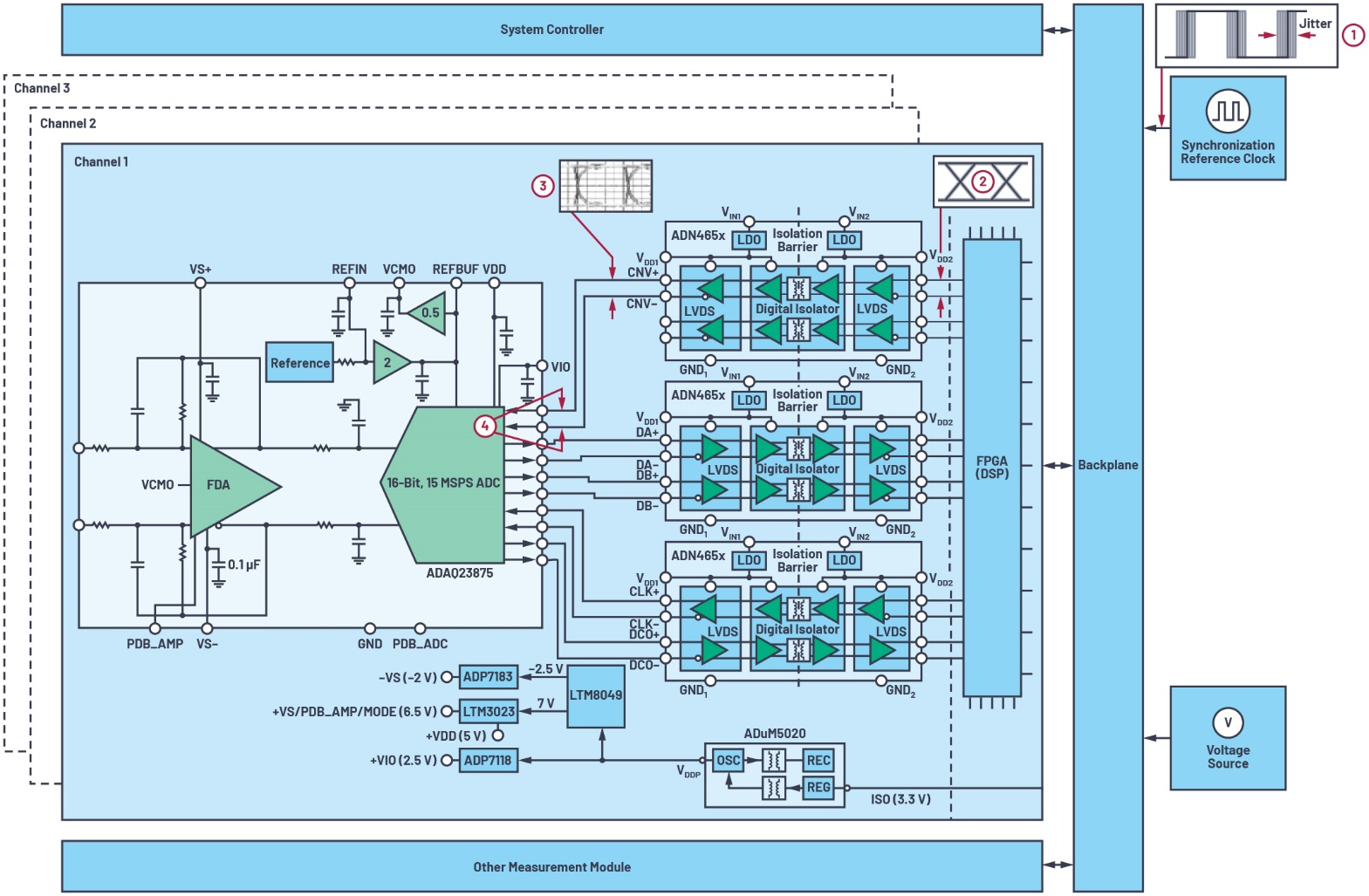

隔离式精密高速DAQ应用

多相功率分析仪就是一个隔离式精密高速DAQ应用示例。图3显示典型的系统架构,其中通道与通道之间隔离,通过共用背板用于与系统计算或控制器模块通信。在本示例中,我们选择ADAQ23875精密高速DAQ解决方案,因为其尺寸小,所以能够在狭小空间内轻松安装多个隔离DAQ通道,从而可以减轻现场测试应用中移动仪器的重量。使用LVDS千兆隔离器(ADN4654)将DAQ通道与主机箱背板隔离。

通过隔离每个DAQ通道,可以在不损坏输入电路的情况下,将每个通道直接连接至具有不同共模电压的传感器。每个隔离DAQ通道的接地跟踪具有一定电压偏移的共模电压。如果DAQ信号链能够跟踪与传感器相关的共模电压,就无需使用输入信号调理电路来支持较大的输入共模电压,并消除对下游电路来说较高的共模电压。这种隔离还可带来安全性,并消除可能会影响测量精度的接地环路。

在功率分析仪应用中,在所有DAQ通道中实现采样事件同步至关重要,因为与采样电压相关的时域信息不匹配会影响后续计算和分析。为了在通道间同步采样事件,ADC采样时钟通过LVDS隔离器从背板发出。

在图3所示的隔离式DAQ架构中,以下这些抖动误差源会增加控制ADC中采样保持开关的采样时钟上的总抖动。

1. 参考时钟抖动

采样时钟抖动的第一来源是参考时钟。该参考时钟通过背板传输至每个隔离式精密高速DAQ模块和其他插入背板的测量模块。该时钟用作FPGA的时序参考;所以,FPGA中的所有事件、数字模块、PLL等的时序精度都取决于参考时钟的精度。在没有背板的某些应用中,使用板载时钟振荡器作为参考时钟源。

2. FPGA抖动

采样时钟抖动的第二来源是FPGA带来的抖动。注意,FPGA中包含一条触发-执行路径,并且FPGA中PLL和其他数据模块的抖动规格都会影响系统的整体抖动性能。

3. LVDS隔离器抖动

采样时钟抖动的第三来源是LVDS隔离器。LVDS隔离器产生附加相位抖动,会影响系统的整体抖动性能。

4. ADC的孔径抖动

采样时钟抖动的第四来源是ADC的孔径抖动。这是ADC本身固有的特性,请参阅数据手册查看具体定义。

图3.通道与通道之间的隔离DAQ架构

有些参考时钟和FPGA抖动规格基于相位噪声给出。要计算对采样时钟的抖动贡献,需要将频域中的相位噪声规格转化为时域中的抖动规格。

根据相位噪声计算抖动

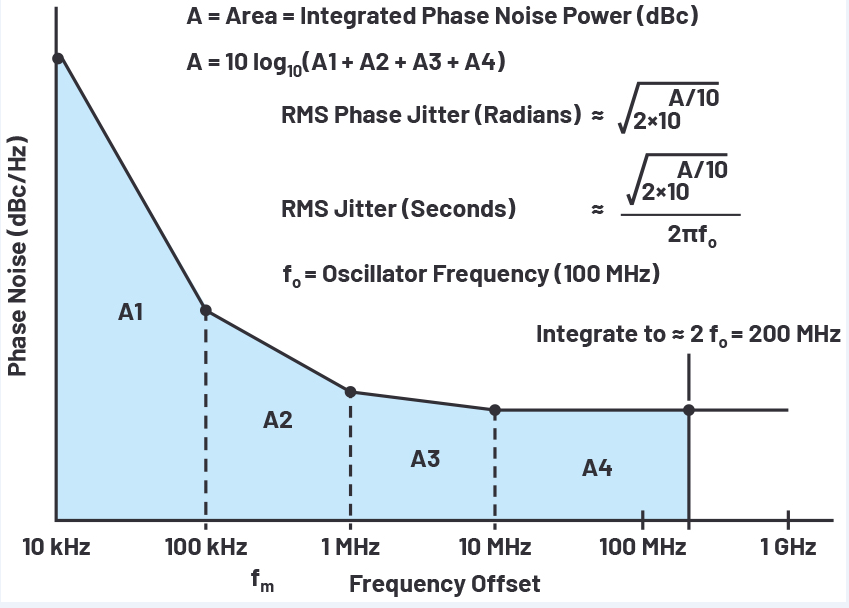

相位噪声曲线有些类似于放大器的输入电压噪声频谱密度。与放大器电压噪声一样,最好在振荡器中使用1/f低转折频率。振荡器通常用相位噪声来描述性能,但为了将相位噪声与ADC的性能关联起来,必须将相位噪声转换为抖动。为将图4中的图与现代ADC应用关联起来,选择100 MHz的振荡器频率(采样频率)以便于讨论,典型曲线如图4所示。请注意,相位噪声曲线由多条线段拟合而成,各线段的端点由数据点定义。

图4.根据相位噪声计算抖动

计算等量rms抖动时,第一步是获取目标频率范围中的积分相位噪声功率,即曲线区域A。该曲线被分为多个独立区域(A1、A2、A3和A4),每个区域由两个数据点定义。假设振荡器与ADC输入端之间无滤波,则积分频率范围的上限应为采样频率的2倍,这近似于ADC采样时钟输入的带宽。积分频率范围下限的选择也需要一定的斟酌。理论上,它应尽可能低,以便获得真实的rms抖动。但实际上,制造商一般不会给出偏移频率小于10 Hz时的振荡器特性,不过这在计算中已经能够得出足够精度的结果。多数情况下,如果提供了100 Hz时的特性,则选择100 Hz作为积分频率下限是合理的。否则,可以使用1 kHz或10 kHz数据点。还应考虑,近载波相位噪声会影响系统的频谱分辨率,而宽带噪声则会影响整体系统信噪比。最明智的方法或许是对各区域分别积分,并检查各区域的抖动贡献幅度。如果使用晶体振荡器,则低频贡献与宽带贡献相比,可能可以忽略不计。其它类型的振荡器在低频区域可能具有相当大的抖动贡献,必须确定其对整体系统频率分辨率的重要性。各区域的积分产生个别功率比,然后将各功率比相加,并转换回dBc。已知积分相位噪声功率后,便可通过下式计算rms相位抖动(单位为弧度):

以上结果除以2πf0,便可将用弧度表示的抖动0转换为用秒表示的抖动:

更多详细信息,请参阅“MT-008教程:将振荡器相位噪声转化为时间抖动”。

量化参考时钟抖动

高性能DAQ系统中使用的参考时钟源一般为晶体振荡器,与其他时钟源相比,它可以提供更出色的抖动性能。

我们一般使用表1所示的示例在数据手册中定义晶体振荡器的抖动规格。在量化参考时钟的抖动贡献时,相位抖动是最重要的规格指标。相位抖动通常定义为边沿位置相对于平均边沿位置的偏差。

表1.数据手册中给出的晶体振荡器抖动规格示例

符号 | 参数 | 测试条件 | 最小值 | 典型值 | 最大值 | 单位 | |

JPER | 周期抖动,rms | LVDS | — | XXX | — | ps | |

LVPECL | — | XXX | — | ||||

LVCMOS | fOUT = 125 MHz | — | XXX | — | |||

RJ | 随机抖动,rms | LVDS | — | XXX | — | ps | |

LVPECL | — | XXX | — | ||||

LVCMOS | fOUT = 125 MHz | — | XXX | — | |||

DJ | 确定性抖动 | LVDS | — | XXX | — | ps | |

LVPECL | — | XXX | — | ||||

LVCMOS | fOUT = 125 MHz | — | XXX | — | |||

TJ | 总抖动 | LVDS | — | XXX | — | ps | |

LVPECL | — | XXX | — | ||||

LVCMOS | fOUT = 125 MHz | — | XXX | — | |||

fJITTER | 相位抖动 (12 kHz至20 MHz) | LVDS | — | XXX | — | fs | |

LVPECL | — | XXX | — | ||||

LVCMOS | fOUT = 125 MHz | — | XXX | — | |||

另一方面,有一些晶体振荡器指定相位噪声性能,而不是指定抖动。如果振荡器数据手册定义了相位噪声性能,可以将噪声值转化为抖动,如“根据相位噪声计算抖动”部分所述。

量化来自FPGA的抖动

FPGA中参考时钟的主要作用是提供触发信号,以启动FPGA中设定的不同并行事件。换句话说,参考时钟协调FPGA中的所有事件。为了提供更好的时间分辨率,参考时钟通常被传递到FPGA中的PLL,以增大其频率,因此,可能出现短时间隔事件。此外,需注意FPGA中包含一条触发-执行路径,其中,参考时钟被传递至时钟缓冲器、计数器、逻辑门等。处理抖动敏感型重复事件(例如,通过隔离将LVDS转化-开始信号提供给ADC)时,需要量化来自FPGA的抖动贡献,以合理预估整体系统抖动对高速数据采集性能的影响。

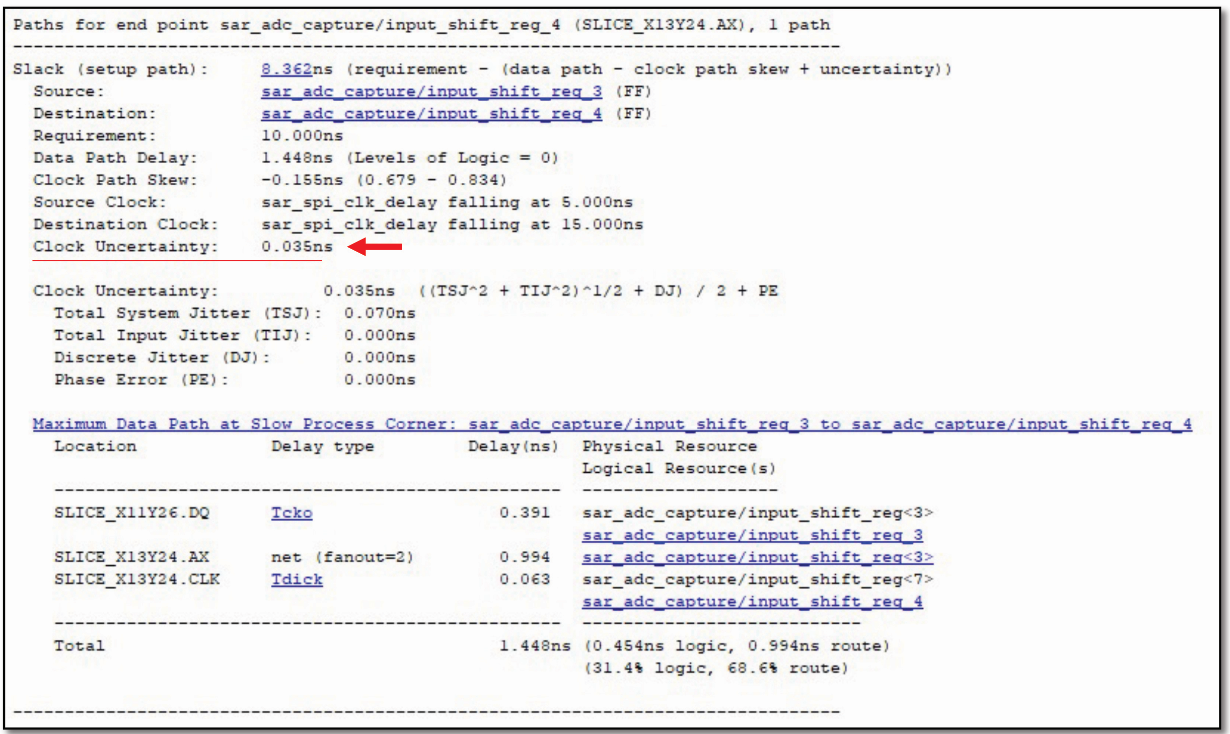

FPGA的抖动性能通常在FPGA数据手册中给出。也会在大部分FPGA软件工具的静态时序分析(STA)中给出,如图5所示。时序分析工具可以计算数据路径源和目的地的时钟不确定性,并将它们组合以获得总时钟不确定性。为了自动在STA中计算参考时钟抖动量,必须在FPGA项目中将其添加为输入抖动约束。

图5.静态时序分析(STA)示例视图

量化数字隔离产生的抖动

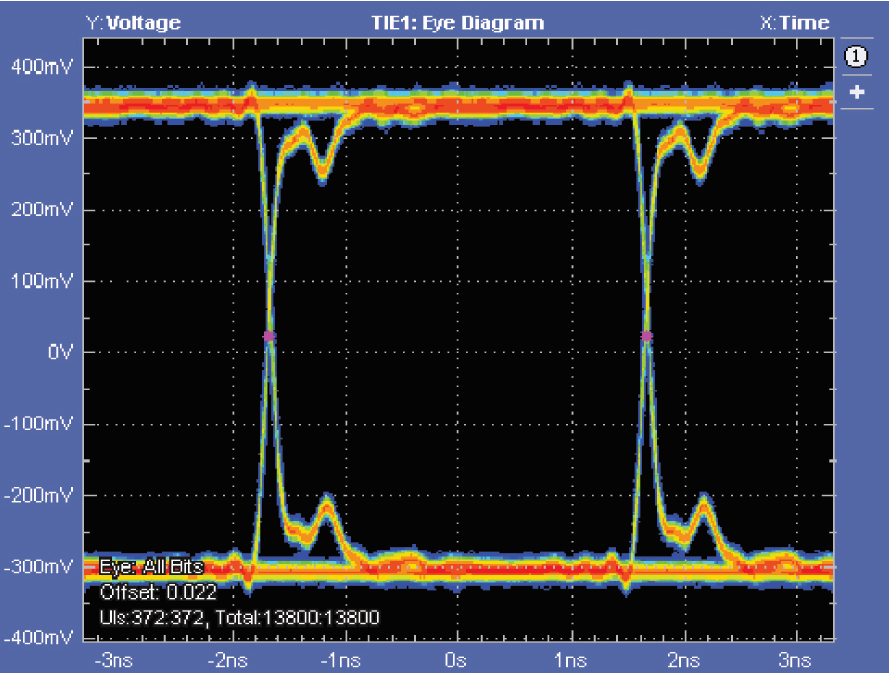

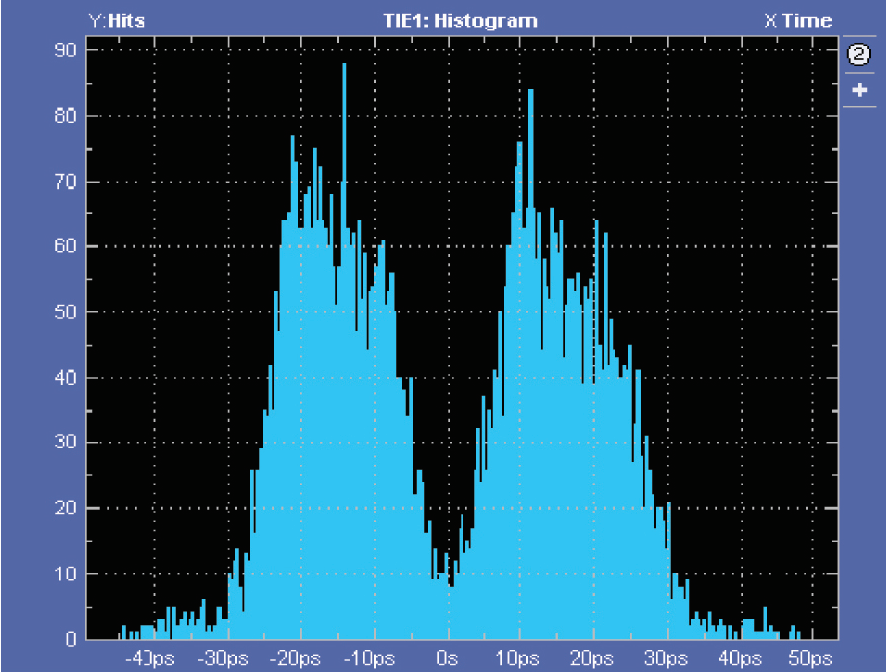

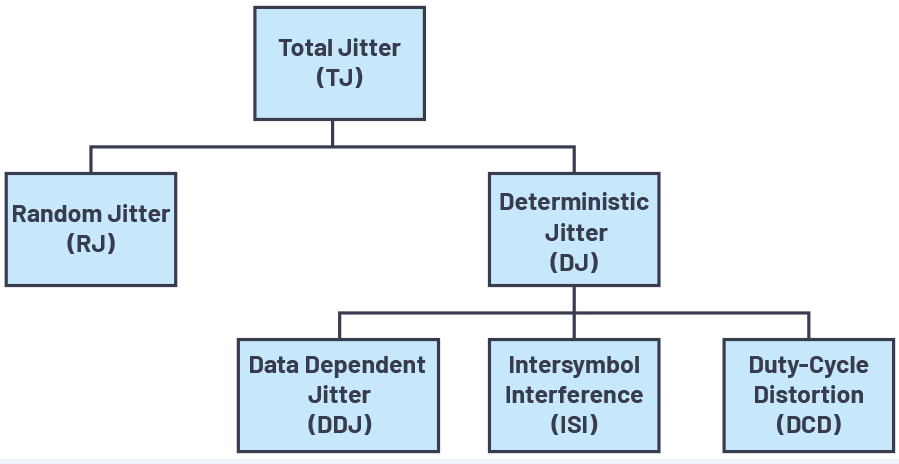

查看抖动的最基本方法是用差分探针去测量LVDS信号对,并且上升沿和下降沿上均要触发,示波器设定为无限持续。这意味着高至低和低至高的跃迁会相互迭加,因此可以测量交越点。交越宽度对应于峰峰值抖动或截至目前所测得的时间间隔误差(TIE)。比较图6和图7所示的眼图和直方图。有一些抖动是随机来源(例如热噪声)所导致,此随机抖动(RJ)意味着示波器上所看到的峰峰值抖动会受到运行时间的限制(随着运行时间增加,直方图上的尾巴会升高)。

图6.ADN4651的眼图

图7. ADN4651的眼图直方图

相比之下,确定性抖动(DJ)的来源是有界限的,例如脉冲偏斜所导致的抖动、数据相关抖动(DDJ)和符码间干扰(ISI)。脉冲偏斜源于高至低与低至高传输延迟之间的差异。这可以通过偏移交越实现可视化,即在0 V时,两个边沿分开(很容易通过图7中直方图内的分隔看出来)。DDJ源于不同工作频率时的传输延迟差异,而ISI源于前一跃迁频率对当前跃迁的影响(例如,边沿时序在一连串的1s或0s与1010模式码之后通常会有所不同)。

图8.总抖动贡献来源

图8显示如何充分估算特定误码率下的总抖动(TJ@BER)。可以根据模型与测量所得的TIE分配之间的拟合状态来计算随机抖动和确定性抖动。此类模型中的一种是双狄拉克模型,它假设高斯随机分布与双狄拉克δ函数卷积(两个狄拉克δ函数之间的分隔距离对应于确定性抖动)。对于具有明显确定性抖动的TIE分布而言,该分布在视觉上近似于此模型。有一个难点是某些确定性抖动会对高斯分量带来影响,亦即双狄拉克函数可能低估确定性抖动,高估随机抖动。然而,两者结合仍能精确估计特定误码率下的总抖动。

随机抖动规定为高斯分布模型中的1 σ rms值,若要推断更长的运行长度(低BER),只需选择适当的多σ,使其沿着分布的尾端移动足够长的距离(例如,1 × 10-12位错误需要14 σ)即可。接着加入DJ以提供TJ@BER的估计值。对于信号链中的多个元件,与其增加会导致高估抖动的多个TJ值,不如将RJ值进行几何加总,将DJ值进行代数加总,这样将能针对完整的信号链提供更为合理的完整TJ@BER估计。

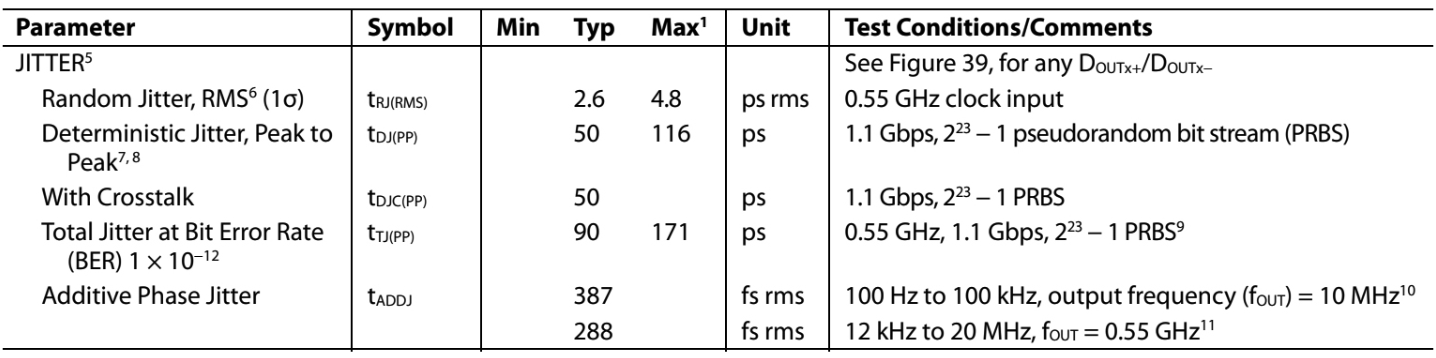

ADN4654的RJ、DJ和TJ@BER全都是分别指定的,依据多个单元的统计分析提供各自的最大值,藉以确保这些抖动值在电源、温度和工艺变化范围内都能维持。

图9显示ADN4654 LVDS隔离器的抖动规格示例。对于隔离式DAQ信号链,附加相位抖动是最重要的抖动规格。附加相位抖动与其他抖动源一起使ADC孔径抖动增加,从而导致采样时间不准确。

图9.ADN4654抖动规格

量化ADC的孔径抖动

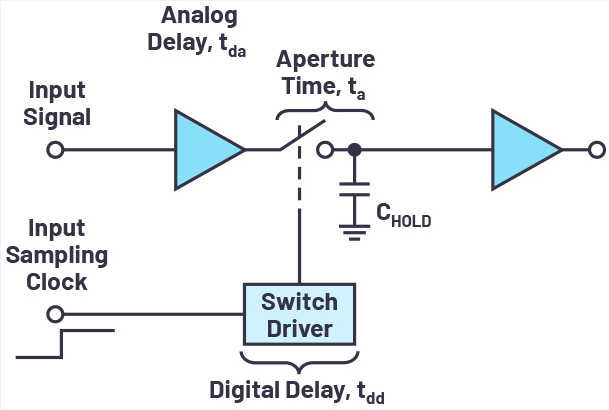

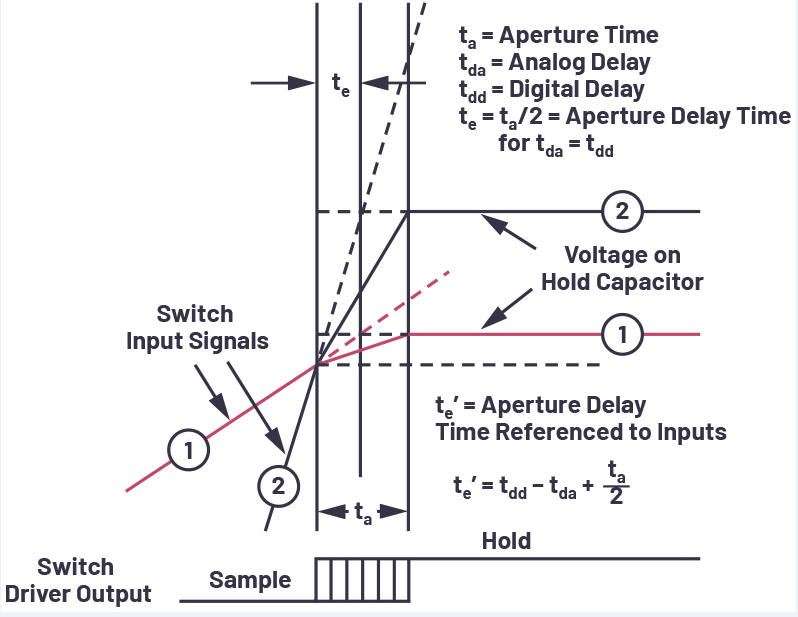

孔径抖动是ADC的固有特性。这是由孔径延迟中的样本间变化引起的,与采样事件中的误差电压对应。在开关断开的时刻,这种样本间变化称为“孔径不确定性”或“孔径抖动”,通常用均方根皮秒(ps rms)来衡量。

在ADC中,如图10和图11所示,孔径延迟时间以转换器输入作为基准;应考虑通过输入缓冲器的模拟传输延迟ta的影响;以及通过开关驱动器的数字延迟tdd的影响。以ADC输入为基准,孔径时间ta’定义为前端缓冲器的模拟传播延迟tda与开关驱动器数字延迟tdd的时间差加上孔径时间的一半ta/2。

图10.ADC的采样保持输入级

图11.采样保持波形和定义

以ADAQ23875为例,孔径抖动仅约0.25 psRMS,如图12所示。此规格通过设计保证,但未经测试。

图12.ADAQ23875孔径抖动

整体采样时钟抖动

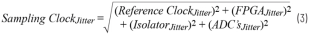

量化图3所示的四大模块各自的抖动贡献之后,可以取四个抖动源的和方根(RSS)来计算控制采样保持开关的信号(或时钟)的整体抖动性能。

另一方面,如果使用了STA,则简化的时钟抖动计算公式为:

采样时钟抖动对SNR的影响

对控制采样保持开关的信号的整体抖动进行量化之后,现在可以量化抖动对DAQ信号链的SNR性能的影响程度。

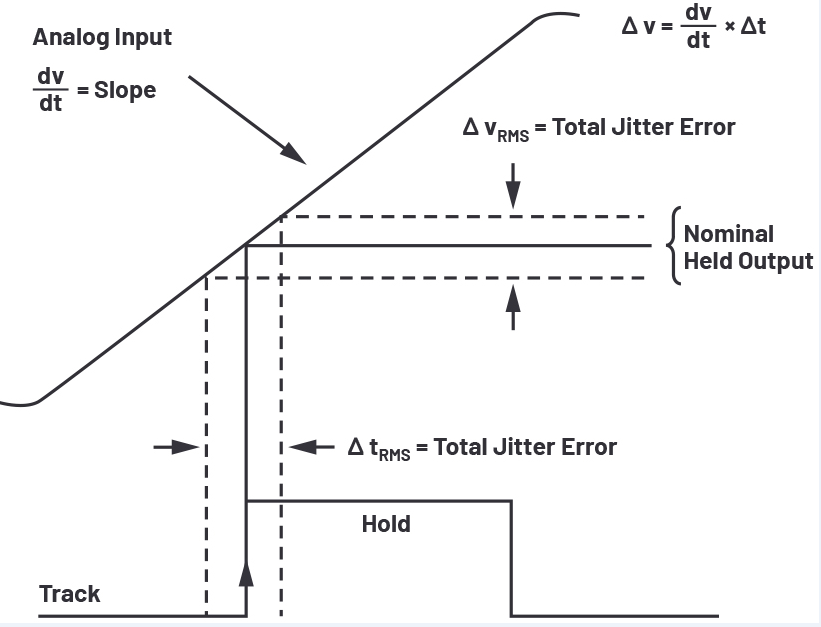

Figure13 illustrates theerror due tojitter on thesampling clock.

图13显示采样时钟上的抖动所造成的误差。

图13.采样时钟抖动造成的影响

通过下面的简单分析,可以预测采样时钟抖动对理想ADC的SNR的影响。

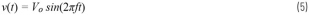

假设输入信号由下式给出:

该信号的变化速率由下式给出:

![]()

![]()

将幅度2πfVO除以√2可以获得dv/dt的rms。现在令ΔVrms = rms电压误差,Δt = rms孔径抖动tj,并代入这些

值:

求解ΔVrms:

![]()

满量程输入正弦波的rms值为VO/√2。因此,rms信号与rms噪声的比值(用dB表示)由频率给出:

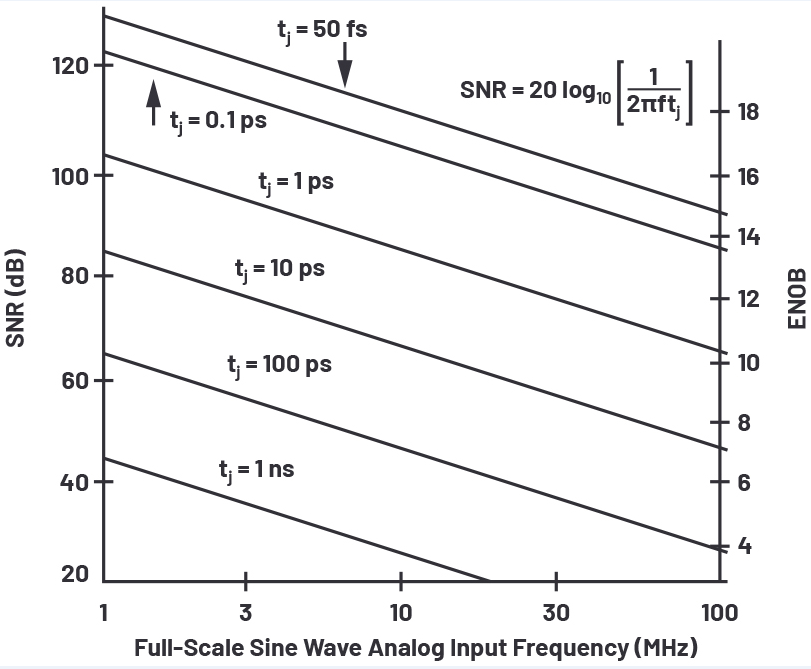

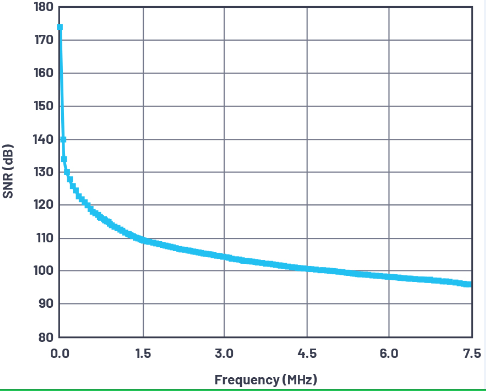

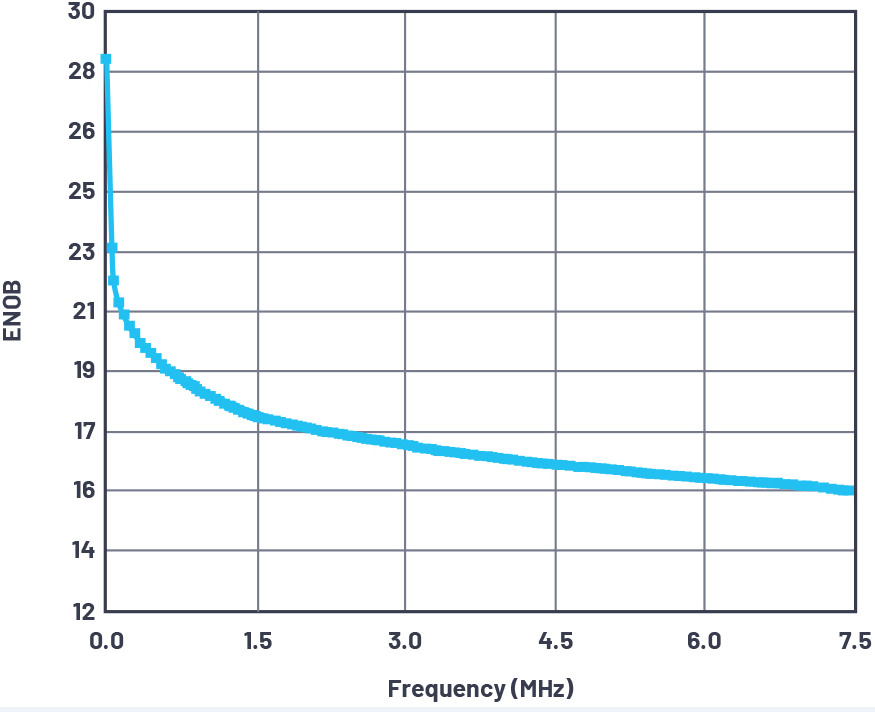

该公式假设ADC具有无限的分辨率,孔径抖动是决定SNR的唯一因素。图14给出了该公式的图形,它说明孔径和采样时钟抖动对SNR和ENOB有严重影响,特别是当输入/输出较高时。

图14.抖动引起的数据转换器理论SNR和ENOB与满量程正弦波输入频率的关系

ADAQ23875和ADN4654采样时钟抖动理想SNR计算

ADAQ23875的孔径抖动(典型值)为250 fs rms,ADN4654的附加相位抖动为387 fs rms (fOUT = 1 MHz)。在这种情况下,我们暂且不考虑参考时钟和FPGA的抖动贡献。

现在,根据ADC和隔离器的抖动规格,我们可以使用以下公式计算总rms抖动:

图14和图15显示了计算得出的隔离式精密高速DAQ系统的最大SNR和ENOB性能。SNR和ENOB随输入频率降低,与图13中所示的SNR理论图一致。

图15.针对ADAQ23875和ADN4654计算得出的SNR的最大值

图16.针对ADAQ23875和ADN4654计算得出的ENOB的最大值

结论

控制ADC中采样保持开关的信号(或时钟)中的抖动会影响精密高速DAQ信号链的SNR性能。在选择组成时钟信号链的各个部件时,了解会使总抖动增加的各种误差源非常重要。

当应用需要将DAQ信号链与背板隔离时,选择低附加抖动数字隔离器是保持出色的SNR性能的关键。ADI提供低抖动LVDS隔离器,可帮助系统设计人员在隔离信号链架构中实现高SNR性能。

参考时钟是采样时钟抖动的第一来源,所以需使用低抖动参考时钟以实现隔离高速DAQ的出色性能。此外,还需确保FPGA和参考时钟之间路径的信号完整性,避免路径本身带来额外误差。

致谢

作者感谢Michael Hennessy和Stuart Servis对本文的技术贡献。

参考资料

1. B. E. Boser和B. A. Wooley。“Σ-Δ调制模数转换器的设计。”IEEE固态电路杂志,第23卷第6期,1988年12月

2. Steven Harris。“采样时钟抖动对奈奎斯特采样模数转换器和过采样Σ-Δ型ADC的影响。”音频工程学会杂志,第38卷第7/8期,1990年7月/8月。

3. Kester, Walt.“MT-008教程:将振荡器相位噪声转换为时间抖动。”ADI公司,2009年。

4. Derek Redmayne、Eric Trelewicz和Alison Smith。“了解时钟抖动对高速ADC的影响。”ADI公司,2006年。

作者简介

Lloben Paculanan是ADI菲律宾GT公司的产品应用工程师。他于2000年加入ADI公司,先后担任多个测试硬件开发和应用工程职位;一直从事精密高速信号链μModule开发。他拥有美国泽维尔大学Ateneo de Cagayan学院工业工程技术学士学位,以及Enverga University的计算机工程学士学位。

John Neeko Garlitos是ADI公司的信号链μModule解决方案产品应用工程师。他从事信号链μModule开发,以及适用于Circuits from the Lab和参考电路的嵌入式软件工作。他于2017年开始在ADI菲律宾GT公司工作。他拥有菲律宾科技大学沙鄢分校电子工程理学士学位,以及菲律宾迪里曼大学电子工程硕士学位。

图片新闻

技术文库

最新活动更多

-

即日-3.27立即报名>> 【在线直播】解密行业检测流量密码——电子与半导体行业

-

3月27日立即报名>> 【工程师系列】汽车电子技术在线大会

-

即日-3.28立即报名>>> 【在线会议】汽车检测的最佳选择看这里

-

即日-3.31立即报名>>> 【在线会议】AI加速卡中村田元器件产品的技术创新探讨

-

4月1日立即下载>> 【村田汽车】汽车E/E架构革新中,新智能座舱挑战的解决方案

-

4日10日立即报名>> OFweek 2025(第十四届)中国机器人产业大会

推荐专题

分享

分享

发表评论

请输入评论内容...

请输入评论/评论长度6~500个字

暂无评论

暂无评论