4日10日 OFweek 2025(第十四届)中国机器人产业大会

立即报名 >>>

7.30-8.1 全数会2025(第六届)机器人及智能工厂展

火热报名中>>

PCB走线及环路面积问题的理论与数据分析!

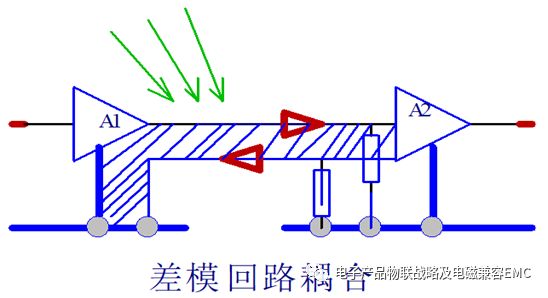

我们了解对于任意的差分信号的控制系统当其布局布线的环路面积过大时,在电磁场的作用下就有可能对系统产生影响。比如以下现象:

1 ……系统噪声

2 ……系统复位

3 ……系统死机

4 ……系统损坏

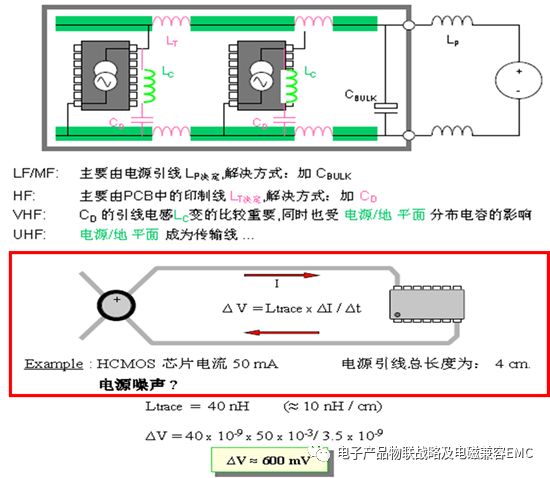

A.大的走线环路面积的走线影响的计算数据参考:

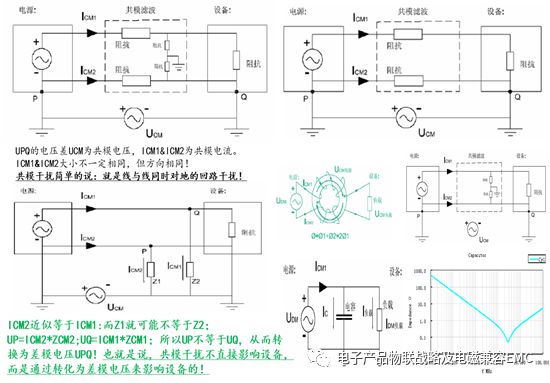

B.共模干扰对设备会产生威胁,出现产品功能及性能的问题!

我们通过基本的原理知道,共模并不能直接对我们的差分信号产生干扰,而是共模干扰信号通过差分信号线的走线阻抗不同而产生的差模干扰;让差分信号线上产生大的噪声电压从而影响到产品的功能及性能的问题;参考如下:

通过理论:系统的共模电感及Y电容的滤波措施是最直接的方法;共模电感的应用会增加系统成本;采用PCB差分信号最短对称的路径及最佳回路面积路径从而 使上图中的Z1 的阻抗近似等于Z2的阻抗;系统也不会出现产品故障及器件损坏!

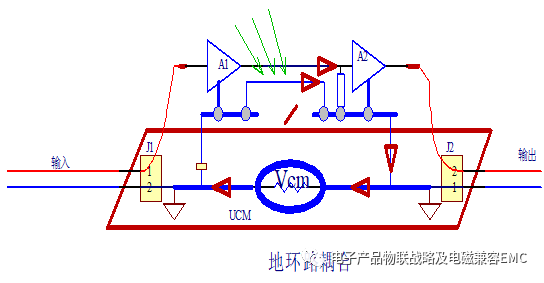

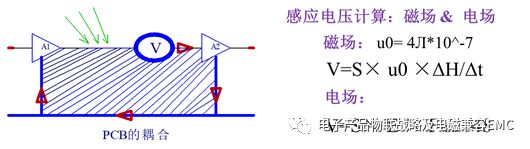

C.对于电子产品系统,我们的PCB-如何与外部产生电磁耦合:

感应电压计算:磁场 & 电场 磁场:u0= 4Л*10^-7

D.进行电子产品系统的PCB简化计算数据参考如下:

*电场问题!参数举例

è环路面积=20cm^2 测试场电压为30V/m@150MHZ , 估算感应电压

V=0.0020*30*150/48 V=200mV

*磁场问题!ESD-静电放电的场影响/参数举例

è环路面积=2cm^2 离ESD测试电流(30A)的距离=50cm , Δt=1ns

H=I/(2 × Л ×D )估算感应电压?

Δt=1ns , H=I/(2×Л×D)=30/(2*Л*0.5)=10A/m

V=0.0002*4*Л*10^-7 * 10/(1*10^-9) V=2.5V

从上面的计算可以看-大的环路面积在差分信号线产生大的噪声电压,如果超过我们允许的门限电压就会容易出现故障机理;对于采用PCB设计,如果差分信号走线是最短对称的路径及最佳回路面积路径从而 使上图中的Z1 的阻抗近似等于Z2的阻抗;系统就不容易出现产品故障及器件损坏!

注意:在走差分线的时候由于空间限制,不能达到理想的效果:电路中有高速逻辑器件时,需要走较长的布线长度时!

问题关键点:布局布线不怕长,就怕不对称或者有比较大的差,这样容易因为时延造成错误的逻辑。

注意:在走差分线的时候由于空间限制,不能完全等距等长时!

问题的关键点:等长等线宽可以保证阻抗匹配,但是不等距实际上对差分匹配会有影响,上面讲的Z1与Z2的阻抗在共模电流的影响下超过阀值门限就会造成错误的逻辑。

更多技术设计应用及技术交流;请关注阿杜老师!

杜佐兵

电磁兼容(EMC)线上&线下高级讲师

图片新闻

技术文库

最新活动更多

-

技术指南立即下载>> 电动汽车功率半导体技术趋势变化带来的挑战及解决方案

-

即日--2.7了解详情>> 【森海塞尔】TeamConnect系列产品——提升视听之体验,塑造音频之未来

-

限时免费立即试用>> 燧石技术,赋光智慧,超越感知

-

2月28日火热报名中>> 【免费试用】东集技术年终福利——免费试用活动

-

即日-3.21立即报名 >> 【深圳 IEAE】2025 消费新场景创新与实践论坛

-

4日10日立即报名>> OFweek 2025(第十四届)中国机器人产业大会

推荐专题

分享

分享

发表评论

请输入评论内容...

请输入评论/评论长度6~500个字

暂无评论

暂无评论