7.30-8.1 全数会2025(第六届)机器人及智能工厂展

火热报名中>>

总线隔离后如何实现接地?

CAN与485都是工业通信中常用的现场总线,各位工程师对于总线隔离方案想必都极为熟悉,但可能会遇到总线采用了隔离方案依旧通讯异常的情况,本文将带您一起探讨总线隔离后该如何接地?

前言

为保证总线网络的通讯稳定性,通讯接口通常会做隔离,隔离的主要目的:

安规考虑:保护设备及人身安全,隔开潜在的高压危险;

提高通信的稳定性:消除地电势差的影响;

提高器件的可靠性:消除地环路影响;

低耦合:提高系统间的兼容性。

目前实现总线隔离有两种方案:采用分立元器件搭建或采用集成模块。

隔离接地的原理

总线增加隔离固然可以保证总线稳定可靠地通信,但是带隔离通信接口的设备,在复杂的环境或安装状态下,接口会表现出完全不同的ESD特性,了解ESD对接口的影响机理,才能有针对性地增加保护器件,提升隔离接口的ESD能力。下面以带有隔离CAN或RS-485通信接口为例,对常见的设备状态下,ESD的作用机理进行分析,并提出相应的改善措施。

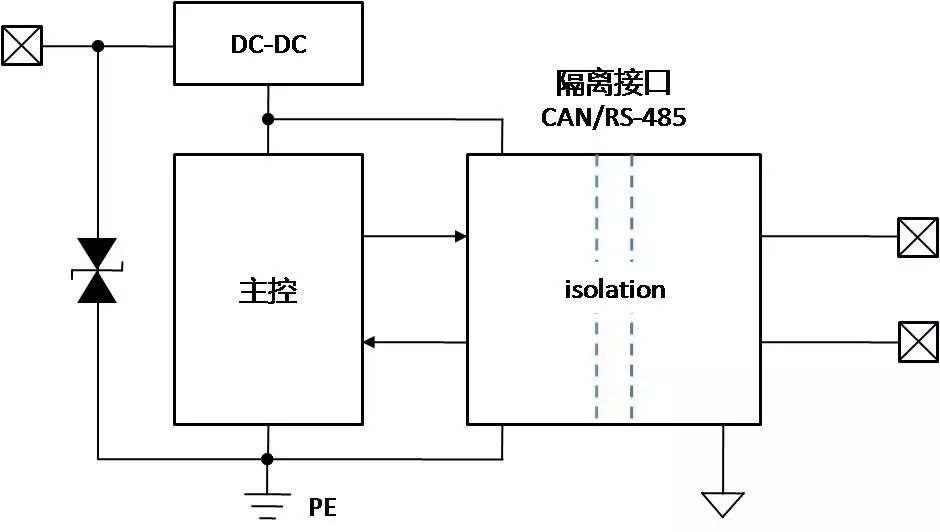

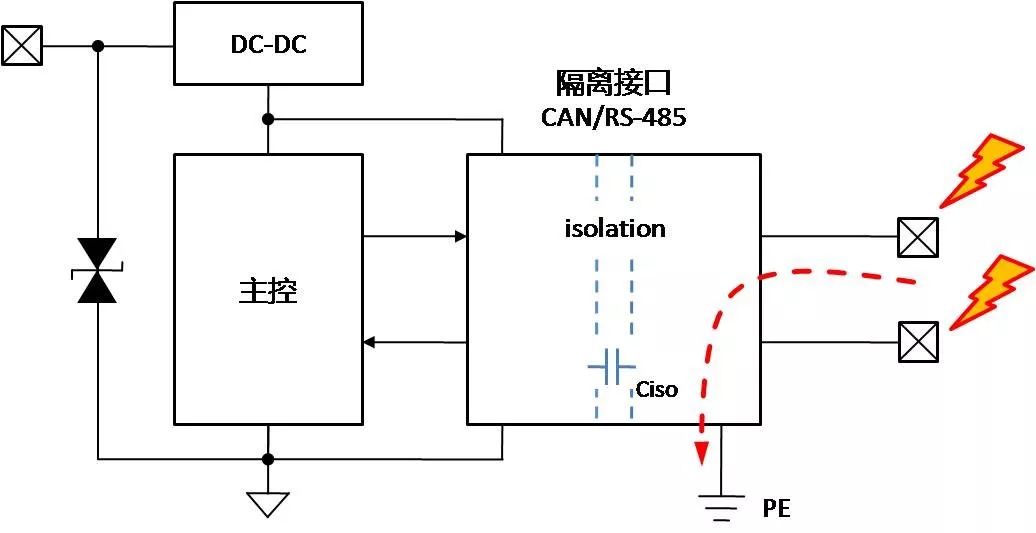

1、总线侧悬空

此状态下,设备控制侧有接入保护地(PE),总线侧参考地悬空,与PE无任何连接,如下图1。

图1

接下来进行分析:

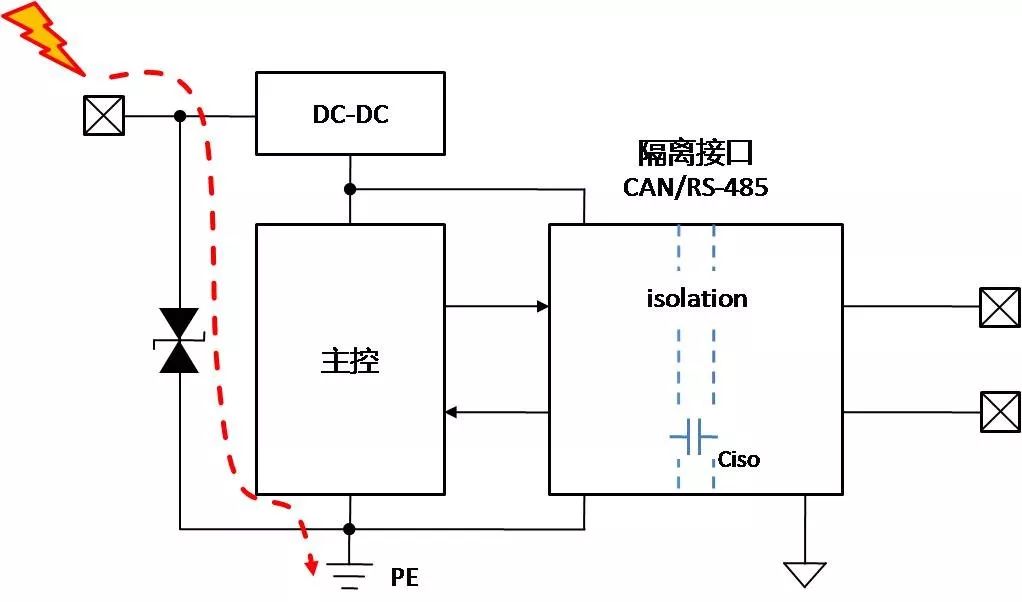

假设控制侧均做了足够的保护措施,当控制侧接口受到静电放电时,能量通过控制侧保护器泄放至PE,对隔离通信接口基本无影响,如下面图2。

当总线接口受到静电放电时,由于总线侧悬空,能量只能通过隔离栅的等效电容Ciso进行泄放,由于Ciso非常小,仅有几皮法至十几皮法,Ciso被迅速充电,两端电压Viso会非常高,几乎等同于放电电压,电压全部施加在隔离接口模块的隔离栅,若电压超出了隔离栅的电压承受范围,则会导致内部隔离栅损坏,如下面图3。

注意:对于一般的隔离接口模块,隔离栅可承受的静电放电电压只有4kV,对于更高等级的6kV或8kV的静电来说是非常脆弱的,极易出现损坏情况。

图2

图3

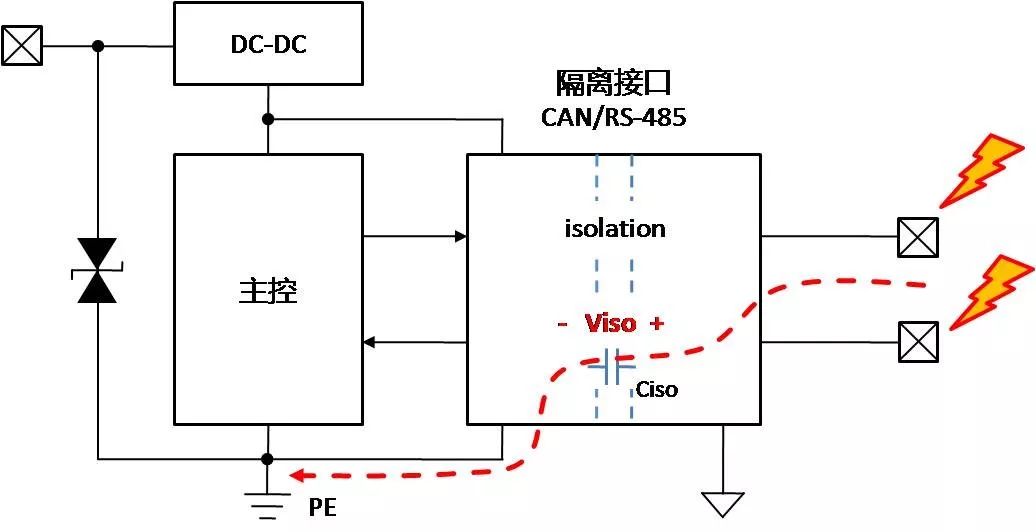

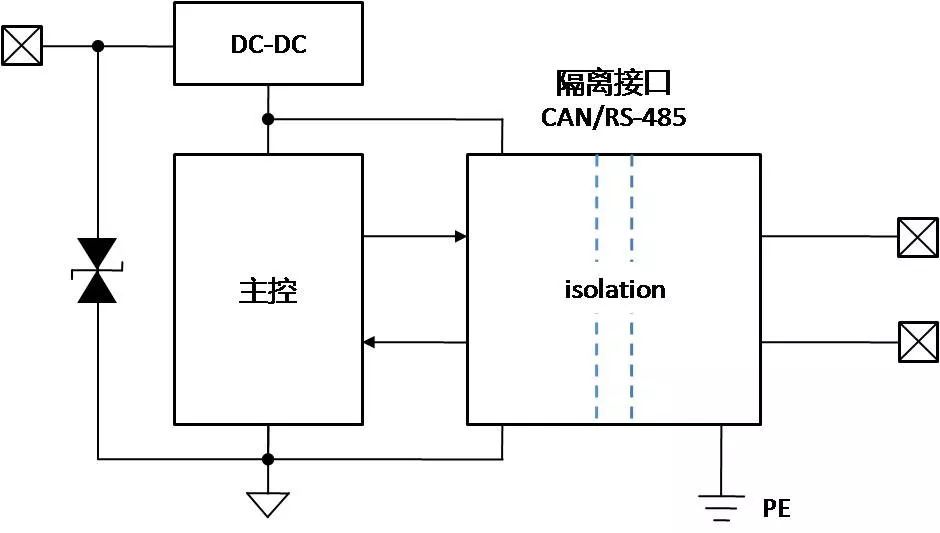

2、设备控制测悬空

此状态下,设备控制侧参考地悬空,与PE无任何连接,总线侧有接入保护地(PE),如下图4。

图4

接下来进行分析:

当总线侧接口受到静电放电时,静电能量通过隔离接口模块内部总线侧器件泄放至PE,但若ESD能量超出了接口模块内部总线侧器件的ESD抗扰能力,总线接口则可能损坏,如下面图5。

当控制侧接口受到静电放电时,由于控制侧悬空,能量只能通过隔离栅的等效电容Ciso进行泄放,由于Ciso非常小,两端电压Viso会非常高,电压全部施加在隔离接口模块的隔离栅,若电压超出了隔离栅的电压承受范围,则会导致内部隔离栅损坏,如下面图6。

图5

图6

3、改善措施

针对上述两种情况,隔离接口模块需要得到有效的静电保护,建议进行隔离接口设计时,增加Cp、Rp以及TVS,提高隔离接口的ESD抗扰能力。

电容Cp的作用:减轻隔离栅的压力,为静电能量提供一个低阻抗的路径,静电能量大部分通过此电容泄放,为达到良好效果,Cp容值应远大于Ciso,建议取100pF~1000pF之间。

TVS管的作用:对于总线侧的静电,静电能量会通过防护器件泄放,注意:其导通电压必须小于隔离接口可承受的最大电压,同时大于信号电压;在通信速率高、或节点数较多时,也需要注意尽量选取等效电容小的器件,以免影响总线正常通信。

图7

注意:若产品无安规要求,可与Cp并联一个大阻值泄放电阻,如1M,以防静电积累;若有安规要求,一般需要去除泄放电阻,同时选择安规电容。

完善的总线接口保护电路

前面只是对ESD的作用机理进行了分析,但随着工业产品对通信接口的EMC等级要求越来越高。许多应用要求满足IEC61000-4-2静电放电4级,IEC61000-4-5浪涌抗扰4级要求。一般的收发器ESD、浪涌的防护等级均比较低,如CTM1051M隔离CAN收发器的隔离耐压为2500VDC,裸机情况下,ESD、浪涌等级均较低。所以有必要增加外围电路,提高通信端口的EMC等级。

图8

以CAN总线为例,上图为完善的外围推荐电路。其中GDT置于最前端,提供一级防护,当雷击、浪涌产生时,GDT瞬间达到低阻状态,为瞬时大电流提供泄放通道,将CAN_H、CAN_L间电压钳制在二十几伏范围内。实际取值可根据防护等级及器件成本综合考虑进行调整,R3 与 R4 建议选用 PTC,D1~D6 建议选用快恢复二极管,参数表如下。

表1 推荐参数表

另一种方案则是采用ZLG的SP00S12浪涌保护模块,可用于各种信号传输系统,抑制雷击、浪涌、过压等有害信号,对设备信号端口进行保护。搭配ZLG的全隔离CTM或SC系列的隔离CAN收发器,如下图。可极大程度的提升产品的集成度,于此同时极大程度的缩小开发周期。

图9

阻容回路接地的必要性

前面讲述了总线隔离之后接地的原理以及推荐电路,想必大家已经很清楚了,在现场,很多客户会提到总线隔离之后为什么需要阻容接地呢?这里给大家简单描述一下:

1、电容:从EMS(电磁抗扰度)角度说,这个电容是在假设PE良好连接大地的前提下,降低可能存在的影响(以大地电平为参考的高频干扰信号对电路的影响),是为了抑制电路和干扰源之间瞬态共模压差的。其实GND直连PE是最好的,但是,直连可能不可操作或者不安全。从EMI(电磁干扰)角度说,如果有与PE相连的金属外壳,有这个高频路径,也能够避免高频信号辐射出来。

2、1M电阻:这是对付ESD(静电放电)测试用的。因为这种用电容连接PE和GND的系统(浮地系统),在做ESD测试的时候,打入被测电路的电荷无处释放,会逐渐累积,抬升或降低GND相对PE的电平,累积到一定程度,超过了PE和电路之间的绝缘最薄弱处所能耐受的电压范围,GND和PE之间就会放电,几个纳秒间,在PCB上的产生数十到数百安培的电流,这足以让任何电路因EMP(电磁脉冲)宕机,或者是让PE与电路之间绝缘最薄弱处所在信号连接的器件损坏。但是有时候又不能直接连接PE和GND,那么就用一个1~2M的电阻去慢慢释放这个电荷,以消除二者间的压差。当然1~2M这个数值是根据ESD测试标准选择的,因为IEC61000里面规定最高的重复次数只有10次/秒,如果你搞个1000次/秒的非标ESD放电,那么1~2M的电阻我觉得是不能释放掉累积的电荷的。

图片新闻

技术文库

最新活动更多

-

3月27日立即报名>> 【工程师系列】汽车电子技术在线大会

-

4月1日立即下载>> 【村田汽车】汽车E/E架构革新中,新智能座舱挑战的解决方案

-

即日-4.22立即报名>> 【在线会议】汽车腐蚀及防护的多物理场仿真

-

4月23日立即报名>> 【在线会议】研华嵌入式核心优势,以Edge AI驱动机器视觉升级

-

4月25日立即报名>> 【线下论坛】新唐科技2025新品发布会

-

4月30日立即参与 >> 【白皮书】研华机器视觉项目召集令

推荐专题

分享

分享

发表评论

请输入评论内容...

请输入评论/评论长度6~500个字

暂无评论

暂无评论