4日10日 OFweek 2025(第十四届)中国机器人产业大会

立即报名 >>>

7.30-8.1 全数会2025(第六届)机器人及智能工厂展

火热报名中>>

Chiplet解决芯片技术发展瓶颈及Chiplet的未来

在今年的举办的Computex上,AMD发布了基于3D Chiplet技术的3D V-Cache。该技术采用了台积电的3D Fabric先进封装技术,成功地将含有64MB L3 Cache的Chiplet以3D堆叠的形式与处理器封装在了一起。

不止是AMD和台积电,英特尔也在多个产品中采用了Chiplet技术。在架构日中,英特尔发布的下一代至强可扩展处理器Sapphire Rapids 就采用了2.5D的嵌入式桥接解决方案。

在后摩尔时代,随着芯片节点逐渐逼近物理极限,每一代半导体工业节点提升对于芯片性能带来的收益越来越小,Chiplet逐渐成为了巨头们追逐的焦点。

延续摩尔定律的关键

小芯片(Chiplet)技术被视为延缓半导体摩尔定律的解方,它的概念其实很简单就是硅片级别重用。将一个芯片组成的处理器划分为多个芯片,分别是:数据存储、计算、信号处理、数据流管理等功能,然后再将它们连接在一起形成一个<小芯片>的芯片网络。

如今不同类型的计算和工作负载呈现爆炸式增长,也出现了许多不同的架构来支持不同类型的计算模型。所以异构集成成为延续摩尔定律性能趋势的一种方式。

Chiplet像是搭积木的方式,它是一类满足特定功能的die,我们称它为模块芯片。Chiplet模式是通过die-to-die内部互联技术将多个模块芯片与底层基础芯片封装在一起,构成多功能的异构System in Packages(SiPs)芯片的模式。

Chiplet解决芯片技术发展瓶颈问题

为什么要发展Chiplet技术,这就需要从半导体工艺制程提升的难度和SoC研发所面临的问题出发。

SoC是以超深亚微米工艺技术和知识产权核IP复用技术为支撑,将系统所需的处理器、存储器、模拟电路模块、数模混合信号模块以及片上可编程逻辑等高度集成到一颗芯片中,依次缩小体积,增加功能,提高性能和可靠性,还能大幅缩短产品上市时间、降低开发成本。

但随着半导体工艺的进步,在同等面积大小的区域里,要放进更多的硅电路,这就会出现一些难以解决的问题,比如:漏电流增加、散热问题增加、时钟频率增长减慢等。

国际商业战略公司首席执行官Handel Jones表示:“设计28nm芯片的平均成本为4000万美元。相比之下,设计7nm芯片的成本为2.17亿美元,设计5nm设备的成本为 4.16亿美元,3nm设计更是将耗资高达5.9亿美元。”如此昂贵的成本,并不能被大多数企业接受。

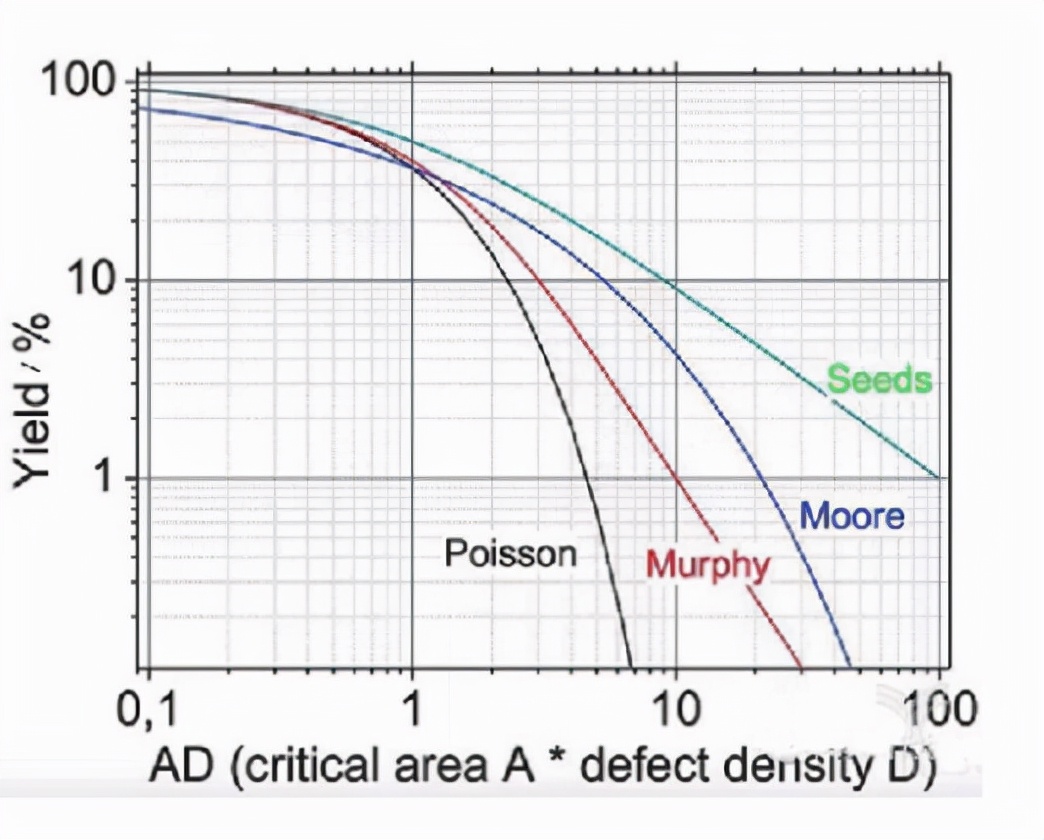

另一个是关于芯片制造的良品率,从上图中可以看出,芯片的良品率与芯片的面积有关,随着芯片面积增大,良品率会下降。掩模尺寸700mm2的设计通常会产生大约30%的合格芯片,而150mm2芯片的良品率约为80%。

将大芯片分成更小的芯片可以提高产量降低成本。

“每个小芯片都是使用与单片情况相同的标准光刻程序制造的,以生产更多数量的较小小芯片。然后单个小芯片进行 KGD 测试。现在,对于与单片情况相同的故障分布,每个潜在缺陷导致仅丢弃大约四分之一的硅量。小芯片可以单独测试,然后重新组装并封装到完整的最终 SoC 中。总体结果是,每个晶圆都可以产生数量明显更多的功能性 SoC。”上图示意了一个假设的单片32核处理器。

The Linley Group 的优秀白皮书“Chiplets Gain Rapid Adoption: Why Big Chips Are Getting Small”中直接提出,Chiplet技术可以将大型7nm设计的成本降低高达25%;在5nm及以下的情况下,节省的成本更大。

AMD的小芯片之路

AMD率先提出Chiplet模式,在2019年全面采用小芯片技术获得了技术优势。AMD构建了自己的Chiplet生态体系,生产了Ryzen和Epyc x86处理器,并且自使用7nm制程生产Zen2 CPU内核后,CPU的性能比以前的制程提高了15%。

在Hot Chips上AMD展示了其最新的Zen3微结构,增加了 CCX(核心复合体)内的核心数量,单芯片集成15个Die。在 Zen 2 中,一个八核小芯片有两个四核 CCX,每个都连接到主 IO 芯片,但在 Zen 3 中,单个 CCX 增长到八核,并且每个小芯片仍保持八核。

AMD 计划在 2022 年底之前推出其 EPYC 4 Genoa 处理器和 Zen 4 架构,这其中增加了很多技术支持,同时将工艺节点缩小到 5 纳米。

AMD首席执行官 Lisa Su 在演讲时表达了未来的规划,“我们与台积电就他们的 3D 结构密切合作,将小芯片封装与芯片堆叠相结合,为未来的高性能计算产品创建 3D 小芯片架构。”

英特尔对于Chiplet的布局

2018 年,英特尔将 EMIB(嵌入式多硅片)技术升级为逻辑晶圆 3D 堆叠技术。2019 年,英特尔推出 Co-EMIB 技术,能够将两个或多个 Foveros 芯片互连。

2020 年 6 月,英特尔正式发布 Lakefield 芯片,这是首款基于 Foveros 3D 立体封装技术的芯片,采用1个大核+4个小核的混合CPU设计。

今年英特尔架构日上发布的下一代Sapphire Rapids-SP Xeon CPU 是英特尔的里程碑,采用Multi-Tile Chiplet 设计,并且支持 DDR5、高带宽内存、PCIe Gen. 5.0 和计算快速链路 (CXL) 。

英特尔有自己独特的小芯片连接方式,英特尔首席工程师兼流程与产品集成总监Ramune Nagisetty有介绍,英特尔连接小芯片的方式是嵌入式多芯片互联桥。可以将其视为将两个小芯片链接在一起的高密度桥接器,一般来说经常会使用硅中介层(硅中介层是具有密集互连和内置硅通孔的硅基板,实现了芯片之间的高带宽连接)作为高级封装基板。英特尔的EMIB本质上是一块非常小的硅中介层,具有非常高密度的互连和微凸块,其密度远高于标准封装基板上的密度。

对于未来的发展,英特尔鼓励用户自主选择和设计小芯片,以搭建为自己应用优化的系统。这是英特尔正在努力构建小芯片生态的重要标志。而小芯片生态一旦形成,将会成为堪比SoC的重要芯片设计范式。

国内的Chiplet未来

芯片先进制程逐渐突破物理极限,如何把芯片封的更小成为了焦点,因此属于先进封装技术的Chiplet受到极大的关注。先进封装技术在发展的过程中,出现三个发展的方向,分别是2.5D/3D封装技术、Fan-out封装技术和Chiplet封装技术。

厦门大学微电子与集成电路系主任于大全教授认为,Chiplet技术的概念最初是从2.5D/3D IC封装演变而来,以2.5D硅通孔中介层集成CPU/GPU和存储器可以被归类为Chiplet范畴。

国内厂商也在积极布局Chiplet技术。

目前长电科技布局的多维扇出集成技术XDFOI(X-Dimensional Fan-out Integration,XDFOI)XDFOI是一种以2.5D TSV-less为基本技术平台的封装技术,在线宽/线距可达到2μm/2μm的同时,还可以实现多层布线层,以及2D/2.5D和3D多种异构封装,能够提供Chiplet及异构封装的系统封装解决方案。

在10月19日的股东大会上,通富超威的副总经理蒋澍表示,通富超威与AMD在先进封装电合作上将更加紧密,目前在Chiplet等领域已展开深度合作。上半年通富超威苏州完成AMD 6个新产品的导入,支持5nm产品导入工作;通富超威槟城进行了设备升级,以实现5nm产品的工艺能力和认证。并且根据半年报,其2.5/3D封装项目已完成立项并导入多家客户,并完成6项超大尺寸FCBGA样品生产。

在去年的全球硬科技创新大会上,业内公司与专家启动了中国Chiplet产业联盟,旨在联合AI产业相关的学术界、产业界等各方重要力量,共同制定全球Chiplet互联标准、共建 chiplet 开放平台,实现缩短芯片设计周期,降低芯片设计成本。

Chiplet赛道已经越发拥挤,发令枪声响后,谁能率先抵达终点,我们拭目以待。

图片新闻

技术文库

最新活动更多

-

即日-3.21立即报名 >> 【深圳 IEAE】2025 消费新场景创新与实践论坛

-

即日-3.25立即报名 >>> 【在线会议】医疗设备的无线共存、高速数字与射频测试

-

即日-3.27立即报名>> 【在线直播】解密行业检测流量密码——电子与半导体行业

-

3月27日立即报名>> 【工程师系列】汽车电子技术在线大会

-

即日-3.28立即报名>>> 【在线会议】汽车检测的最佳选择看这里

-

即日-3.31立即报名>>> 【在线会议】AI加速卡中村田元器件产品的技术创新探讨

推荐专题

分享

分享

发表评论

请输入评论内容...

请输入评论/评论长度6~500个字

暂无评论

暂无评论