4日10日 OFweek 2025(第十四届)中国机器人产业大会

立即报名 >>>

7.30-8.1 全数会2025(第六届)机器人及智能工厂展

火热报名中>>

打破垄断,国产接口IP成为新势力

在外部环境不断加强和国内市场急速膨胀下,国产替代风潮来袭,国内涌现大量初创企业。一直以来,国内集成电路产业链上,普遍较为关注应用层面SoC方面的开发,而在底层技术上投入有限。尤其是在核心技术链和关键供应链上仍然存在不少断点,特别是以IP为代表的关键核心环节,将有可能成为产业发展的致命罩门。

从集成电路产业构成来讲,IP属于底层技术,非常关键。值得一提的是,通常留给设计者完成热门IC设计的周期一般只有3个月,但IC的复杂度以每年55%的速率递增,设计能力每年仅提高21%,因此,IP的复用可以大大节约时间。

数据显示,去年全球50亿美元的IP销售额带动了5000亿美元的全球半导体销售额,换言之每1美元的IP支出能够带动和支撑100倍价值的芯片市场。从市场价值来看,IP的全球市场规模约为50亿美元,撬动着6000亿美元的半导体产业不断向前发展。

来源:方正证券研究所

IP的增速是IC市场增速的2倍,而接口IP市场增速又是整个IP市场增速的2倍。另据IPnest数据显示,接口IP过去5年到未来5年的全球年均复合增长率16%,而中国市场增长率更远超于此。但事实上,虽然接口IP市场前景广阔、增长迅猛之势远超想象,但国内市场自给率尚仍然不足10%,接口IP作为芯片设计上游的核心关键技术,实际已呈现“卡脖子”的态势。

接口IP普遍是EDA与IP相配合的形式

半导体IP(Intellectual Property)是经过验证的可重用的芯片设计模块,和EDA一样是芯片产业的上游核心技术。IP开发和IP复用技术大大促进了芯片设计业的快速发展。IP厂商一般采用收取前期IP许可费(IP License)+后期按芯片出货量计算的版权费(Royalty)的商业模式,以降低用户的研发投入。IP参数需求包括工艺节点、电源、功耗、性能等。

据IBS数据显示,半导体IP市场将从2018年的46亿美元增长至2027年的101亿美元,年均复合增长率为9.13%。其中数模混合(包括模拟和接口类)IP市场2018年为7.25亿美元,预计在2027年达到13.32亿美元,年均复合增长率为6.99%;射频IP市场2018年为5.42亿美元,预计在2027年达到11.24亿美元,年均复合增长率为8.44%。

过去十年间,智能手机是推动IP行业前进的强大动力,其中处理器IP受益最大,迅速成长为全球最大的IP种类,同时LPDDR、USB和MIPI等接口协议也在蓬勃发展。

下游数据爆发性增长需要更高的带宽来满足数据交换的需求,更高速的接口协议应运而生,接口IP市场得到快速发展。2019年有线接口IP约占全球IP市场22.1%,为8.7亿美元,占比相对于2018年提升2%,是增速最快的IP市场。

IPnest曾分析,从现在到 2025 年,接口IP将保持极高的增长率。根据IPnest提供的数据,接口IP 供应商在2020年的收入总额为10.68亿美元,而2019年这个数据为8.72亿美元,同比增长率为22.4%,并确认增长会是长期的迹象。

接口IP的增长动力是来自以数据为中心的应用、超多纯量(hyperscalar)、数据中心、存储、有线和无线网络以及新兴的人工智能的需求。所有这些应用都需要越来越高的带宽,从而推动 PCIe、以太网和 SerDes 或内存控制器 IP 等接口协议的增长。从热门细分市场也可以看出,5G、汽车电子、IoT、AI、云计算等领域,都需要多种不同协议的接口IP。

目前国际接口IP市场龙头企业主要包括ARM、Synopsys、CEVA、Cadence,细心的读者不难发现其中大部分企业都拥有自主的EDA。这是因为EDA和IP的商业模式很相似,而且有着共同客户,EDA与IP相配合可以提高用户黏性。

接口IP的重要性日益增长,整个IP市场的占比正在抢夺处理器IP的市场份额,成为了最具发展潜力的IP品类。在有线接口类别中,Synopsys是明显的领导者,2018年,该公司拥有约45%的市场份额,在物理IP市场则占有约35%的市场份额。而过去三年Synopsys 的IP收入占比来看,这家公司的IP收入占比正在逐年提升,带来毛利率提升。

Cadence为EDA业界第二厂商,IP行业第三厂商,在1988年由SDA与ECAD两家公司兼并而成,到1992年已占据EDA行业龙头地位,但到2008年被Synopsys超越。Cadence在IP中的定位则从2010年收购Denali开始,通过收购各自细分市场中的中小型供应商领导者来创建自己的IP产品,接口IP和DSP IP是Cadence增长的巨大动力。

国产接口IP以拿下EDA和生态作为主线据中国半导体行业协会统计,2020年中国集成电路产业销售额为8848亿元,其中设计业销售额为3778.4亿元,占比高达42.87%。我国集成电路设计业的蓬勃发展,相应而来的是对IP的大量需求,尤其是自主可控、掌握知识产权的优质国产IP。

很遗憾的是,在50亿全球IP市场需求中,当前大部分仍由全球较领先的公司提供。而这50亿美元需求中,中国市场约15亿美元,占比30%;15亿美元的中国市场中,中国本土IP公司的自给率还不到10%。

国内IP厂商虽然目前规模有限,不过就产品种类而言,国内半导体IP已经覆盖处理器和微控制器、存储器、外设及接口、模拟和混合电路、通信、图像和媒体等各类IP。虽然国内芯片设计公司的增长加大了对IP的需求,但目前仍以购买国外IP为主,本土IP产业的规模并不大。

不过,国内厂商一些先驱也早已意识到这种情况,逐步布局接口IP领域,其中包括华大九天、芯耀辉、和芯微、芯原微、吉崴微、芯动科技、锐成芯微等。

●华大九天 —— 以自有EDA工具建立独特接口IP优势

北京华大九天科技股份有限公司(简称“华大九天”)成立于2009年,一直聚焦于EDA工具的开发、销售及相关服务业务。

作为国内知名的EDA设计工具,华大九天基于自有的强大EDA工具,形成了独具优势的IC设计解决方案。华大九天目前在IP业务的布局主要聚焦在高速接口,(超)低功耗数模混合类的IP产品上,目前和国内外的foundry和设计公司都有合作,多款IP已经成功量产。

此前,华大九天曾表示,现在的IP产业,类似10至15年前EDA行业的发展状况,诸候割据,每家在做一小块业务。IP行业的并购整合也将是大势所趋。华大九天希望未来可以得到基金公司的支持,希望在IP市场上能有更大的作为。相信,这方面的效果会在未来几年中逐渐显现出来。

●芯耀辉 —— 布局EDA+IP+AI协同自动设计平台

芯耀辉科技有限公司是一家于2020年6月成立的国产IP企业,其自主研发先进工艺芯片IP产品拥有稳定性高、兼容性强、跨工艺、可移植等独特的价值和优势,服务于数字社会的各个重要领域,包括数据中心、智能汽车、高性能计算、5G、物联网、人工智能、消费电子等。

此前,芯耀辉科技有限公司联席CEO,IEEE Fellow余成斌曾经说过,“一群怀揣爱国情怀和使命感的行业专家,在经历20多年的IP相关研发后,不仅看到了国产IP占据整个市场很少部分,同时也看到了机遇,由此便成立了芯耀辉。”

值得一提的是,余成斌从事模拟集成电路设计与半导体IP产业研发工作已经快30年,在澳门曾从无到有联合创建和带领集成电路国家重点实验室之外,也同时联合创办了Chipidea澳门微电子,之后被新思科技并购,并担任Synopsys IP研发总监,一直长期专注于IP产业研发和管理。

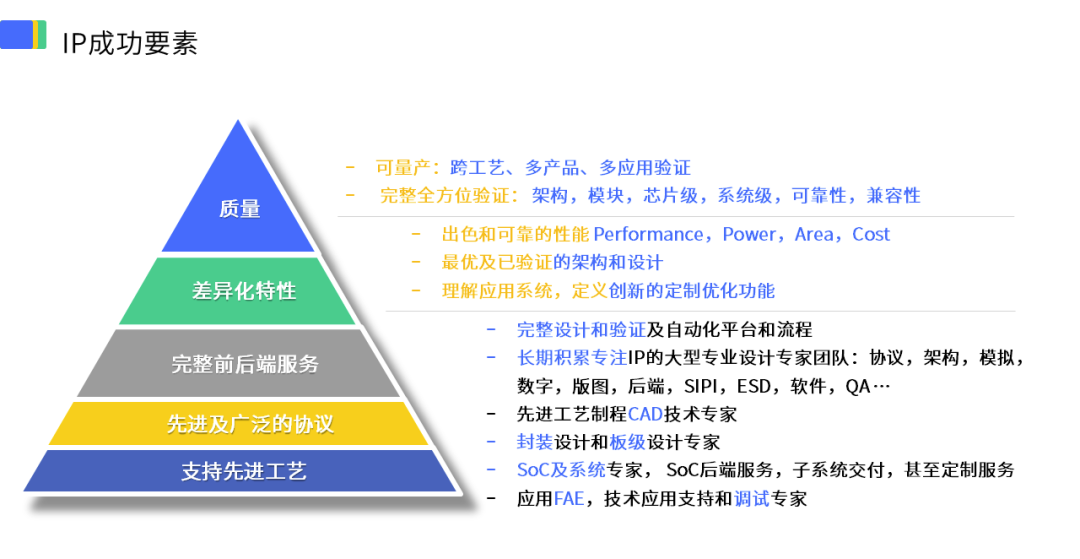

芯耀辉的整个核心团队都是来自全球排名第一的EDA和IP供应商新思科技,还有顶尖的芯片公司里面做IP的团队,包括紫光展锐、海思、英特尔、AMD、高通等。他们都在过去的公司里面有长达十几二十年一直做这些顶尖IP的经验。这一整个大型专业设计专家团队,能够做出支撑最先进工艺的IP设计,特别是在国内,芯耀辉具备了非常丰富的可以量产跨工艺、多产品、多应用验证的IP,完整前后端服务,凸显差异化特性的经验和能力。

根据余成斌的介绍,IP是经过验证的可重用的芯片设计模块,和EDA一样是芯片产业的上游核心技术。目前市场上诸如DDR、USB、PCle这些接口IP产品都是稀缺的,目前公司已完成14nm/12nm接口的布局,正在向下一代的产品研发,已陆续推出覆盖DDR、PCIe、HDMI、USB、SATA、MIPI等产品解决方案。

他认为,国内IP市场破局难点一方面在设计上极具挑战性,另一方面没有机会去一直迭代,因为迭代是需要很长时间积累的东西。“芯耀辉拥有自己成功的模式,我们会先把产业目前上游核心接口IP这块做好,从延续摩尔定律到扩展摩尔定律,我们都可以做得很好。而未来我们所规划的蓝图将是通过EDA+IP+AI协同自动设计平台去打破常规,超越摩尔定律”,余成斌如是说。

●和芯微 —— 量产数量过亿的硅验证IP

四川和芯微电子股份有限公司(以下简称“和芯微”)成立于2004年,资产总额超过两亿元,拥有自建研发中心。目前,拥有中外发明专利400多项,其中,美国专利80余项,专利申请数、授权书、国外专利申请量在成都市名列前茅。

根据其官方介绍,和芯微是中国大陆第一家掌握USB 2.0和音频编解码核心技术并实现批量生产的企业;是国家863计划IP硬化工程项目承担单位、工信部认定的集成电路设计企业、四川省高新技术企业、四川省成长型中小企业和创新型试点企业;也是国内为数不多的IP研发企业之一,也是国内规模最大的数模混合IP供应商。

从IP产品来讲,该公司拥有自主知识产权集成电路IP产品11类60余种,主要包括USB 2.0 Device/OTG/Hub PHY、16~24bit Audio CODEC、SATAII PHY、DDR2 I/O & Controller、USB 3.0 PHY和一系列的I/O Pad。经专家鉴定,公司自主开发的USB 2.0 PHY IP技术已达到国内领先、国际先进水平,量产数量过亿。传输速率高达4.8Gbps的高速串行接口技术也已通过了阶段性验证,拟投入量产。

官方强调,为客户提供经过批量生产验证和硅验证的IP产品,并应客户需求提供量身定制的个性化服务。凭借丰富的IC设计经验、多年的技术积累以及与上游代工厂和封测厂的良好互信关系,公司顺应市场需求推出了集成电路设计服务,结合自有优质IP产品,有效帮助客户缩短产品上市时间,降低产品开发风险,为客户创造更大的价值。

●芯原微 —— 自主可控IP搭建技术平台

芯原微电子(上海)股份有限公司(芯原股份,688521.SH)是一家依托自主半导体IP,为客户提供平台化、全方位、一站式芯片定制服务和半导体IP授权服务的企业。这家公司成立于2001年,总部位于中国上海,在中国和美国设有6个设计研发中心,全球共有11个销售和客户支持办事处,目前员工已超过1,300人。

其官网上显示,在芯原微独有的芯片设计平台即服务(Silicon Platform as a Service, SiPaaS)经营模式下,通过基于公司自主半导体IP搭建的技术平台,芯原可在短时间内打造出从定义到测试封装完成的半导体产品,为包含芯片设计公司、半导体垂直整合制造商(IDM)、系统厂商和大型互联网公司在内的各种客户提供高效经济的半导体产品替代解决方案。

芯原微的业务范围覆盖消费电子、汽车电子、计算机及周边、工业、数据处理、物联网等行业应用领域。其IP产品包括高清视频、高清音频及语音、车载娱乐系统处理器、视频监控、物联网连接、数据中心等;此外,芯原微还拥有6类自主可控的处理器IP,分别为图形处理器IP、神经网络处理器IP、视频处理器IP、数字信号处理器IP、图像信号处理器IP和显示处理器IP,以及1,400多个数模混合IP和射频IP。

●吉崴微电子 —— EDA、IP和先进封装一站式方案

昆山吉崴微电子科技有限公司成立于2020年3月,是美国海归半导体博士团队创办于昆山高新区的半导体设计暨仿真验证服务等新创企业。其定位是国内半导体领先的“EDA、IP和先进封装”一站式方案提供商。

据了解,吉崴微电子拥有“芯片全系统AION仿真平台”产品方案以解决我国集成电路产业发展中的关键“卡脖子”难题,并持续优化在芯片高速IO接口和系统评估等技术与能力,对SOC/封装/PCB板进行全芯片系统的性能优化为突破口,从而整合芯片设计/封装/PCB板的技术整合,并致力解决高速接口IP国产化问题。

作为一个新创年轻的科技型企业,凭借着团队的技术创新实力和企业先进经验,获得昆山市政府大力支持,目前处在高速发展中。吉崴微电子在海外拥有合作伙伴企业,协同开发新一代半导体设计的解决方案和工具设备。为客户解决技术难题、为员工创造未来、为投资者带来回报是我们努力的方向,为社会创造价值是我们的责任与担当。

“我们不会像一些公司那样追随市场而做EDA”,该公司曾表示,吉崴微电子整个EDA的定位是全球不可替代的,是唯一的,不会随波逐流。

●芯动科技 —— 通用标准和PPA定制优化双重IP方案

芯动科技(Innosilicon)是中国一站式IP和芯片定制服务及GPU领军企业,提供全球各大工艺厂从55纳米到5纳米FinFET全套高性能IP核和ASIC定制解决方案。

据了解,该公司所有IP和芯片全自主可控,经过数十亿颗量产打磨,连续十年中国市场份额遥遥领先,正在推出国内首个数据中心高性能服务器GPU——“风华”。

在高性能计算/多媒体&汽车电子/IoT物联网等领域,芯动解决方案具有国际先进水平,涵盖DDR5/4、LPDDR5/4、GDDR6X/6、HBM2e/3、Chiplet、56G/32G SerDes(含PCIe5/4/USB3.2/SATA/RapidIO/GMII等)、HDMI2.1、ADC/DAC、智能图像处理器GPU和多媒体处理内核等多种技术。芯动科技的ASIC定制,跨工艺跨封装,涉及从需求到产品, 能端到端为客户加速从规格、设计到流片量产,及封装成型全流程。

根据该公司介绍,芯动科技IP能够满足国际通用标准,还可根据客户应用场景进行PPA优化,一步到位交钥匙快速集成,全程为客户产品成功保驾护航,实现芯片差异化竞争优势。特别是其Memory接口和Chiplet接口上的优势和布局尤为突出。

●锐成芯微 —— 从超低功耗到IP研发

锐成芯微(Actt)成立于2011年,致力于集成电路知识产权(IP)产品设计、授权,并提供一站式服务。其官方介绍中显示,该公司专注于集成电路知识产权(IP)研发、授权业务及一站式设计服务,从超低功耗技术这一个“点”起步,逐步构建成超低功耗模拟IP和高可靠性非易失性存储器IP的两点一“线”,并进而形成模拟IP、存储器IP、接口IP和射频IP的产品格局。

IP包括超低功耗模拟IP、高可靠性存储IP、高性能射频IP及高速接口IP为主的产品格局。公司先后与20多家晶圆厂建立了合作伙伴关系,国内外申请专利超200件,累计开发IP 500多项,服务全球数百家集成电路设计企业,产品广泛应用于5G、物联网、智能家居、汽车电子、智慧电源、可穿戴、医疗电子、工业控制等领域。

国产接口IP挑战和机遇并存通过以上盘点不难发现,国内接口相关IP设计企业数量正在高速增长,本土IP种类覆盖逐渐齐全。在新开IC项目数量高速增长之下,众多应用对接口IP有着极大需求,勇于“吃螃蟹”的本土设计公司逐渐增多,但国产在接口IP上仍要面临国际大厂垄断格局以及本土企业同质化竞争逐渐浮现的挑战。

一位接口IP专家曾表示,国内在接口IP正在面临的问题就是人才缺乏和设计经验不足。设计接口的IP,这是一个多学科的综合考量点,而且需要有很强的经营积累的过程。除此之外,在高速接口上,相关EDA工具上也较为贫乏。

结合上文的企业可以看出,相关经验人士正在带队进入接口IP领域,并围绕EDA作为关键进行接口IP的研发设计。其中最为典型的就是芯耀辉这家公司,CEO余成斌不仅拥有30余年的IP研发经验,整体的战略也着手在EDA和平台生态建设上。

“IP企业要找准定位发挥自身优势,发展技术和服务的独特性,更为重要的是能否建立起一种生态的能力,建立的上下游生态体系。这是企业层面的错位发展和布局差异化。”,一位接口IP专家这样建议国产IP。

国产接口IP从扩展摩尔和超越摩尔上发展那么国产接口IP的机会在哪里?余成斌此前曾在一次对话中向记者表示,后摩尔时代IP将沿着延续摩尔、扩展摩尔和超越摩尔的三个方向发展。

Chiplet将是扩展摩尔IP的发展主要技术,这背后实际是先进封装技术+接口IP技术。可以看到,SoC的成本是最高的,Chiplet将取得在性能、die功耗和成本的平衡。Chiplet需要接口IP也称为高速D2D连接,串行模式如56G/112G SerDes,并行的连接如HBI和HBM。D2D设计更需要更优化的SIPI设计和验证,多晶片SIP ESD保护,PVT检测和自动调准等验证量产解决方案。

据Omdia数据显示,2018年全球Chiplet市场规模为6.45亿美元,预计2024年市场规模可达58亿美元,年均复合增长率可达44%,并且有望逐渐扩展到整个半导体市场。Chiplet正在为IP行业带来更多想象力。

来源:芯耀辉

新一代EDA+IP+AI协同自动设计的新时代将是IP发展超越摩尔打破常规的方向。余成斌分析,未来IP必须涵盖更加复杂的功能子系统、拥有更高的适配性、智能化自动化以及高抽象层次和高精度的系统级模型和自适应界面,从而打破常规从顶层系统抽象到底层物理实现方法论的革新,来满足未来复杂系统的智能化应用、高度异构集成芯片高速实现的需求;打破系统芯片的设计和验证工作量巨大,复杂性高及周期耗时不断增长的瓶颈。

除此之外,一款IP产品被认可,不仅需要设计上的优势,还需要不断积累的口碑, “硅验证”就是让接口IP被认可的最直接的方式。

根据摩尔定律,高性能芯片设计难度不断加大,且IP极高的技术壁垒导致独立完成所有芯片IP设计需要大量资源和成本。对比之下使用经过验证的IP可以有效降低设计风险和成本。而这种沉淀需要长期积累、持续投入,考验着企业的商业策略和能力。

来源:芯耀辉

“在后摩尔时代,IP将结合先进工艺、先进封装、智能协同自动设计作为撬动整个芯片产业需求的支点”,余成斌这样介绍道。

图片新闻

最新活动更多

-

即日-3.21立即报名 >> 【深圳 IEAE】2025 消费新场景创新与实践论坛

-

即日-3.25立即报名 >>> 【在线会议】医疗设备的无线共存、高速数字与射频测试

-

3月27日立即报名>> 【工程师系列】汽车电子技术在线大会

-

即日-3.31立即报名>>> 【在线会议】AI加速卡中村田元器件产品的技术创新探讨

-

4月1日立即下载>> 【村田汽车】汽车E/E架构革新中,新智能座舱挑战的解决方案

-

4日10日立即报名>> OFweek 2025(第十四届)中国机器人产业大会

推荐专题

分享

分享

发表评论

请输入评论内容...

请输入评论/评论长度6~500个字

暂无评论

暂无评论