4日10日 OFweek 2025(第十四届)中国机器人产业大会

立即报名 >>>

7.30-8.1 全数会2025(第六届)机器人及智能工厂展

火热报名中>>

芯片制造商引爆3D IC热潮 EDA产业亟需本土创新

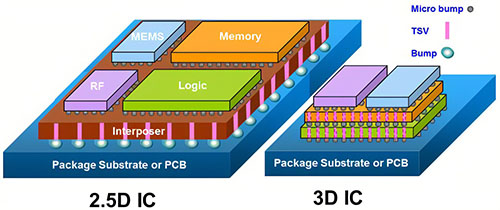

随着摩尔定律的放缓,2D和3D封装技术被认为是下一个半导体产业成长所需的关键技术,各半导体厂商都在致力于研究。在PC领域,AMD早期采用被称为“chiplet”的2D封装技术,以应付对手英特尔的竞争力,其重要性毋庸置疑。

6月27日台湾媒体报道称,台积电(TSMC)将3D IC研发中心设在日本,以此来拉开与三星代工、英特尔等在先进工艺节点上的差距。

随着摩尔定律放缓,3D IC设计备受关注

TSMC是世界上最大的代工生产半导体制造商,接受AMD、Apple、NVIDIA、Qualcomm等无晶圆厂(Fabless)半导体制造商的芯片代工生产。AMD的Ryzen、苹果的A/M系列、NVIDIA的H100等先进芯片均由TSMC制造。

在此之前,台积电的研发和生产总部都在中国台湾,但近年来该公司一直在加快将此类设施转移到海外。譬如,在建的美国亚利桑那州的新晶圆厂,计划2024年开始生产。日本去年也宣布,TSMC设立新工厂的消息,计划生产时间也是于2024年开始。

此次TSMC在日本设立的3D IC研究中心旨在为半导体制造的后端封装工序服务。

这几年,摩尔定律已经持续放缓,很难像以前那样在两年内将晶体管数量翻一番。因此,提高性能的唯一方法是增加芯片的裸片尺寸,但结果会导致制造成本的上升。

在这种情况下,使用2D、3D封装技术有望解决该问题,如,AMD在使用“chiplet”的2D封装技术。三星电子推出的3D封装“X-Cube 技术”。台积电正在研发的“CoWoS”2D封装技术,以及正在使用的“InFO”,且未来计划推出3D封装“SoIC技术”。

3D IC热潮下,芯片的设计仿真是个难点

由于未来摩尔定律不太可能重回常规步伐,因此半导体制造商面临着巨大的压力,这些制造商不仅要保证信号完整性和追求低功耗的同时,还要求以更小的封装尺寸加快创新芯片设计的上市速度。虽然3D IC有望满足所有这些需求,但与此同时,它们也带来了新的设计复杂性,对传统EDA工具和工艺提出了挑战。

3D IC通过堆叠裸片并使之互联以使其作为单个器件运行来制造,这样做带来的新风险是由更高密度引起的热积聚。因为它们比典型的片上系统(SoC)大得多,具有更长的互连,所以需要对它们进行严格的测试,以发现有故障的集成点以及系统级故障。

然而,大多数半导体研发团队根本不具备管理3D IC分析和设计验证这一艰巨工作的能力。传统的SoC仿真方法让他们不堪重负,这种方法依赖于一系列循序渐进的过程,其中单一物理仿真工具被逐一应用。当工程师将这些不同的工具和这一系列过程应用于复杂的3D IC设计时,他们会遗漏系统级交互、连接点、综合热效应和其他考虑因素,从而导致严重错误。

随着3D IC在高级半导体应用中变得越来越普遍,工程团队需要一种同样创新的新分析方法。他们需要一个单一、开放和成熟的平台,在整个产品设计中进行并行、多元的模拟和分析。他们需要在组件和系统层面上快速、同时考虑多种物理因素。

EDA市场迫切需要国内企业的本土创新

而掌握这些新方法和前沿设计、仿真EDA工具的企业几乎被国际巨头Synopsys,Cadence,SIEMENS EDA,Ansys等寡头占据,与之相比的是,国内EDA企业起步较晚,要落后于竞争对手。目前而言存在国内EDA市场由国外公司主导。

作为IC和PCB背后的关键技术,设计和制造计算机芯片不可或缺,国内半导体设计企业必然离不开EDA工具,EDA市场也迫切需要一些国内企业的自主创新。近几年,随着持续的中美贸易紧张局面,国内自主创新热潮不减,对EDA领域的投资也在迅速增加。

根据MarketWatch数据显示,预计2020年至2025年间,中国EDA工具市场将实现10.2%的复合年增长率,到2027年,全球EDA市场预计将达到208.9亿美元。

国内EDA领域最大的公司之一是芯华章X-Epic。该公司由前新思科技副总经理王礼宾于2020年3月创立,据报道,该公司在由云晖资本领投的Pre-A轮融资中筹集了至少1亿元,此后又经历了多次融资。

此外,其它大型EDA公司包括上海合见工业软件集团有限公司和合肥的全芯智造技术有限公司。两家公司也属于初创企业。合见工业软件成立于2020年5月,全芯智造成立于2020年9月,均由Synopsys的前资深人士创立,Synopsys本身也投资于全芯智造。

与国外寡头相比,国内创新企业别无选择,只能在风险投资家的腰包和支持下迅速整合资源并开发本土工具。由政府主导的集成电路大基金已经参与了EDA初创企业的多轮融资。

高性能FPGA原型验证系统桦捷(HuaPro-P1)使用演示。来源/芯华章

这种对国内 EDA的承诺肯定会得到回报。2020年11月,芯华章X-Epic展示了首批成功的本土EDA解决方案之一,称为“EpicElf”,一种FPGA验证工具。2021年11月24日,芯华章发布了4款极具技术门槛的验证EDA产品,以及统一底层构架的智V验证平台,包括了数字仿真穹鼎GalaxSim、形式验证穹瀚GalaxFV、智能验证穹景GalaxPSS以及原型验证桦捷HuaPro-P1。

总结一点:3D IC设计是摩尔定律放缓之后的下一个风口,如何解决其芯片设计、仿真及系统验证等问题应是当务之急。

图片新闻

最新活动更多

-

即日-3.21立即报名 >> 【深圳 IEAE】2025 消费新场景创新与实践论坛

-

即日-3.25立即报名 >>> 【在线会议】医疗设备的无线共存、高速数字与射频测试

-

3月27日立即报名>> 【工程师系列】汽车电子技术在线大会

-

即日-3.31立即报名>>> 【在线会议】AI加速卡中村田元器件产品的技术创新探讨

-

4月1日立即下载>> 【村田汽车】汽车E/E架构革新中,新智能座舱挑战的解决方案

-

4日10日立即报名>> OFweek 2025(第十四届)中国机器人产业大会

推荐专题

分享

分享

发表评论

请输入评论内容...

请输入评论/评论长度6~500个字

暂无评论

暂无评论