7.30-8.1 全数会2025(第六届)机器人及智能工厂展

火热报名中>>

佳能猪突猛进,纳米压印取得重要进展

日本佳能公司10月13日宣布推出FPA-1200NZ2C纳米压印半导体制造设备,该设备执行电路图案转移。

佳能据介绍,佳能的纳米压印光刻(Nano-Imprint Lithography,NIL)技术可实现最小线宽14nm的图案化,相当于生产目前最先进的逻辑半导体所需的5nm节点。此外,随着掩模技术的进一步改进,NIL有望实现最小线宽为10nm的电路图案,相当于2nm节点。NanoimprintLithography(NIL),是一种新型的微纳加工技术。该技术将设计并制作在模板上的微小图形,通过压印等技术转移到涂有高分子材料的硅基板上。纳米压印的分辨率由所用印模板图形的大小决定,物理上没有光刻中的衍射限制,纳米压印技术可以实现纳米级线宽的图形。

5nm芯片是目前 IC 制程的领先水平,采用极紫外光刻(EUV)技术。5nm芯片在晶体管、导线间距等方面有非常高的要求,为了实现更小的尺寸和更加密集的设备,就需要采用更先进的制程技术。

3nm的也就台积电有苹果的芯片推出。5nm已经是很厉害的水平了,中芯至今还没达到。

纳米压印概念非常高深,但实际上它的原理并不难理解。压印是古老的图形转移技术,活字印刷术便是最初的压印技术原型,而纳米压印则是图形特征尺寸只有几纳米到几百纳米的一种压印技术。

打个比方来说,纳米压印光刻造芯片就像盖章一样,把栅极长度只有几纳米的电路刻在印章上,再将印章盖在橡皮泥上,得到与印章相反的图案,经过脱模就能够得到一颗芯片。在行业中,这个章被称为模板,而橡皮泥则被称为纳米压印胶。

日本铠侠从2017年就开始与佳能等企业合作开发NIL压印技术。目前,铠侠已经将NIL技术应用到了15nm NAND闪存器上,并有望在2025年推出采用NIL技术的5nm芯片。铠侠表示,NIL设备相比EUV可以降低90%的能耗,同时转化率更好,而且NIL设备的成本更低,研发成本比EUV降低了60%。

几种常用光刻技术对比:

如果能在5nm上稳定压印光刻技术,批量生产的话,佳能估计又能起飞一段时间了。

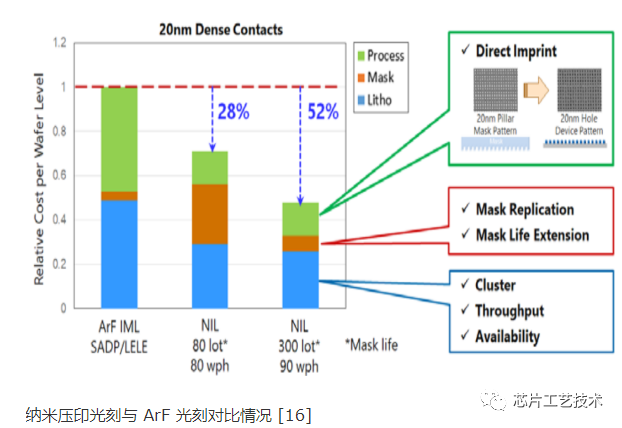

佳能的研究显示,其设备在每小时 80 片晶圆的吞吐量和 80 片晶圆的掩模寿命下,纳米压印光刻相对 ArF 光刻工艺可降低 28% 的成本,随着吞吐量增加至每小时 90 片,掩模寿命超过 300 批次,成本可降低 52%。此外,通过改用大场掩模来减少每片晶圆的拍摄次数,还可进一步降低成本。

对纳米压印来说,模板是器件成功的关键。不同于传统光学光刻使用的 4X 掩模,纳米压印光刻使用 1X 模版,会导致模具制作、检查和修复技术面临更大挑战。

SK海力士2023年引入佳能的纳米压印设备,正在测试和研发,用于2025年推出3D NAND的量产,届时晶圆成本能下降不少。

原文标题 : 佳能猪突猛进,纳米压印取得重要进展

图片新闻

技术文库

最新活动更多

-

3月27日立即报名>> 【工程师系列】汽车电子技术在线大会

-

4月25日立即报名>> 【线下论坛】新唐科技2025新品发布会

-

在线会议观看回放>>> AI加速卡中村田的技术创新与趋势探讨

-

4月30日立即参与 >> 【白皮书】研华机器视觉项目召集令

-

即日-5.15立即报名>>> 【在线会议】安森美Hyperlux™ ID系列引领iToF技术革新

-

5月15日立即下载>> 【白皮书】精确和高效地表征3000V/20A功率器件应用指南

推荐专题

分享

分享

发表评论

请输入评论内容...

请输入评论/评论长度6~500个字

暂无评论

暂无评论