7.30-8.1 全数会2025(第六届)机器人及智能工厂展

火热报名中>>

低压差分信号LVDS

图12

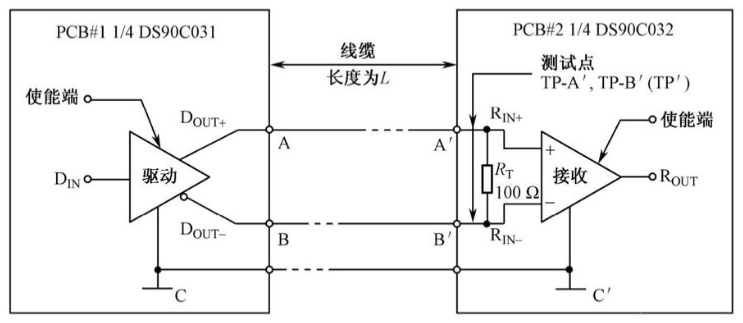

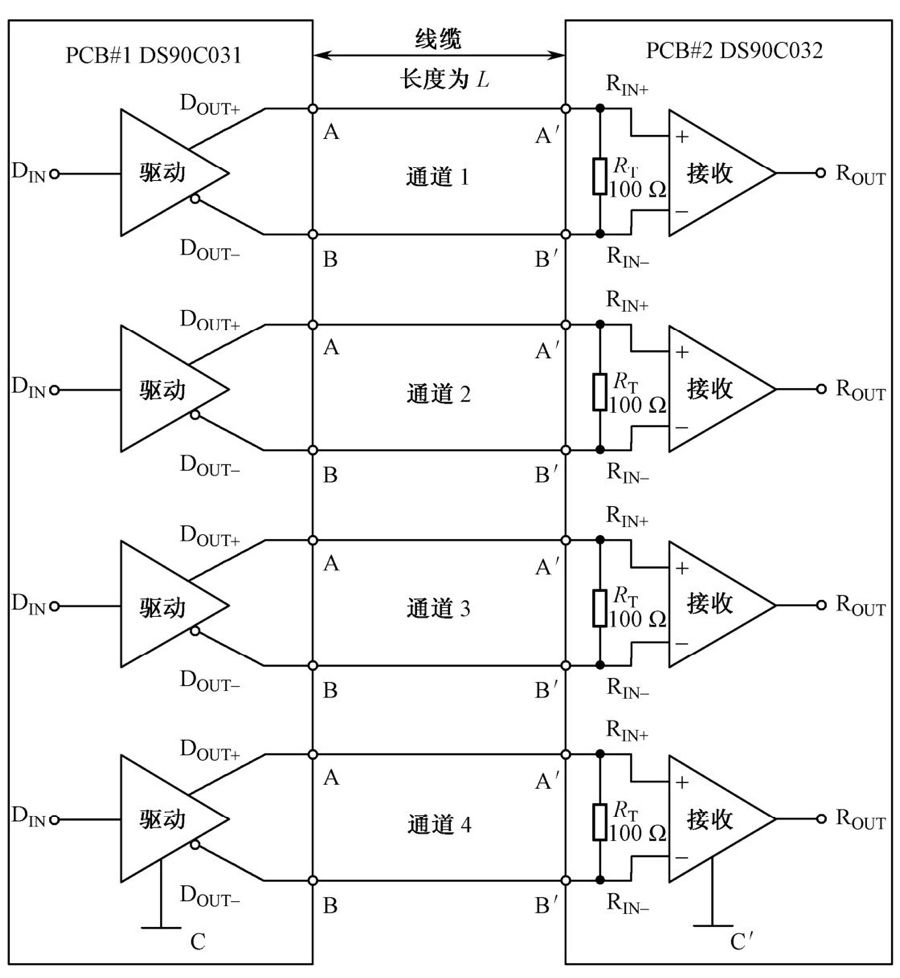

b.眼图测试电路LVDS驱动器及接收器通常用于简单的点对点的配置,如图13所示。以下内容介绍了接收眼图测试电路。

图13

PCB#1表示的是一个LVDS驱动器DS90C031焊接到阻抗相匹配的连接器(位于边缘PCB)。连接器是一个AMPLIMITE 0.050系列连接器。用于这一测试的线缆是编号为271211Berk-Tek线缆,这是CAT3 105(差模)28 AWG的双绞线(25对全屏蔽),这种线缆是一个共同的数据接口线缆。对于这种试验的报告,下面对线缆长度进行了测试:1m、2m、3m、5m和10m,线缆长度超过10m就不进行试验,但可应用在较低的数据传输速率上。Berk-Tek不再制造这种线缆,其他厂商制造了类似的线缆,如日立电线曼彻斯特(部件编号#49251)。PCB#2 1/4 DS90C032 LVDS是接收端阻抗匹配(位于边缘PCB)的连接器。该连接器是一个AMPLIMITE 0.050系列连接器。一个功率为100 W的表面贴装电阻器是用来终止线缆接收输入引脚的。c.测试过程伪随机位序列(PRBS)的产生器连接到驱动器的输入端,眼图(测量在TP'端)在示波器上观察。在不同的线缆长度(L)下进行测试,使频率的输入信号不断增加,直到测量抖动相当于20%对单位区间的特定线缆长度。使用NRZ编码方案,在差分电压点上抖动测试两次。首次测量了0V差分电压(最佳接收阈值点)的最低抖动,和最高接收阈值点(±100mV)获得最坏的情况下的最高抖动。d.使用差分探头无论是LVDS、ECL,还是CML,使用差分探头都有同样的效果,都适用于示波器和其他形式的测试设备。差分探测比单端探测更精确,且有更好的噪声抑制效果。许多数据表和LVDS的准确规格为(Do+)-(Do-),这是用不同的振幅来衡量差分探头。输出这种探头通常为2× [(Do+)-(Do-)]。2)结果和数据点不同数据率的抖动及与线长的关系如表3所示。

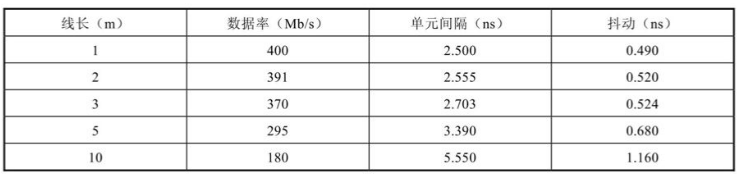

表3 20%抖动表和0V差分(最小抖动)

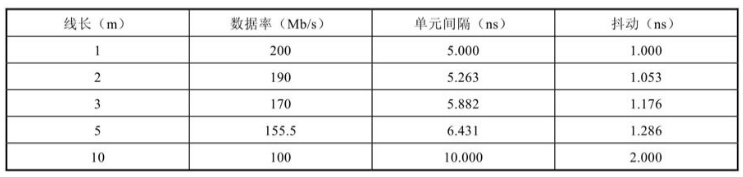

0V差分点抖动测量:对于1m的线缆,在400Mb/s时测量到0.490 ps的抖动;对于10m线缆,在180Mb/s时测量到1.160ns的抖动。±100mV的电平下抖动测量:对于1m的线缆,在200Mb/s时有1ns的抖动;对于10m线缆,在100Mb/s时有2ns的抖动,如表4所示,数据抖动与线长及数据率的关系如图14所示。表4 20%抖动表和±100mV(最大抖动)

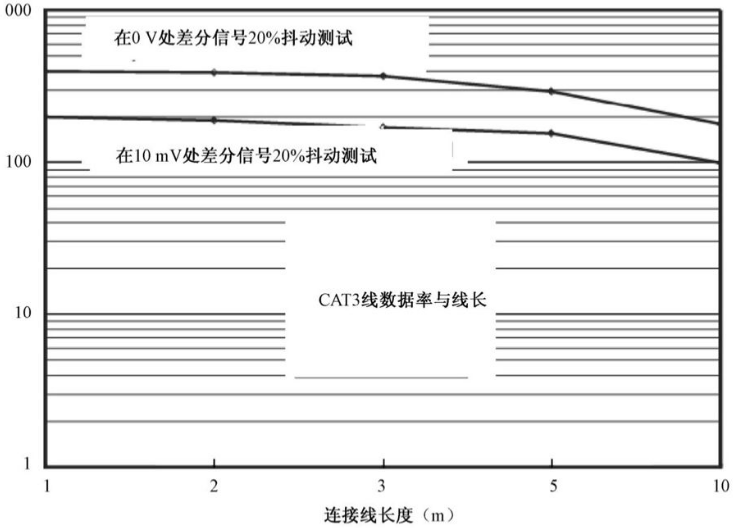

图14

图14

在LVDS线缆较长的情况下,当直接耦合的LVDS提供高达±1V的共模抑制时,长线缆的应用可能需要更大的共模的支持。图14显示了数据速率和线缆长度应用程序测试之间的关系。通常,数据传输率在200~400Mb/s,有可能传输更短的距离,而传输率为100~200Mb/s之间,传输距离有可能为10m。请注意,使用不同的编码方案、线缆或线规(特设工作组)将创建一个不同的关系,即最大数据传输率与线缆长度的关系。

2 、误码率测试

1) 什么是误码率测试误码率测试是一种用来衡量性能的通信系统的方法。标准方程的误码率测量为误码率=(传输错误的位数)/(总的传输位数)图15所示的测试提供了一系列误码率测试的DS90C031/032的LVDS线路驱动器/接收装置的结果。4个驱动器被用于驱动1~5m的标准双绞线线缆速率在选定的数据下的传输,4个接收器被用来恢复数据的负载在线缆的末端。

图15

PCB #1 DS90C031的LVDS驱动器焊接到与PCB相匹配的、设备之间的(位于边缘PCB)连接器。

连接器是AMPLIMITE 0.050系列连接器。图15中的测试用的是编号为271211Berk-Tek的套件,这是一个CAT3 105(差模)28 AWG的双绞线(25对),常用在SCSI中。这种线缆是一个共同的数据接口线缆,用于对1m和5m长的线缆进行测试。Berk-Tek不再制造这种线缆,类似的线缆,可以通过其他厂商进行生产,如日立电线曼彻斯特(部件编号为49251)。PCB#2 DS90C032 LVDS接收器焊接到布线阻抗匹配的电路上,连接器是一个AMPLIMITE 0.050系列连接器。100 W功率的表面贴装电阻器是用来在接收输入引脚上终止线缆的。

2)测试流程并行高速误码率发送器/接收设置(泰克MultiBERT-100)可用来进行测试,发射器被连接到驱动器的输入端,而接收器则连接到BERT可接收器的输入端,对不同线缆的长度和数据传输率进行了测试。测试器提供PRBS 152 -1长序列位。在第一次测试中,四个通道输入同样的测试信号。至于在其他的测试中,PRBS 顺次间隔 4位取值得到一序列,送到输入通道,这样通道间也提供了一种随机序列。使用的编码方案是NRZ码。在室温下,电源电压为+5.0V时,经系统测试配置,在一定时间内连续测试。在完成时,分组并记录结果,其中包括测试时间、传输比特数和错误比特记录。

3)测试和结果通过测试表明LVDS技术误码率极低。5m的双绞线在100Mb/s运行时,测得误码率1×10-12。

图片新闻

技术文库

最新活动更多

-

3月27日立即报名>> 【工程师系列】汽车电子技术在线大会

-

4月1日立即下载>> 【村田汽车】汽车E/E架构革新中,新智能座舱挑战的解决方案

-

即日-4.22立即报名>> 【在线会议】汽车腐蚀及防护的多物理场仿真

-

4月23日立即报名>> 【在线会议】研华嵌入式核心优势,以Edge AI驱动机器视觉升级

-

4月25日立即报名>> 【线下论坛】新唐科技2025新品发布会

-

4月30日立即参与 >> 【白皮书】研华机器视觉项目召集令

推荐专题

-

10 第四代半导体,破晓时刻

分享

分享

发表评论

请输入评论内容...

请输入评论/评论长度6~500个字

暂无评论

暂无评论