4日10日 OFweek 2025(第十四届)中国机器人产业大会

立即报名 >>>

7.30-8.1 全数会2025(第六届)机器人及智能工厂展

火热报名中>>

不就是包地打孔嘛,能有多讲究?

问:为什么要包地?

答:为了控阻抗和降低串扰;

问:那包地需不需要打过孔呢?

答:要啊,必须要啊,不然包地就没意义了。

问:那包地打孔设计一般需要注意什么地方呢?

答:……

是的,坊间传说的包地神技能其实并没有那么直观。什么叫直观,就好像1+1=2。(好了,别逗了)。那就好比10%的阻抗变化会带来大约5%的反射,比如100mil的过孔stub的谐振点大概会在15GHz之类的。包地打孔你很难从一开始就能够预测到你的设计质量会怎么样,而且一样的设计放在不同的板子也会千差万别。而且最重要的是并不是包了地就一定会带来信号质量的改善,很多情况下你辛辛苦苦包完了,结果只换来这几个字。

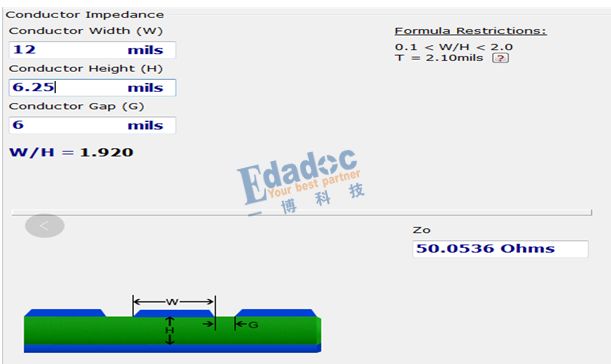

好了,说了那么多吓人的话,我都不好意思再说了,只能举一个吓人的例子吧。我们如果要使用例如网络分析仪去测试PCB上面的DUT(待测物),最通常的做法就是通过SMA头接入PCB,我们要举的这个例子就是一个测试板,由于只有表层走线,4层板就足够了,这样的话表层到第二层参考层的厚度一般就比较厚,直接导致的后果就是表层的走线要很宽才能控到50欧姆的阻抗,另外也可以采用下面这种共面波导的包地形式来达到目的,这样的话线宽就可以不用太过粗。我们通过阻抗计算软件计算,得到线宽走12mil,同层的包地距离6mil。

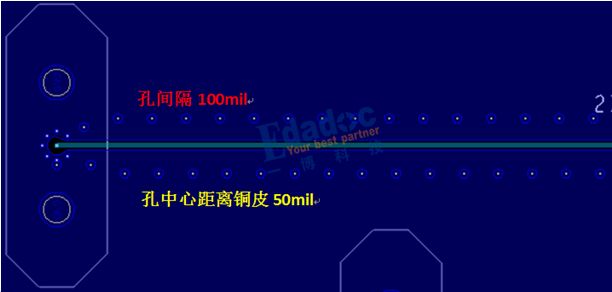

前面说了嘛,这也算一种包地的情况,那我们的工程师就自然的把地过孔打上,就像下图所示一样。

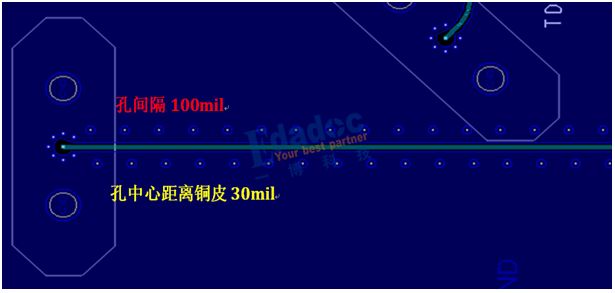

做过设计的朋友都知道,现在使用软件来进行包地打孔的设计那叫一个方便啊,输入过孔的间隔和距离后,唰一声就做出来了。

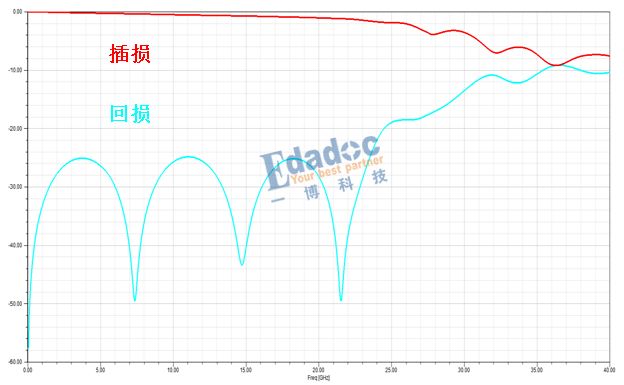

上面的设计看起来也好像没什么问题,包了地,打了孔。由于我们这个是一块测试板,需要达到的测试频段达到30GHz,因此上图的这根校准线的设计是至关重要的,必须要有很好的回损和插损的性能。当我们拿这根设计进行仿真后会发现,结果可能并没有想象中那么美好,如下所示:

在大概25GHz之后回损就变得不线性了,一直往恶劣的方向走去,同时插损也受到了影响,因此根据我们还算丰富的测试经验来看,这根校准线的设计应该是很难满足30GHz的测试要求的。

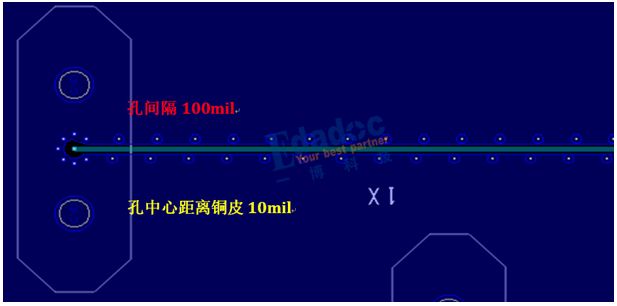

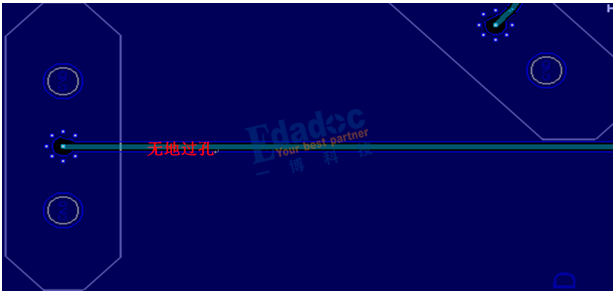

地也包了,孔也打了,那为什么会出现高频振动和跌落的原因呢?这时候我们SI的优势就体现出来了,我们可以去做不同包地情况的分析,例如我们补充下面这三种情况:分别是包地过孔距离铜皮10mil,30mil和干脆不打过孔了。

我们把4种情况的仿真结果放在一起来看,会发现一些意想不到的东西。

图片新闻

技术文库

最新活动更多

-

3月27日立即报名>> 【工程师系列】汽车电子技术在线大会

-

4月1日立即下载>> 【村田汽车】汽车E/E架构革新中,新智能座舱挑战的解决方案

-

4日10日立即报名>> OFweek 2025(第十四届)中国机器人产业大会

-

即日-4.22立即报名>> 【在线会议】汽车腐蚀及防护的多物理场仿真

-

4月23日立即报名>> 【在线会议】研华嵌入式核心优势,以Edge AI驱动机器视觉升级

-

4月25日立即报名>> 【线下论坛】新唐科技2025新品发布会

推荐专题

分享

分享

发表评论

请输入评论内容...

请输入评论/评论长度6~500个字

暂无评论

暂无评论