一文读懂,绕线的影响有哪些?

粉丝:“请问高速先生,绕线的设计要注意哪些地方”,高速先生:“至少要保证绕线的间距达到3H”,然后再补上一句,“H是信号到参考层的距离哈”。这时候粉丝一般都会“哦……谢谢哈”,我们随即以一个尴尬而不失礼貌的微笑进行回应……

其实我们也知道,一个简单的回答会让粉丝们变得越发的不淡定,虽然这个答案本身是比较准确的,仅仅是这个回答会有一点口说无凭的感觉。

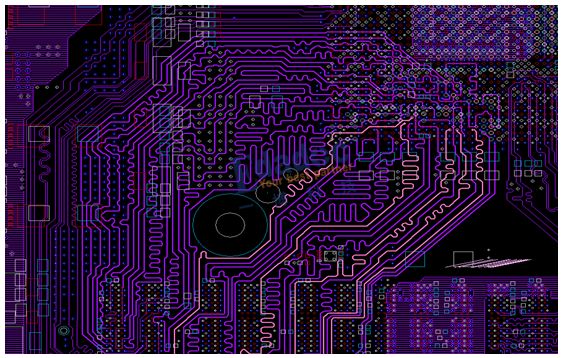

什么?你们还不知道我们到底在说什么东西?其实绕线的设计基本上存在于每一块PCB板的并行信号上。最常见的就是我们的DDR设计,一组需要等长的信号由于收发pin的位置不一样,必然会存在绕线的情况。然后从空间的角度来衡量的话,绕线的间隔越小那么所占的空间就越小,尤其是在DDR颗粒间的绕线更是如此,在里面寸土寸金的地方,作为一个工程师肯定希望更小间距的绕线咯。

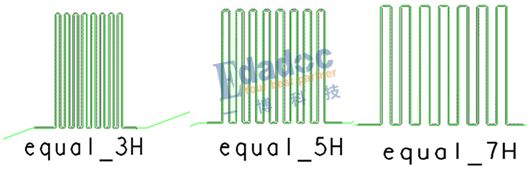

好吧好吧,解释完我们到底在说什么之后,我们还是继续说回口说无凭这个事哈。粉丝们希望得到一些数据的支撑,为此我们也专门做了一板测试板去验证它。很简单,没有对比就没有伤害,我们做的测试板要对比的设计如下所示,分别做了绕线间距为3H,5H和7H三种设计,当然还有不绕线的一根参考线啦,总长度为10inch。

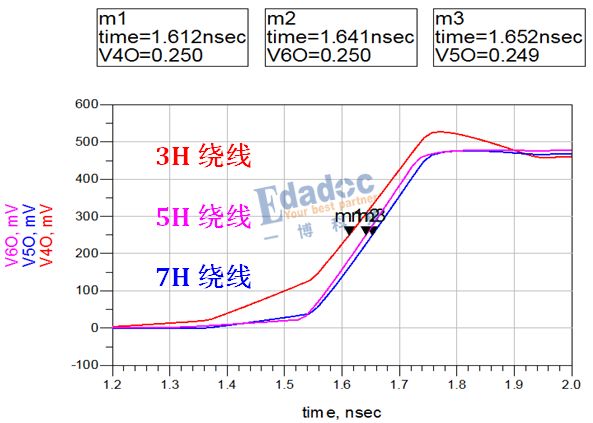

那么测试的数据是怎么样的呢?首先说到绕线嘛,大家肯定会关心绕线完的时延啦,结果这三种情况的测试结果的对比是这样的。可以看到,绕线绕得越密的话,信号的延时会变小,3H大概会比5H的绕线快30ps,而5H之后就影响比较小了,5H只比7H快10ps左右了。

我们老是说3H是一个基本原则,我们可以和不绕线的延时来比一下,结果如下所示。

它们的延时差了大概50ps。考虑到这个是10inch的绕线情况,那么简单粗暴的换算成单元长度时,其实每英寸的差别只有5ps左右,已经是非常小的影响了。

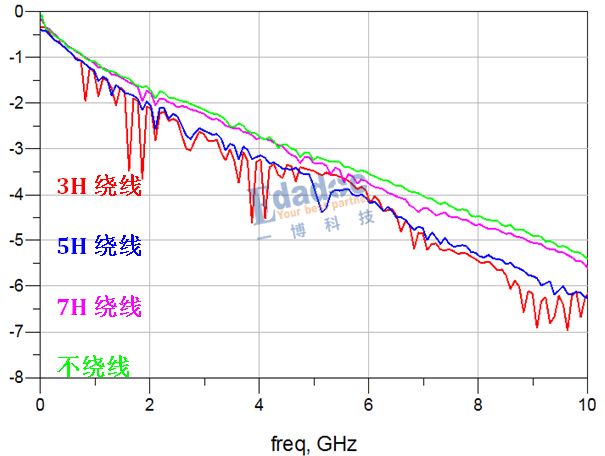

当然如果从损耗这个角度来看的话,又会看到一些和信号频率很相关的影响了。可以看到3H在2GHz以上就会有很明显的谐振点,要是信号速率在4Gbps(2GHz基频)时就会严重影响信号质量,5H,7H就会明显有很好的改善。

虽然从损耗来看3H比较恐怖,但是……我们都忽略了一点,哪怕你真的需要走10inch的绕线,你也不会把一个跑几个Gbps的走线用单端线来走吧。这里顺便说一下哈,同样的绕线,用差分的形式会有非常非常明显的改善哈,大家不要太担心。我们单线的绕线设计目前主要就是应用于DDR这样的并行系统,目前最高的速率也只不过在1.5GHz(3Gbps)左右哈。

— end —

本期提问

说说你们目前对绕线的设计是怎么去处理的?或者对于绕线还有什么见解也可以谈谈哈。

文 | 黄刚

图片新闻

最新活动更多

-

4月16日预约观看>> 开发前服,优化项目投资价值 筑牢落地关键防线

-

4月22日立即报名>> 【在线会议】ADI六款仪器仪表方案助力产品快速上市

-

4月23日立即报名>> 【直播】 智测未来·2026海克斯康春季产品创新日

-

5月13日立即预约>>> 【线下会议】恩智浦创新技术峰会·深圳

-

5月14日立即下载>> 【白皮书】村田室内外定位解决方案

-

即日-5.20立即下载>> 【限时免费】物理场仿真助力生物医学领域技术创新

分享

分享

发表评论

登录

手机

验证码

手机/邮箱/用户名

密码

立即登录即可访问所有OFweek服务

还不是会员?免费注册

忘记密码其他方式

请输入评论内容...

请输入评论/评论长度6~500个字

暂无评论

暂无评论