后FinFET时代的技术演进

Forksheet:性能和面积的改进

IMEC的研究人员最近使用TCAD仿真来量化Forksheet架构的预期PPA潜力。所研究的器件针对IMEC的2nm技术节点,采用42nm的接触栅节距和16nm的金属间距的5T标准单元库。拟议的设计包括一些微缩助推器,例如埋入式电源轨和环绕接触。

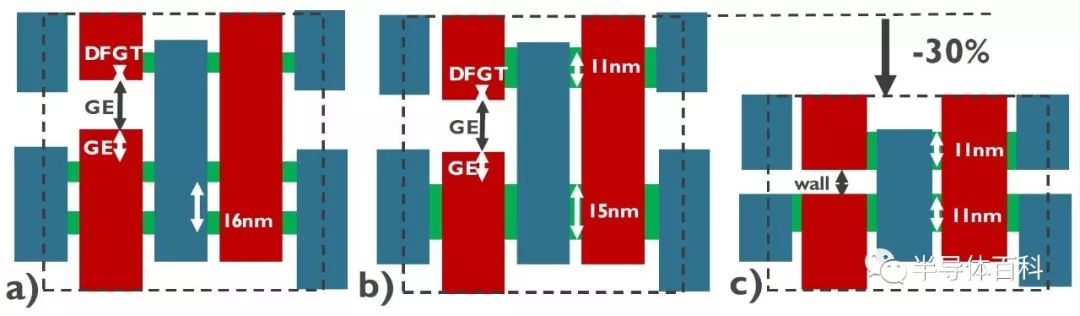

与Nanosheet器件相比,已计算出10%的速度增益(恒定功率)和24%的功率减小(恒定速度)。这种性能提升的部分原因是由于栅极-漏极重叠较小而导致的(寄生)Miller电容减小。可用空间还可以用于增加sheet宽度,从而提高驱动电流。最后,可以利用从n到p的间距减小将轨道高度从5T缩小到4.3T,从而使单元面积减小20%。在SRAM设计中,仿真结果表明,在8nm 的pn间距下,单元面积的微缩比例和性能提高了30%。

SRAM半单元的版图,用于a)FinFET,b)GAA Nanosheet和c)Forksheet。由于pn间距不受栅极扩展(GE),栅极切割(GC)或dummy fin gate tuck(DFGT)的影响,因此Forksheet可以提供高达30%的位单元高度微缩比例。

在从平面到FinFET以及垂直堆叠的Nanosheet的自然进化中,可以将Forksheet视为下一版本。以上特性证明了其作为2nm技术节点的最终逻辑“通用” CMOS器件的潜力。在进一步的研究中,需要解决将这些器件完全投入生产的工艺挑战。

CFET:通往3T逻辑标准单元的道路

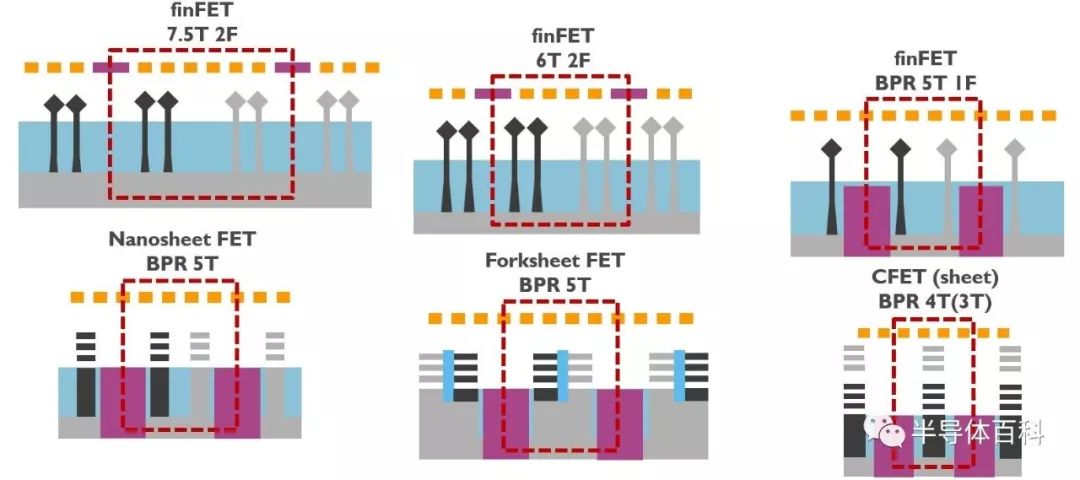

小于5T时,单元高度的进一步降低主要受到可布线性问题的限制,而且这个问题应在逻辑区块级别进行评估。为了优化可布线性,我们将进入CFET时代,进一步推动了摩尔定律的发展。

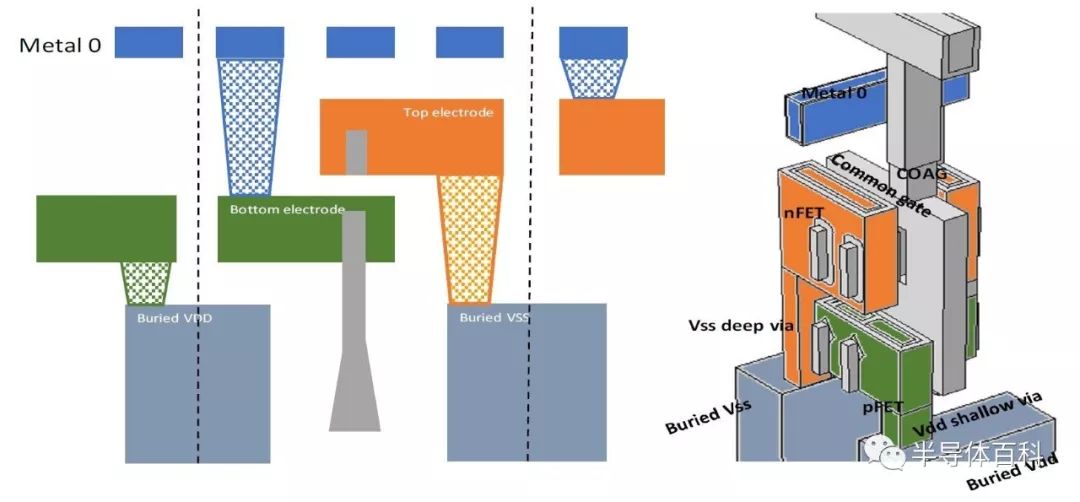

CFET的概念在于将nFET“折叠”在pFET之上,这样就充分利用了器件3D微缩的潜力。

由于具有堆叠特性,CFET拥有2个局部互连层,这为内部单元布线和减小单元面积提供了更大的自由度。单元之间的可布线性也可以大大改善。

CFET架构具有2个局部互连层以及pn 堆叠CMOS基本结构。

初步评估表明,基于FinFET的4T CFET可以对标甚至超过5T“标准” FinFET器件的标准单元功率性能指标。它还可以提供面积缩小25%的标准单元和SRAM单元。基于Nanosheet的CFET可以提供额外的性能提升,并且对于缩小到3T逻辑标准单元来说是必需的。

结论

在本文中,IMEC提出了一条通往2nm及以下技术节点的最终规模化逻辑器件的演进路径。在今天的主流FinFET之后出现了Nanosheet器件,该器件提供了出色的沟道控制功能,同时又增加了有限的工艺复杂性。当配合定标助推器时,具有5T轨道高度的标准单元将触手可及。下一步,Forksheet可能会进场,由于减小了n到p的间距,因此提供了通往4.3T单元的可能性。相关工艺仿真证实了其在2nm技术节点上的潜力。CFET作为最紧凑的CMOS结构,为实现3T逻辑标准单元带来了希望。

从FinFET到Nanosheet,Forksheet再到CFET。

图片新闻

最新活动更多

-

4月16日预约观看>> 开发前服,优化项目投资价值 筑牢落地关键防线

-

4月22日立即报名>> 【在线会议】ADI六款仪器仪表方案助力产品快速上市

-

5月13日立即预约>>> 【线下会议】恩智浦创新技术峰会·深圳

-

5月14日立即下载>> 【白皮书】村田室内外定位解决方案

-

即日-5.20立即下载>> 【限时免费】物理场仿真助力生物医学领域技术创新

-

5月29日立即下载>> 【白皮书】工业视觉AI实战白皮书合集

分享

分享

发表评论

登录

手机

验证码

手机/邮箱/用户名

密码

立即登录即可访问所有OFweek服务

还不是会员?免费注册

忘记密码其他方式

请输入评论内容...

请输入评论/评论长度6~500个字

暂无评论

暂无评论