7.30-8.1 全数会2025(第六届)机器人及智能工厂展

火热报名中>>

一文揭密封装补偿背后的时间黑洞

作者:姜杰

不知各位是否还记得雷豹,没错,就是上次仿真电源差点翻车的那位仁兄《一个好,两个不行,那三个怎么办呢?》,最近,他又饱受PIN Delay的折磨。

所谓PIN Delay,直译“管脚延时”,不过,我们更习惯另外一种叫法“封装长度”。“管脚延时”是指封装级互连产生的延时:对于芯片而言,是指DIE pad到封装引脚之间的延时差异(比如下图中黄色的走线);对于某些高速连接器来说,比如弯公连接器,则是指每一列pin上的延时不一致。在高速电路设计中,需要考虑Pin Delay来减少信号长度的误差。

封装补偿是解决问题的方法,通常芯片或连接器厂家会提供封装级互连长度的参数,PCB设计的等长处理阶段,需要将该参数计入信号长度再绕等长,以达到精确控制信号总长度的目的。

正常而言,考虑了封装长度的走线等长会更好。不过凡事有特例,雷豹最近就遇到了这样的特例。本指望PIN Delay能补回些延时,谁曾想PCB做完封装补偿之后信号时序仿真结果反倒“变差”了,究竟怎么回事?

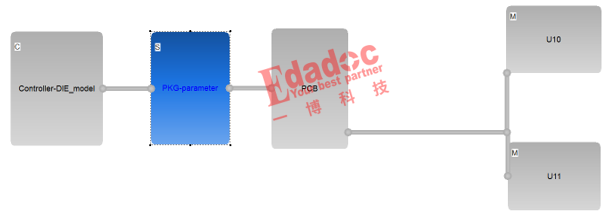

与以往的案例不同,该试验板的主控芯片还在封装设计阶段,换句话说,单板设计与主控芯片的封装设计是同步进行的。因此客户一开始仅提供了DIE pad的模型及部分信号通道的封装参数。吊诡的仿真结果似乎一开始就有迹可循,不过这是后话。

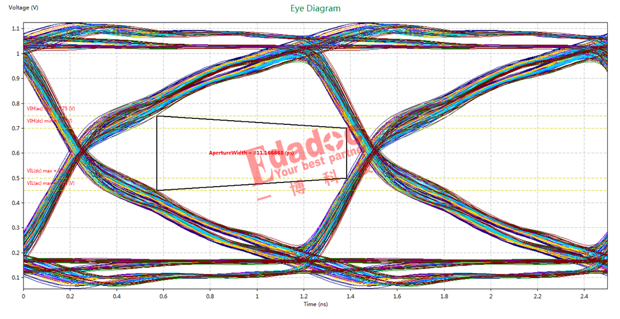

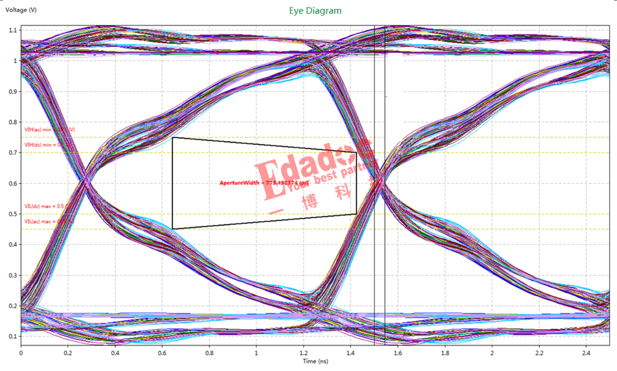

仿真对象是数据速率800Mbps的NAND信号,最短的信号通道(CH6)。由于一开始客户未能提供相应的封装补偿参数,因此最初只能看到PCB在没有设置PIN delay的通道眼图,使用有效眼宽的大小来衡量时序的优劣,是811ps。

随着芯片封装设计的推进,终于等来了PIN delay参数,在Layout攻城狮根据封装补偿调整单板走线等长之后,雷豹迫不及待的再次对同一通道进行仿真,眼图在众人期待的眼神中渐次展开……

封装补偿之前有效眼宽811ps,补偿之后却变成——796ps?!看到这个结果,男人开始沉默,女人开始流泪,一团疑云罩住了所有人:不是说封装补偿后的有效眼宽会变大吗,补偿的时间都去哪啦?!

面对这么刺激的结果,雷豹除了愕然,居然还有些许兴奋:一定要揪出这个时间“黑洞”。首先怀疑的是单板的PIN delay参数设置错误,配合设计工作的Layout老炮儿虽然觉得侮辱性很强,但还是对照客户提供的封装补偿参数检查了约束管理器中的设置,排除了PCB等长设置问题,设计攻城狮的尊严得以维护,问题仍然悬而未决。

既然设计文件没问题,那会不会是仿真模型有异常呢?仔细检查主控芯片的封装参数,果不其然,发现了问题所在!

客户提供的封装模型中居然只有CH7通道的封装参数!

众所周知,等长处理只是手段,我们的目的是等时。而对比PIN delay的具体数据可以发现,不同的通道信号之间延时差别是显而易见的,以DQS信号为参考,根据芯片封装补偿参数,在CH6通道中,DQ3需要减小延时,DQ5需要增加延时,才能达到与DQS的一致,而在CH7通道中则刚好相反,DQ3需要增加延时,DQ5需要减小延时。仿真使用CH7通道的封装参数来补偿CH6通道的走线长度,极端情况下,短的更短,长的更长,难怪结果会南辕北辙,让人抓狂。

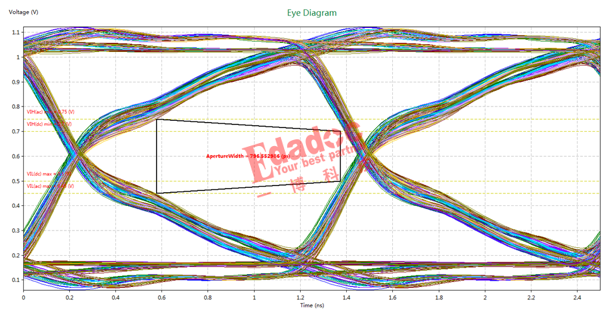

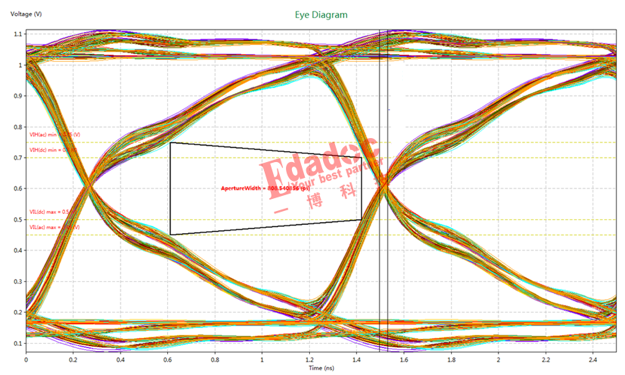

那么,我们再来看看提供了封装模型参数的CH7通道在增加PIN delay前后的差异。没有考虑PIN delay之前,通道的眼图有效眼宽是779ps。

考虑PIN delay之后通道的眼图有效眼宽达到808ps,相比之前增加了29ps,这个值与CH7通道PIN delay最大(78ps)和最小(48ps)的差值28ps也基本吻合。

真相大白,众人释然。雷豹却陷入了沉思:随着接触到的芯片设计越来越多,仿真思路也该与时俱进,“开局一模型,仿真用到底”的时代似乎一去不复返,芯片设计在更新,仿真过程中也应时时检查,步步留心。

图片新闻

技术文库

最新活动更多

-

3月27日立即报名>> 【工程师系列】汽车电子技术在线大会

-

4月1日立即下载>> 【村田汽车】汽车E/E架构革新中,新智能座舱挑战的解决方案

-

即日-4.22立即报名>> 【在线会议】汽车腐蚀及防护的多物理场仿真

-

4月23日立即报名>> 【在线会议】研华嵌入式核心优势,以Edge AI驱动机器视觉升级

-

4月25日立即报名>> 【线下论坛】新唐科技2025新品发布会

-

4月30日立即参与 >> 【白皮书】研华机器视觉项目召集令

推荐专题

分享

分享

发表评论

请输入评论内容...

请输入评论/评论长度6~500个字

暂无评论

暂无评论