终于,在2022年上半年的最后一天,三星宣布3nm芯片量产,成为全球第一家量产3nm芯片的厂商,实现了三星的第一个小目标--领先台积电,兑现了自己的承诺。

同时三星也表示,3nm芯片相比于自己的5nm芯片,性能提升了23%,功耗降低了45%,芯片面积缩小了16%。

不得不说,这些数值也表现非常棒,特别是功耗降低45%,让下游的客户心动不已。毕竟当芯片进入到5nm之后,功耗大增,已经让厂商们头痛不已了。

特别是高通,自从芯片进入5nm之后,由于功耗太大,发热量也上升,于是骁龙888、骁龙8Gen1都获得了“火龙称号”。

如果3nm能够降低45%功耗,想必高通是最兴奋的厂商之一,因为“驯龙”有戏,“火龙”有救了啊。

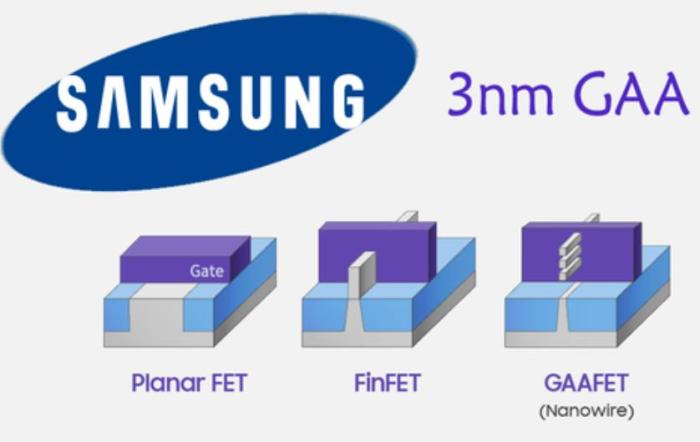

那么问题来了,为何三星的3nm工艺,能降低45%的功耗?原因在于三星采用了GAAFET晶体管技术,而之前从14-4nm,采用的是FinFET晶体管技术。

对于一颗芯片而言,功耗分为两个部分,一个部分是动态功耗,一部分是静态功耗(又称漏电功耗)。

动态功耗是指芯片进行计算时,本身的功耗。而静态功耗,则是芯片加上电之后,电流通过晶体管时,泄露的功耗。

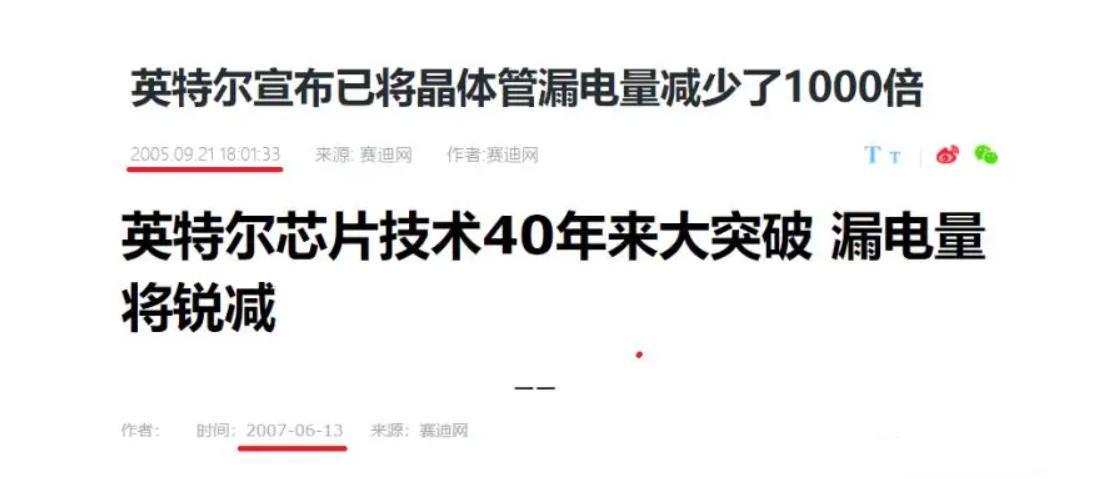

别小看静态功耗,静态功耗才是大头,占一颗芯片总功耗的60%以上,晶圆厂一直就在与静态功耗(漏电功耗)对作,比如英特尔,一直就在讲自己的漏电功功降低了。台积电之前有个“台漏电”的称号,也是讲这一块控制得不佳。

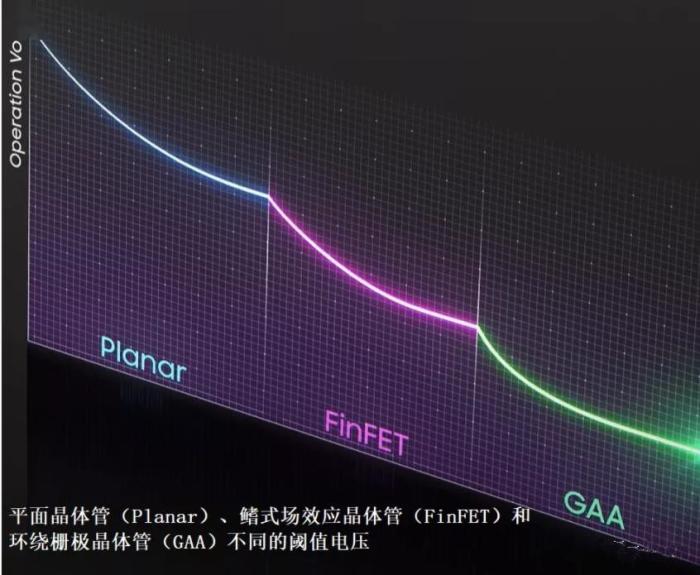

而使用GAAFET晶体管技术时,由于技术更先进,相比于FinFET技术,加到晶体管上的电压(阈值电压)变小了。大家回忆下初中物理知识,功率=电流X电压。

当电压变小时,是不是功耗就变小了?由于GAAFET相比FinFET的阈值电压要低30-50%,所以静态功耗理论上也就变小30-50%。

再加上3nm工艺更精细,在动态功耗上也会有降低,以及GAAFET晶体管技术,本身漏电情况也会稍好一点,所以最终实现了45%的功耗降低。

而三星还表示第二代 3 纳米 GAA 制造工艺也正在研发中第二代工艺将使芯片功耗降低达 50%,性能提高 30%,面积减少 35%。

可以说,三星的3nm工艺,比依然采用FinFET工艺的台积电3nm,真的是更有优势的。

考虑到当前台积电已经绑定了苹果、AMD等厂商,三星为了抢台积电的市场,这次是拥抱中国厂商了,据媒体报道称,上海磐矽半导体将成为最初的客户之一,另外还有更多的中国企业,可能会率先与三星合作3nm。

不知道接下来台积电如何应对,基于FinFET技术,本来就落后一些,现在时间又落后一些,台积电已经处于劣势了。

就看三星3nm的率良高不高了,如果良率高,表现好,这一把说不定真有翻身机会,就像当年三星在FinFET技术上,率先实现14nm一样。

分享

分享

发表评论

请输入评论内容...

请输入评论/评论长度6~500个字

暂无评论

暂无评论