7.30-8.1 全数会2025(第六届)机器人及智能工厂展

火热报名中>>

借助虚拟工艺加速工艺优化

物理结构变化的影响

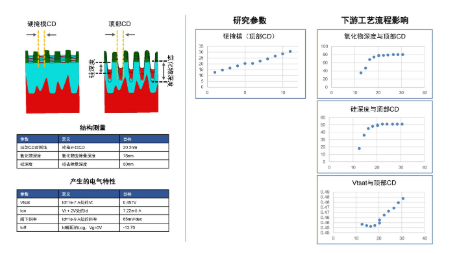

对由物理结构改变造成的影响的研究,首先需要检查标准模型中的参数的设定,包括硬掩模CD/顶部CD、硅深度和氧化物深度。SEMulator3D使用以上参数构建模型然后提取对应的器件电学参数(包括Vt、ION、IOFF和亚阈值摆幅)(图4,左侧)。

图4:研究标准模型(左侧)的物理结构变化的影响。使用SEMulator3D(右侧)进行的实验表明,氧化物深度和硅深度对CD变化的敏感性在20nm以上降低,而Vtsat敏感性在相同范围内增加。

本研究的目的是将图4中的硬掩模CD以2 nm的增量从12 nm变化至30 nm,同时监测其他结构参数,包括硅深度和氧化物刻蚀。此变化是通过更改流程早期工艺步骤来实现的,并且下游工艺步骤对模型更改的响应符合预测。

图4(右侧)显示,硬掩模CD变化对栅极刻蚀具有非线性响应。氧化物深度和顶部硅深度对较小CD的顶部CD很敏感,但在较大CD上趋于饱和。另一方面,当CD高于20 nm标准值时,Vtsat值显著增加。因此,SEMulator3D的指标揭示了对单个物理结构变化的各种响应,有利于工程师研究物理结构变化对所选参数造成的影响。

识别重要的工艺步骤

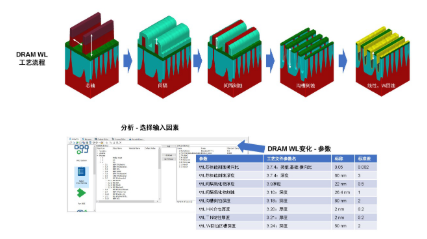

下一步DOE,包括蒙特卡罗变异性研究,以确定重要的工艺步骤(图5)。在参数变化研究中,采用了蒙特卡罗方法对DRAM字线 (WL) 深度进行变化。

图5:SEMulator3D利用数百甚至数千次DOE试验,使用回归分析来识别对特定指标有显著影响的关键工艺参数。

WL工艺参数值是通过基于平均值或标准值和标准差的高斯分布随机设置的。演示中选择了50个实验。然而,通常至少需要100个实验才能获得有意义的研究。

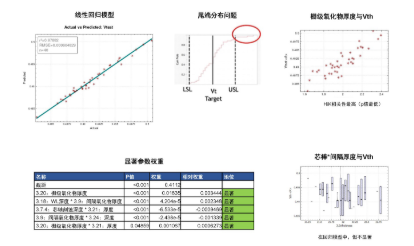

DOE的结果如图6所示。DOE运行时,阈值电压Vt在0.4837 V和0.5031 V之间变化。SEMulator3D的回归分析有助于识别对阈值电压影响显著的5个参数,这些参数的p值小于0.5,不支持原假设。注意,第一个参数(截距)被排除在本讨论之外,因为它始终是列表的一部分。

图6:工程师可以在SEMulator3D中分析任何量测结果,以识别重要参数,极端情况如上图所示(红色圈出)。

有待进一步研究的五个最重要的因素是:

●栅极介电层厚度(最重要的参数)

●字线刻蚀深度和侧墙厚度的交叉项

●芯轴刻蚀深度和栅极厚度的交叉项

●间隔氧化物厚度和抛光深度的交叉项,以及

●栅极介电厚度和侧墙厚度的交叉项。

线性回归曲线的R方值 (r2) 为0.97882,说明模型与数据吻合较好。栅极氧化层厚度与Vth图显示出很强的相关性,而芯棒间隔厚度与Vth图则没有相关性,因此可以认为它不是一个重要参数。

DOE的结果还可以帮助识别一些特殊情况,例如规格下限 (LSL) 到规格上限 (USL) 范围之外的Vth,使工程师可以仔细检查况并找到造成这种结果的工艺条件。

工艺优化

为了从不同的角度进行优化,我们可以将电学性能作为研究的目标。可以使用电学性能参数目标值作为工艺步骤优化的目标。每个工艺步骤参数都可以改变,以寻找满足电气性能的条件。

根据所使用的制造设备,在软件中定义了每个刻蚀行为的允许范围。因此,可以根据材料的刻蚀选择比、横向比、聚合/锥度、溅射和离子通量分布等参数来定义刻蚀行为。利用DOE确定的重要输入参数,输入电学性能指标。

SEMulator3D采用直接优化的方法,以确定WL刻蚀工艺中最佳刻蚀步骤行为的工艺参数,以满足电学性能目标。校准工艺建议包括氧化层,硅和氮化层的刻蚀选择比、氧化层和硅的刻蚀角度和选择比等参数。

根据这些结果,可以通过工艺研究验证是否存在满足条件的电学性能,或者在此范围内是否无法实现特定的电学性能。

虚拟工艺节省了成本和时间

由于工艺假设是在开发早期甚至在硬件实现之前完成的,因此虚拟工艺无需制造真正的晶圆,即可验证这些假设,节省了时间和费用。

该DRAM案例研究表明,通过在虚拟环境中执行大量的DOE和工艺变化研究,可以消除不相关DOE路径的时间和成本,并快速实现性能和良率目标,从而加快产品上市时间。

图片新闻

技术文库

最新活动更多

-

3月27日立即报名>> 【工程师系列】汽车电子技术在线大会

-

在线会议观看回放>>> AI加速卡中村田的技术创新与趋势探讨

-

4月30日立即参与 >> 【白皮书】研华机器视觉项目召集令

-

5月15-17日立即预约>> 【线下巡回】2025年STM32峰会

-

即日-5.15立即报名>>> 【在线会议】安森美Hyperlux™ ID系列引领iToF技术革新

-

5月15日立即下载>> 【白皮书】精确和高效地表征3000V/20A功率器件应用指南

推荐专题

分享

分享

发表评论

请输入评论内容...

请输入评论/评论长度6~500个字

暂无评论

暂无评论