7.30-8.1 全数会2025(第六届)机器人及智能工厂展

火热报名中>>

半导体的3D时代

每年在SPIE高级光刻会议召开之前的星期日,尼康都会举行其Litho Vision研讨会。我有幸连续第三年受邀发言,不幸的是,由于新冠肺炎的影响,该活动不得不取消。但是到活动宣布取消时,我已经完成了演讲文稿,所以在此分享。

概述

我演讲的题目是“ Economics in the 3D Era”。在演讲中,我将讨论三个主要的行业领域,即3D NAND,逻辑和DRAM。对于每个部分,我都会讨论当前的状态,然后进入技术,掩模数量,密度和成本预测的各自路线图。所有状态和预测都将针对公司,并涵盖每个细分市场的领导者。此演示文稿的所有数据,技术,密度,掩模数量和成本预测均来自我们的 IC Knowledge–战略成本和价格模型– 2020 –修订版00模型。该模型基本上是一份详细的行业路线图,可以模拟成本,设备和材料要求。

3D NAND

3D NAND是业界最“ 3D”的细分市场,其层堆叠技术可通过在竖直方向上添加层来提高密度。

图1展示了3D NAND TCAT制程。

图1. 3D NAND TCAT制程。

在3D NAND领域,市场领导者是三星,他们使用的是TCAT制程。市场上排名第二的是Kioxia(前身为Toshiba Memory),他们使用的工艺与三星基本相同。美光也正在采用电荷陷阱技术,我们希望其工艺类似于TCAT制程,从而使TCAT制程能够代表行业大多数。SK海力士使用不同的制程,但在许多关键要素上与TCAT制程相同。唯一不使用电荷陷阱技术的公司是英特尔美光公司,但由于英特尔和美光已经在3D NAND领域分道扬,,英特尔将是唯一一家仍然采用浮栅技术的公司。

TCAT制程包括三个主要部分:

制作CMOS – 这些CMOS用于写入,读取和擦除比特信息。最初,除英特尔-美光公司外,每家公司都在存储器阵列外围制造CMOS,而英特尔-美光公司在存储器阵列下方制造一些CMOS。随着时间的流逝,其他公司已经迁移到阵列下的CMOS,我们希望在几代之内,所有公司都将迁移到阵列下的CMOS,因为它提供了更好的裸片面积利用率。

制作存储阵列–对于电荷陷阱技术,可通过沉积氧化物和氮化物的交替层来进行阵列制造。然后向下蚀刻穿过各层的沟道孔,并重新填充氧化硅/氮化硅/氧化硅(ONO)层,多晶硅管(沟道)并填充氧化物。然后使用光刻-蚀刻-收缩-蚀刻方法制造阶梯。然后穿过阵列向下蚀刻狭隙,并蚀刻掉氮化物膜。然后沉积阻挡层和钨以填充蚀刻氮化物的水平开口。最后,将通孔蚀刻停止到到钨的水平片上。

互连– CMOS和存储器阵列然后互连。对于阵列下的CMOS,一些互连发生在存储器阵列制造之前。

这种技术掩模使用效率非常高,因为可以用若干张掩模对很多层进行构图。整个制程只需要一张沟道孔掩模,若干张阶梯掩模(取决于层数和制程需求)。在早期的工艺中,单张掩模可以制作大约8层,但是如今某些工艺可以通过单张掩模做到32层。狭缝(slot)蚀刻需要一张掩模,有时还有另一个浅狭缝需要一张掩模,最后接触通孔也需要一张掩模。

沟道孔蚀刻是非常难的高深宽比(HAR)蚀刻,一旦达到一定的最大层数,该制程就必须以所谓的“串堆叠”(string stacking)方式分成多个“串”(存储单元串)。基本上,在串堆叠中,沉积一组层,应用掩模,蚀刻,填充沟道。然后沉积另一组层,光刻,蚀刻和填充。理论上,这可以循环很多次。英特尔-美光科技公司使用浮栅工艺,该工艺使用的氧化硅/多晶硅层比氧化硅/氮化硅层更难蚀刻,所以他们是最早使用串堆叠技术的。

图2展示了Intel-Micron串堆叠技术。

图2. Intel-Micron串堆叠制程。

每家公司都有自己的沟道孔蚀刻方法,并且在串堆叠方面有自己的限制。因为使用氧化多晶硅层,所以Intel-Micron通过堆叠2次32层的串制作了64层芯片,然后通过堆叠2次48层的串量产了96层芯片。英特尔已经发布了144层存储芯片,预计将是3次堆叠48层。SK Hynix到72层时开始串堆叠,Kioxia是96层开始堆叠(都是电荷陷阱技术,都是氧化硅/氮化硅层)。三星是最后一个串堆叠技术的支持者,他们量产了一款92层的单串芯片,并发布了一款128层的单串器件。

通过在一个单元中存储多个比特,也可以提高存储密度。NAND闪存已从单层单元(SLC)到2个比特的多层单元(MLC),再到3比特的三层单元(TLC),再到4比特的四层单元(QLC)。业界现在正准备推出5个比特的五层单元(PLC),甚至还有关于6比特的6层单元(HLC)的讨论。增加每个单元的比特数有助于提高密度,但收益却在降低,从SLC到MLC的比特数是2倍,从MLC到TLC的比特数是1.5x,TLC到QLC的比特数是1.33x,从QLC到PLC的比特数是1.25倍。如果业界达到了PLC,则接下来到HLC的比特数将只是1.20倍。

图3在左轴上显示了按年份和公司分类的串堆叠,在右轴上显示了每个单元的最大比特数。

图3.堆叠层数,每单元比特数。

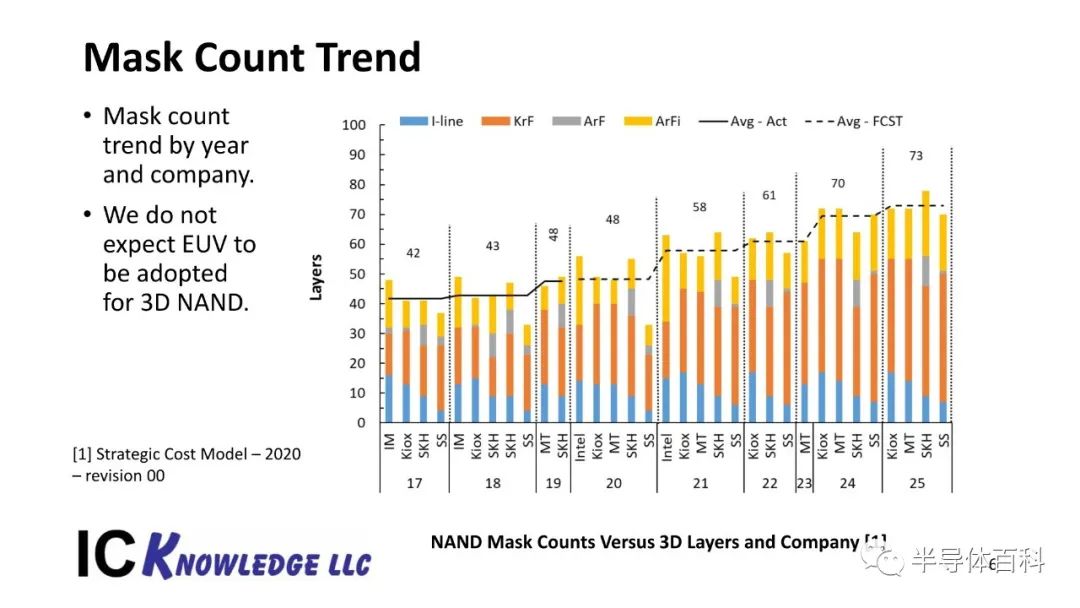

图4展示了我们对按曝光类型,公司和年份划分的掩模数量的分析。虚线是每年的平均掩模数,从2017年的42张增加到2025年的73张,这与层数从2017年的平均60个增加到2025年的512个相对应。换句话说,掩模数量仅增加1.7倍就增加了8.5倍的层数以突出3D NAND工艺的掩模使用效率。

图4.掩模数量趋势。

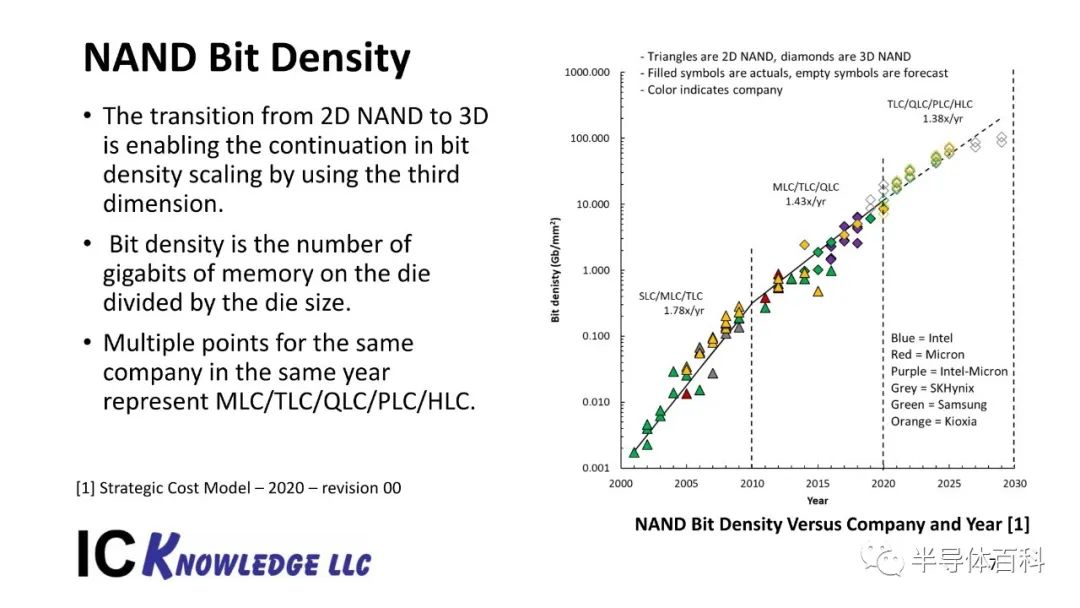

图5展示了各家公司2D NAND和3D NAND的实际和预测比特密度随年份变化的趋势。这里是整个芯片的比特密度,即芯片的容量除以芯片的尺寸。

图5. NAND比特密度。

从2000年到2010年,在光刻微缩的推动下,2D NAND比特密度每年增长1.78倍。大约在2010年左右,继续缩小2D NAND的难度导致增长减慢至1.43倍,直到2015年左右3D NAND成为驱动力并继续以每年1.43倍的速度增长。我们预计从2020年到2025年的年增长率将略有下降,为1.38倍。与去年相比,这是我们的预测的一项改进,因为我们看到这些公司推动该技术的速度超出了我们最初的预期。最后,SK海力士谈到了2025年的500层和2030年的800层,导致2025年之后的速度进一步放缓。

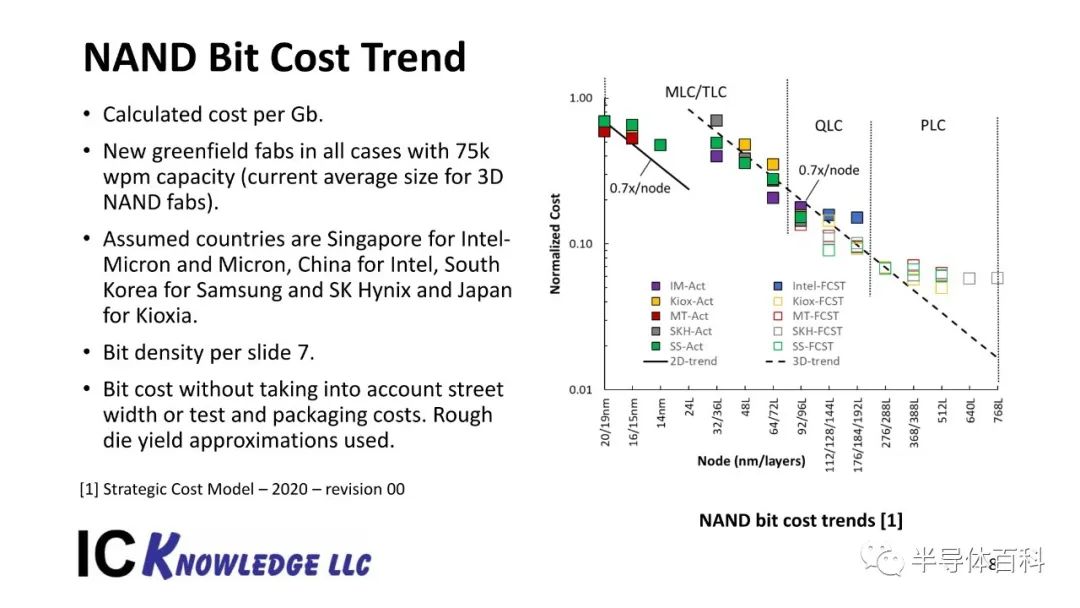

图6给出了NAND单位比特成本趋势。

图6. NAND单位比特成本。

在该图中,我们采用了使用战略成本和价格模型计算出的晶圆成本,并将其与图5中的位密度相结合以产生单位比特成本趋势。在所有情况下,这些晶圆厂都是新建的月产能75,000片晶圆的工厂,因为这是NAND晶圆厂在2020年的平均产能。这些晶圆厂对应所在的国家分别是新加坡-英特尔美光,英特尔-中国,Kioxia-日本,三星和SK海力士-韩国。这些计算不包括封装和测试成本,不考虑划片槽宽度,并且仅包含粗略的芯片良率假设。

图表中的前三个节点是2D NAND,每个节点的成本趋势为0.7倍。随着向3D NAND的过渡,大多数公司的比特成本最初都增加了,但现在已降至2D NAND比特成本以下,并且每个节点的趋势为0.7倍,直到大约300到400层。我们预计单位比特成本会趋于平缓,除非在工艺或设备效率方面取得一些突破,否则该技术将面临成本极限。

图片新闻

技术文库

最新活动更多

-

3月27日立即报名>> 【工程师系列】汽车电子技术在线大会

-

4月25日立即报名>> 【线下论坛】新唐科技2025新品发布会

-

在线会议观看回放>>> AI加速卡中村田的技术创新与趋势探讨

-

4月30日立即参与 >> 【白皮书】研华机器视觉项目召集令

-

即日-5.15立即报名>>> 【在线会议】安森美Hyperlux™ ID系列引领iToF技术革新

-

5月15日立即下载>> 【白皮书】精确和高效地表征3000V/20A功率器件应用指南

推荐专题

-

10 功率半导体,嗅到风险

分享

分享

发表评论

请输入评论内容...

请输入评论/评论长度6~500个字

暂无评论

暂无评论