堆叠

-

面向高性能的3D-IC芯片堆叠技术,如何普及?——技术现状、挑战与未来前景

芝能智芯出品 3D-IC(三维集成电路)技术作为芯片行业的一项突破性创新,近年来在数据中心和神经处理等领域展现了显著的进步。 通过将多个芯片垂直堆叠并通过高密度互连技术集成,3D-IC大幅提升了性能和能效,特别是在人工智能(AI)和大数据处理等高性能计算场景中

-

AMD芯片革命,多芯片堆叠技术

本文由半导体产业纵横(ID:ICVIEWS)编译自igorslab AMD芯片堆叠,革新未来处理器设计。 AMD 的一项新专利申请表明,该公司正计划将“多芯片堆叠”方法集成到其未来的处理器中

-

SK海力士突破300层技术大关,正式量产321层堆叠NAND闪存

(本篇文篇章共788字,阅读时间约2分钟) 2024年11月21日,韩国存储器巨头SK海力士宣布,已正式量产全球首款321层堆叠1Tb TLC 4D NAND闪存,标志着存储器行业又一项技术里程碑的诞生

-

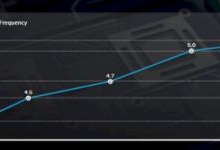

如何获得足够的 HBM,并将其堆叠的足够高?

本文由半导体产业纵横(ID:ICVIEWS)编译自nextplatform 任何新的内存方法都必须具备可制造性与成本效益,方能被采用。 业界可通过多种方式扩展计算引擎的内存容量与带宽,以更好地驱动人工智能(AI)和高性能计算(HPC)工作负载,但目前所能做到的仍有不足

-

英伟达的内存未来:一个GPU上堆叠20个DRAM芯片

本文由半导体产业纵横(ID:ICVIEWS)综合 堆叠更多的DRAM芯片,为GPU芯片带来更多助力。 据Trendforce 报道,内存制造商三星、SK 海力士和美光希望堆叠更多 DRAM 芯片

-

-

Pickering推出新的PXI多通道电池仿真模块 —— 仿真堆叠电压高达1000V

最新版本的PXI/PXIe 6通道300mA电池仿真模块提高了电压隔离能力,在BMS测试系统中,电池堆叠电压提高至1000V2023年4月19日,于英国Clacton-on-Sea。Pickering

-

中国首次商用芯片堆叠技术,成功破局,美国的图谋又一次破产了

中国芯片企业龙芯发布了全新的服务器芯片龙芯3D5000,值得注意的是这是国内首款采用了芯片堆叠技术的芯片,将两颗3C5000堆叠在一起推出了3D5000,性能提升一倍,满足了服务器芯片的要求。

-

-

让14nm秒变7nm?华为辟谣开发出芯片堆叠技术方案:假消息!

今天网络上有一份关于华为攻破堆叠芯片技术的聊天记录,引起了网友的关注。 其中显示,有人称华为搞定了堆叠方案,可以用14nm芯片堆叠成7nm水平,性能媲美的情况下,功耗也能优化下来。 甚至还附带了一份华为技术团队的官方通知

-

-

-

国产芯片将王者归来,以芯片堆叠技术实现5nm性能

近期深圳某科技企业悄悄地上线了麒零官方账号,似乎显示出它的芯片回归日期日益临近,2023年量产纯国产芯片似乎有望变成现实,此前该公司的高管已多次表示2023年王者归来,如今这些信息无疑得到印证。由于众

-

【专利情报】华为下注堆叠封装技术要在手机业务东山再起!

知情郎·专利情报|牛公司·新专利·前沿技术本期,专利情报栏目将解读华为的堆叠封装技术。华为最近又上了热搜头条,这次是因为芯片堆叠技术专利公布。近期,华为公布了3个芯片堆叠封装专利,向外界证明自己在手机市场仍有翻盘的希望!市场热议纷纷,看来华为不甘手机业务这般寂寞下去,还想东山再起

-

深度丨“3D堆叠”技术,半导体大厂继续深耕

前言:在用于个人电脑和高性能服务器的尖端半导体开发方面,3D堆叠技术的重要性正在提高。在通过缩小电路线宽提高集成度的微细化速度放缓的背景下,3D技术将承担半导体持续提高性能的作用。作者 | 方文图片来

-

华为芯片堆叠封装专利,到底是个啥?解决啥问题的?

众所周知,在华为的业绩发布会上,当时的轮值董事长郭平说,华为要采用面积换性能,用堆叠换性能的方式,来解决芯片问题,使不那么先进的芯片,也能够具有竞争力。而前两天,网上也被大家晒出了华为芯片堆叠封装专利图,可见采用堆叠换性能并不是乱说的,华为早就在做准备了

-

华为芯片堆叠封装专利公开!

近日,国家知识产权局官网公开的信息显示,华为技术有限公司公开了“一种芯片堆叠封装及终端设备”专利。据摘要显示,本公开涉及半导体技术领域,其能够在保证供电需求的同时,解决因采用硅通孔技术而导致的成本高的问题

-

具前瞻性的华为芯片堆叠专利被公开,提早布局的它或成为大赢家

国家专利局专利信息公开了一份华为的芯片相关专利,专利摘要显示,这是一种芯片堆叠封装及终端设备,申请时间在2019年9月30日,可能说明它很早就已预见到芯片制造工艺开发将遇到瓶颈,为此以芯片堆叠技术开辟提升芯片性能的新道路

-

ASML怎么看?佳能研发新型3D光刻机,堆叠光刻,或明年面市

众所周知,目前全球最牛的光刻机厂商是ASML,并且全球仅有它能够研发EUV光刻机,用于7nm及以下的芯片。而像佳能、尼康、上海微电子的光刻机,均无法支持7nm及以下的芯片制造,更多的只能用于中、低档的晶圆制造

-

华为用堆叠、面积增大解决芯片问题背后:6块14nm才顶一块5nm

众所周知,在华为2021年财报发布会上,华为轮值董事长郭平公开表示:“华为未来将推进三个重构,用堆叠、面积换性能,用不那么先进的工艺也可以让华为的产品有竞争力”。从这句表述中,大家可以看到,华为其实想

-

华为正式确认芯片堆叠技术,余承东所言王者归来或许快了

华为之前传出的双芯堆叠技术已被各方热议许久,如今正式得到了华为的确认,这或许意味着华为以双芯堆叠技术设计的芯片即将投产,随着芯片的问题得到解决,或许它真的即将王者归来了。在昨日华为的2021年年度业绩

-

索尼全球首发双层晶体管堆叠式CIS技术

①索尼全球首发双层晶体管堆叠式CIS技术索尼半导体解决方案宣布其已成功开发出全球首个双层晶体管像素堆叠式CIS技术。新技术让光电二极管分别置于不同的基片层。使独立优化光电二极管和像素晶体管架构成为了可

-

全球首款,阿里达摩院成功研发基于 DRAM 的 3D 键合堆叠存算一体芯片

12 月 3 日消息,据阿里云官方微信公众号发布,阿里达摩院成功研发出存算一体芯片。这是全球首款基于 DRAM 的 3D 键合堆叠存算一体芯片。该芯片突破了冯?诺依曼架构的性能瓶颈,满足人工智能等场景对高带宽、高容量内存和极致算力的需求

-

泛林集团首席技术官Rick Gottscho博士:下一代芯片在堆叠、微缩和检验方面的挑战

泛林集团首席技术官Rick Gottscho博士接受了行业媒体Semiconductor Engineering (SE)的专访。

-

3级电子产品PCBA片式元器件堆叠安装分析

一、概述不能片面引用IPC标准为军用电子产品电子装联的质量判据,尤其是航天产品中不能简单地引用IPC标准。IPC标准与MIL标准之间存在一定的差距,不属于同一个档次,对于军用电子产品,尤其是航天电子产品,如果IPC标准中的规定符合MIL标准规定的,我们可以采纳,如果低于MIL标准规定的,则必须抛弃

PCBA片式元器件 2020-04-11 -

灵活高效之上,英特尔先进技术封装技术堆叠无限可能

在今年7月,英特尔推出了一系列全新封装基础工具,包括将EMIB和Foveros技术相结合的创新应用(Co-EMIB),全方位互连(ODI)技术,和全新裸片间接口(MDIO)技术。

-

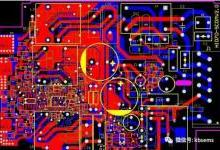

教你利用PCB分层堆叠控制EMI辐射

解决EMI问题的办法很多,现代的EMI抑制方法包括:利用EMI抑制涂层、选用合适的EMI抑制零配件和EMI仿真设计等。本文从最基本的PCB布板出发,讨论PCB分层堆叠在控制EMI辐射中的作用和设计技巧

-

不输魅族,VIVO APEX 2019正式发布,黑科技堆叠的概念机

昨天,魅族以最简陋的方式发布了全球首款无孔手机,将VIVO的热度抢走了不少。而今天VIVO也正式亮相了他们的首款无孔手机,虽然都是无孔但是实现的方式有所差异,不过此次VIVO还是给我们带来了一定的惊喜。

-

构建未来计算引擎,英特尔下注3D芯片堆叠技术

面临压力,英特尔能从现有工艺中释放出超乎想象的更高性能;而Foveros将在不久的将来为英特尔计算引擎的构建奠定基础。

-

力挺摩尔定律:英特尔开发出3D堆叠技术

近年来,“摩尔定律”被其他厂商唱衰,本该是芯片“鼻祖”的英特尔也在技术上渐渐落后于竞争对手。在此次的架构日,英特尔展示了他们的众多下一代技术和已经做出的创新,其中就包括业界首个3D堆叠逻辑芯片。

-

揭秘Find X:“量产概念机”背后,OPPO在设计、堆叠、制造上的一次重新思考

对于 OPPO 来说,这个过程也是对其自身能力的全面整合和提高。有了量产 Find X 的经验,我们有理由对 OPPO 未来的产品再增加几分期待。

-

耐用、多功能和可堆叠的高密度板对板连接器 满足工业环境的严格要求

Harwin全新的Archer Kontrol系列板对板连接器能够为设计工程师提供强大而灵活的互连解决方案,可满足范围广泛的不同工业应用的要求。这些紧凑型1.27mm间距连接器涵盖从12到80个触点引脚格式,每个触点的额定电流为1.2A。

-

缩放工艺日益困难 台积电独自开发3D芯片堆叠技术

台积电表示将尝试独自开发3D芯片堆叠技术,成为未来该技术产品的唯一供应商。此举对台积电而言具有商业意义,但一些无工厂芯片设计公司认为其缺乏技术水平,这也限制了他们的选择。

3D芯片堆叠技术 3D芯片 台积电 半导体缩放工艺 2011-12-14

最新活动更多 >

-

4月1日立即下载>> 【村田汽车】汽车E/E架构革新中,新智能座舱挑战的解决方案

-

4日10日立即报名>> OFweek 2025(第十四届)中国机器人产业大会

-

即日-4.22立即报名>> 【在线会议】汽车腐蚀及防护的多物理场仿真

-

4月25日立即报名>> 【线下论坛】新唐科技2025新品发布会

-

4月30日立即参与 >> 【白皮书】研华机器视觉项目召集令

-

限时免费下载立即下载 >>> 2024“机器人+”行业应用创新发展蓝皮书